纳芯微全新推出GaN相关产品NSD2621和NSG65N15K

2023-02-05

来源:纳芯微

纳芯微全新推出GaN相关产品,包含GaN驱动NSD2621与集成化的Power Stage产品NSG65N15K,均可广泛适用于快充、储能、服务器电源等多种GaN应用场景。

其中,NSD2621是一颗高压半桥栅极驱动芯片,专门用于驱动E−mode(增强型)GaN 开关管;NSG65N15K是一颗集成化的Power Stage产品,内部集成了高压半桥驱动器和两颗650V耐压的GaN开关管。

NSD2621产品特性:

01. SW引脚耐压±700V

02. 峰值驱动电流2A/-4A

03. 驱动输出集成内部稳压器,驱动电压5V/5.5V/6V可选

04. 传输延时典型值30ns,上下管驱动传输延时匹配低于10ns

05. 内部可调死区时间20ns~100ns

06. SW允许共模瞬变高达150V/ns

07. 独立的SGND和PGND引脚

08. 集成欠压保护和过温保护

09. 工作温度范围-40°C~125°C

10. QFN15 4*4mm封装

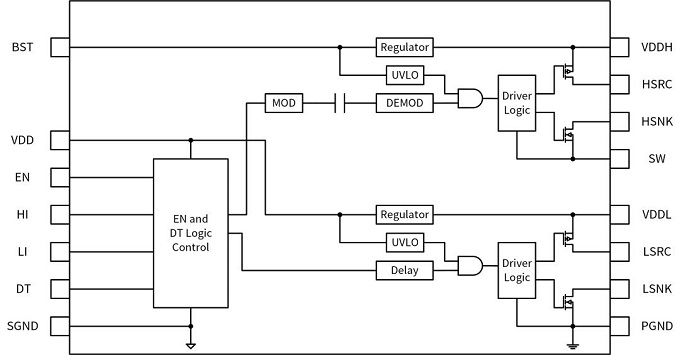

NSD2621功能框图

1. NSD2621将隔离技术应用于高压半桥驱动,解决了GaN应用桥臂中点SW引脚的共模瞬变和负压尖峰问题。

在GaN应用中,为了减小开关损耗,其开关速度远高于传统的Si MOSFET, 桥臂中点的dv/dt达到了50V/ns甚至更高,这对驱动芯片SW引脚的共模瞬变抗扰度提出了极高的要求。同时,高速开关导致的di/dt与寄生电感会在SW引脚产生瞬态负压尖峰,导致驱动芯片发生闩锁甚至损坏。

NSD2621的上管驱动采用隔离技术进行设计,共模瞬变抗扰度高达150V/ns,并且可以耐受700V的负压,有效提升了系统的可靠性。

2. NSD2621内部集成稳压器,有利于保持栅极驱动信号幅值稳定,保护GaN开关管栅级免受过压应力的影响。

与传统的Si MOSFET器件不同,E-mode GaN器件的栅源电压要求极为严格,一般耐压最大值不超过7V。在开关电源中由于系统噪声的影响,驱动芯片VDD或者BST引脚容易引入高频干扰,会引起栅极驱动电压的过冲,从而导致GaN开关管损坏。

NSD2621上下管的驱动输出都集成了内部稳压器LDO,可以有效抑制VDD或BST引入的高频干扰,避免损坏GaN开关管。此外NSD2621可以灵活地选择6V/5.5V/5V不同驱动电压版本,适用于各类品牌的GaN开关管器件。

3. NSD2621超短传输延时有利于减小GaN死区损耗,并且内置可调死区时间功能,可有效避免发生桥臂直通。

GaN器件可以反向导通,其反向导通特性代替了普通MOSFET体二极管的续流作用,但在负载电流较大时其较高的反向导通压降会造成较大损耗,降低了系统效率。为了减小GaN反向导通损耗,应设置尽可能小的死区时间。死区时间的设置除了与电源的拓扑结构、控制方式有关,还受到驱动芯片传输延时的限制。

传统的高压半桥驱动芯片的上管驱动需要采用电平移位设计,为减小功耗多采用脉冲锁存式电平转换器,造成传输延时较长,无法满足GaN 应用的需求。NSD2621上管驱动采用纳芯微擅长的隔离技术进行设计,传输延时典型值仅30ns,并且上下管驱动的传输延时匹配在10ns以内,能够实现对GaN开关管设置几十纳秒以内的死区时间。同时,NSD2621内置20ns~100ns可调的硬件死区时间,可以有效避免发生桥臂直通的情况。

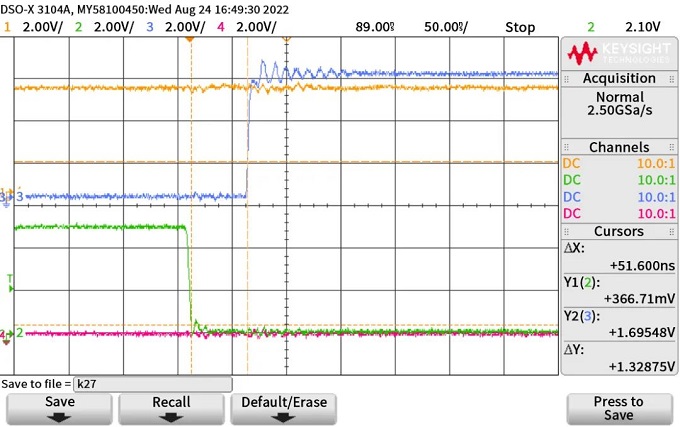

NSD2621内置死区时间测试波形

如上图所示,CH1为上管驱动输入 ,CH2为下管驱动输入,CH3为上管驱动输出,CH4为下管驱动输出。一开始当上管和下管驱动输入都为高电平时,为避免桥臂直通,上下管驱动输出都为低电平;当下管驱动输入变为低电平,经过30ns的传输延时和内置20ns的死区时间后,上管驱动输出变为高电平。

NSG65N15K产品特性

为进一步发挥GaN高频、高速的特性优势,纳芯微同时推出了集成化的Power Stage产品NSG65N15K,内部集成了半桥驱动器NSD2621和两颗耐压650V、导阻电阻150mΩ的GaN开关管,工作电流可达20A。NSG65N15K内部还集成了自举二极管,并且内置可调死区时间、欠压保护、过温保护功能,可以用于图腾柱PFC、ACF和LLC等半桥或全桥拓扑。

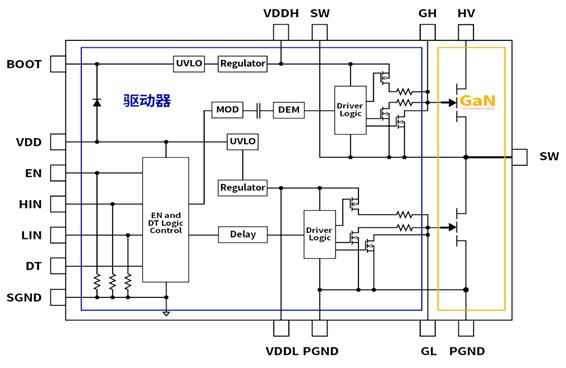

NSG65N15K功能框图

1. NSG65N15K用一颗器件取代驱动器和两颗开关管组成的半桥,有效减少元件数量和布板面积。

NSG65N15K是9*9mm的QFN封装,相比传统分立方案的两颗5*6mm DFN封装的GaN开关管加上一颗4*4mm QFN封装的高压半桥驱动,加上外围元件,总布板面积可以减小40%以上,从而有效提高电源的功率密度。同时,NSG65N15K的走线更方便PCB布局,有利于实现简洁快速的方案设计。

2. NSG65N15K的合封设计有助于减小驱动和开关管之间的寄生电感,简化系统设计并提高可靠性。

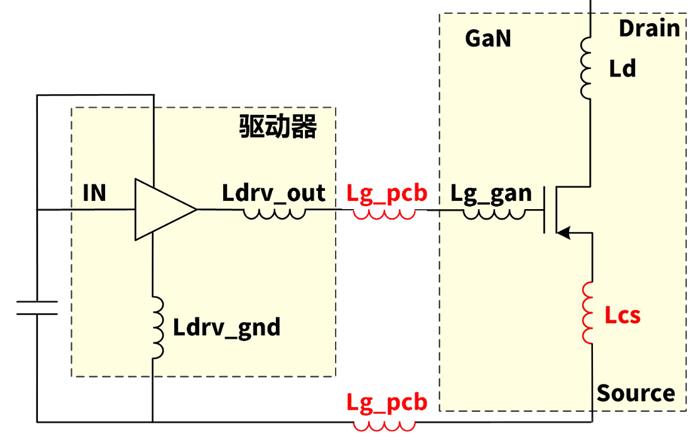

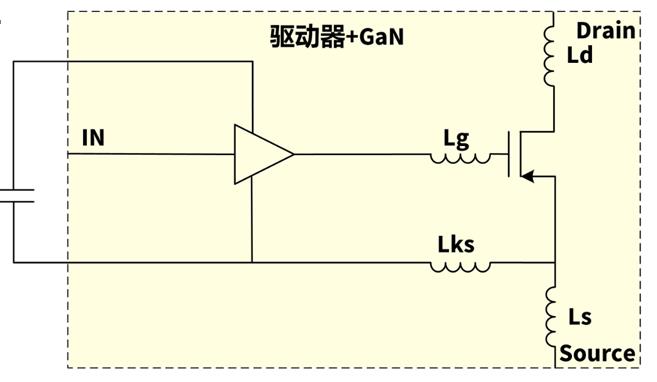

如下图所示,传统的分立器件方案,会引入由于PCB走线造成的栅极环路电感Lg_pcb和由于GaN内部打线造成的共源极电感Lcs。

传统分立方案引入寄生电感

其中,栅极环路电感Lg_pcb会在栅极电压开通或关断过程产生振铃,如果振铃超出GaN的栅源电压范围,容易造成栅极击穿;并且在上管开通过程中,高dv/dt产生的米勒电流会在下管的Lg_pcb上产生正向压降,有可能造成GaN的栅极电压大于开启电压,从而误导通。而共源极电感Lcs造成的影响,主要是会限制GaN电流的di/dt,增加额外的开关损耗;此外,在GaN开通过程电流增大,由于di/dt会在Lcs上产生正向压降,降低了GaN的实际栅极电压,增大了开通损耗。

NSG65N15K减小杂散电感的影响

如上图所示,NSG65N15K通过将驱动器和GaN合封在一起,消除了共源极电感Lcs,并且将栅极回路电感Lg也降到最小,避免了杂散电感的影响,可以有效地提高系统效率与可靠性。