1nm晶体管技术的新进展

2023-02-15

来源: 半导体行业观察

在1纳米或更小规格也能保持高导电性体的新材料TMDC

2023年2月,日本产业技术综合研究所 (AIST)与东京都立大学联合宣布,已经成功在二硫化钼 (MoS2) 上形成了层状材料三碲化二锑 (Sb2Te3),并 制造的 n 型 MoS2晶体管具有足够的耐热性以承受半导体制造过程。

一种称为过渡金属二硫化物(TMDC)的材料具有二维晶体结构,作为下一代晶体管沟道的半导体材料受到关注,因为它即使在 1 纳米或更小的原子层区域也能保持高导电性。然而,公共金属电极与MoS2界面之间的高接触电阻阻碍了晶体管性能的提升。

AIST正在参与日本科学技术厅的战略基础研究促进计划(CREST)“原子层异质结构器件的演示和3D集成LSI的原子层沉积工艺的开发(2017-2021财年):Metropolitan I一直在研究与大学的联合项目中的高性能 TMDC 晶体管。

这一次,研究小组使用 MoS2制造了晶体管,并专注于将Sb2Te3作为其接触材料。Sb2Te3有很多原子层,原子层通过称为范德华力的弱键结合在一起。它还表现出类似于半金属的特性(带隙为 0.2 至 0.3 eV),并且具有约 620°C 的高熔点。

这些特征表明在Sb2Te3和MoS2之间可能形成范德华界面以抑制费米能级钉扎(FLP)现象。因此,确定通过使用Sb2Te3,可以同时实现高耐热性和低接触电阻。

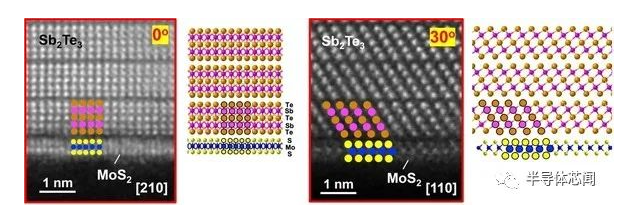

因此,这一次,使用溅射法在单层MoS2上形成Sb2Te3膜。然后,通过透射电子显微镜(TEM)确认在Sb2Te3/MoS2接触界面处形成了范德华界面。

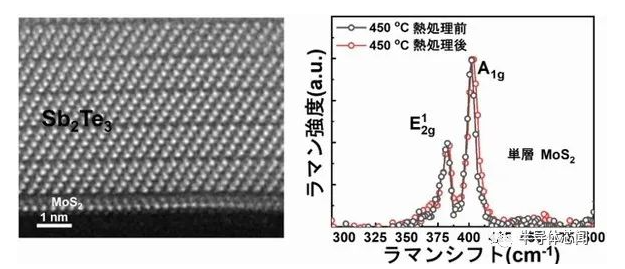

还研究了Sb2Te3/MoS2层压膜结构的耐热性。拉曼光谱分析证实,MoS2单层结构在热处理前后均保持不变。还证实,即使在 450°C 的热处理后,Sb2Te3/MoS2层压膜结构也保持良好的结晶度和范德华界面。

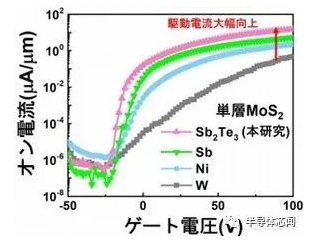

该研究小组还研究了Sb2Te3/MoS2范德瓦尔斯界面形成对晶体管特性的影响。结果发现,具有Sb2Te3电极的晶体管的驱动电流比使用Sb、Ni、W等作为接触材料时高4至30倍。事实上,当测量MoS2晶体管的接触电阻时,使用Sb2Te3电极的晶体管的接触电阻值比使用Sb电极的晶体管低约一个数量级。

未来,课题组将致力于p型TMDC晶体管的低接触电阻技术开发,旨在通过串联n型和p型TMDC晶体管来制造CMOS。

台积电将带来全球第一个2D纳米片晶体管

台积电工程师与台湾两所大学合作,将在今年的国际电子器件会议 (IEDM) 上报告世界上第一个由二维半导体材料制成的纳米片栅环晶体管。

硅纳米片晶体管或又名纳米带提供改进的静电控制和相对较高的驱动电流,并在 3nm 制造工艺中实施。

根据即将推出的 IEDM 计划的亮点,台积电已经展示了在纳米片晶体管中使用过渡金属二硫属化物单层作为半导体通道的可能性。在这种情况下,它是二硫化钼

与硅和自旋轨道耦合相比,这种二维材料可以具有增强的电子迁移率,从而产生自旋电子计算的可能性。

栅极宽度为 40nm 的晶体管在 1V 的 Vds 下产生每微米 410 微安的驱动电流。期望通过堆叠设备来增加驱动电流。

台积电领导的团队将报告制造此类晶体管的集成流程,但优化性能仍有待完成。

TSMC 论文#34.5首次展示 GAA 单层 MoS2 纳米片 nFET……是第 68 届年度 IEDM 的亮点之一。

在论文 #7.4 中,在 EOT 为 1 nm 的单层 MoS2 顶栅 nFET 中接近理想的亚阈值摆动中,台积电领导的团队描述了铪基电介质与 MoS2 的集成,以构建顶栅 nFET 创建可堆叠系统. 亚阈值电压摆幅小于70mV/dec。这表明当晶体管关闭时泄漏电流较低。

1纳米以下制程重大突破!台积电官宣「铋」密武器

IBM 刚刚官宣研发2nm芯片不久,台积电再次发起了挑战! 台积电取得1nm以下制程重大突破,不断地挑战着物理极限。 近日,台大与台积电、美国麻省理工学院合作研究发现二维材料结合「半金属铋(Bi)」能达极低电阻,接近量子极限。 这项研究成果由台大电机系暨光电所教授吴志毅,与台湾积体电路和MIT研究团队共同完成,已在国际期刊Nature上发表,有助实现半导体1nm以下制程挑战。

目前半导体主流制程进展到5nm和3nm节点。 晶片单位面积能容纳的电晶体数目,已将逼近半导体主流材料「硅」的物理极限,晶片效能也无法再逐年显著提升。 近年科学界积极寻找能取代硅的二维材料,挑战1nm以下的制程,却苦于无法解决二维材料高电阻及低电流等问题。 台大、台积电和MIT自2019年展开了长达1年半的跨国合作,终于找到了这把key。

这个重大突破先由MIT团队发现在「二维材料」上搭配「半金属铋(Bi)」的电极,能大幅降低电阻并提高传输电流。 台积电技术研究部门则将「铋(Bi)沉积制程」进行优化,最后台大团队运用「氦离子束微影系统」将元件通道成功缩小至纳米尺寸,终于获得突破性的研究成果。 吴志毅教授说明,在使用「铋(Bi)」为「接触电极」的关键结构后,二维材料电晶体的效能,不但与「硅基半导体」相当,又有潜力与目前主流的硅基制程技术相容,有助于未来突破「摩尔定律」极限。

研究成果能替下世代晶片,提供省电、高速等绝佳条件,未来可望投入人工智能、电动车、疾病预测等新兴科技应用。

敬请关注电子技术应用2023年2月22日==>>商业航天研讨会<<