中文引用格式: 李祉怡,孙航,丁学伟,等. Virtuoso iQuantus Insight及Quantus Insight流程在FINFET先进工艺项目中加速后仿迭代的应用[J]. 电子技术应用,2024,50(8):26-31.

英文引用格式: Li Zhiyi,Sun Hang,Ding Xuewei,et al. Application of Virtuoso iQuantus Insight and Quantus Insight Flow on FINFET advance processes to accelerate post-simulation iteration[J]. Application of Electronic Technique,2024,50(8):26-31.

引言

半导体技术不断发展,随着集成度的提高,工艺节点不断缩小,越来越多的设计进入了7 nm、5 nm甚至更低的节点,制造难度的成倍增长导致设计规则检查(Design Rule Chek, DRC)越发复杂,寄生效应对集成电路设计性能的影响日益深远。为考虑寄生效应对性能的影响,电路工程师会在设计中加上预设的寄生电阻电容进行前仿验证。然而版图中复杂的寄生通路使得从版图设计提取得到的寄生网表中包含大量寄生RC参数,这些寄生RC与电路中预设的值往往存在不小的差距,复杂的寄生RC网络使版图设计后仿真的性能结果无法达到电路前仿预期的结果。

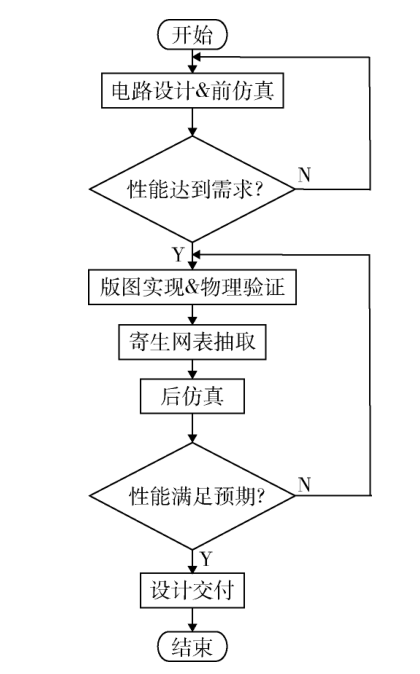

基于这一现状,在从模拟电路设计到最终的设计交付过程中(如图1所示),需要进行多次迭代,根据版图设计后仿结果与电路设计前仿预期之间的差异,不断修改电路设计、调整版图并再次进行后仿,以逐步缩小前后仿差异,最终得到满足性能要求的设计。

图1 模拟电路设计流程图

从图1中可见,当后仿真得到的性能指标不满足预期时,需要对版图进行修改或者对电路设计进行修改,在这一步修改过程中,分析寄生网表中的寄生电阻电容数值能够为修改提供指导,对寄生电阻电容的分析越清晰,电路及版图设计的迭代修改就更加有的放矢,迭代效率更高。因此如何对版图寄生网表进行分析以快速定位问题在集成电路设计迭代过程中至关重要。

本文将讨论如何使用Cadence公司的Virtuoso iQuantus Insight (ViQI)/Quantus Insight (QI)工具对版图寄生网表中的寄生电阻、寄生电容进行分析,直观地查看关键信号路径上的寄生数值是否满足预期,了解寄生电阻、电容在各金属层的分布情况并在版图中对应位置上显示,帮助设计师快速找到薄弱点,同时可通过寄生假设(What-if)功能对薄弱点寄生进行修改,确保电路设计及版图设计可进行针对性的快速迭代。

本文详细内容请下载:

http://www.chinaaet.com/resource/share/2000006117

作者信息:

李祉怡1,2,孙航1,2,丁学伟1,2,张慧丽3,曾义3

(1.深圳市中兴微电子技术有限公司,广东 深圳 518055;

2.移动网络和移动多媒体技术国家重点实验室,广东 深圳 518055;

3.上海楷登电子科技有限公司,上海200120)