随着电子技术、计算机应用技术和EDA技术的不断发展,利用FPGA进行数字系统的开发已被广泛应用于通信、航天、医疗电子、工业控制等领域,FPGA成为当今硬件设计的首选方式之一。PC/104是一种专门为嵌入式控制而定义的工业控制总线,以其独特的堆栈式结构、低功率等优点,得到了广泛的应用。作为主流的现场总线,工业控制局域网CAN(Controller Area Network)总线抗干扰能力强,易于组网,具有非常广阔的应用前景。独特的PC/104总线与CAN总线的结合,进一步拓宽了CAN总线的应用领域。

1基于FPGA的CAN核设计

本设计采用了Altera公司的Cyclone III系列FPGA EP3C25,开发平台采用了Altera公司的Quartus II软件。CAN核的设计以SJA1000功能结构为基础。

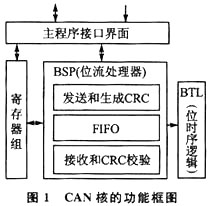

CAN核的功能框图如图1所示。该CAN总线控制器IP核,遵循CANbus 2.0标准,其功能和寄存器操作与SJA1000兼容。IP核采用VHDL编码,并采用容错设计,可抑制存储性器件的数据位翻转,大大提高了IP核的可靠性。CAN核可在FPGA中实现,也可以实现为ASIC。其中包含3个主要模块:寄存器组(can_registers),位时序逻辑(can_btl),位流处理器(can_bsp)。

寄存器组(CAN Register):外部微处理器可以通过地址直接访问这些寄存器。发送数据时,微处理器将要发送的数据写入发送缓冲器,置位命令寄存器的发送请求位来启动发送。接收到数据后,核心控制器将其存在接收缓冲器,并通知位控制器将其取走。同时,CAN寄存器中还有1个64字节的接收FIFO,可以1次存储至少2个数据帧。

位时序逻辑(BTL):用来监视CAN总线并处理与CAN总线相关的位时序。在消息的开始处,当位时序逻辑检测到总线上由隐性位(recessive)到显性位(dominant)的跳变时,就会将其内部逻辑同步到位流,称之为硬同步;随后,在接收消息的过程中,检测到隐性位到显性位的跳变时,便会重同步到位流,称之为软同步。位时序逻辑还要根据总线定时寄存器0和总线定时寄存器1的值来决定每个位周期采样点的位置,以补偿传输延迟和相位漂移所造成的误差;同时,根据总线定时寄存器1的设置采取相应的采样模式(单次采样或3次)对总线上的数据采样。

位流处理器(BSP):根据其实现的功能分为3个模块:数据接收模块、数据发送模块和错误处理模块。数据接收模块将从位时序逻辑送过来的采样数据去除位填充后送到移位寄存器进行串并转换,之后对并行数据进行CRC校验,在消息接收完时发送应答信号,表示接收无误。最后将接收到的消息的特征码与验收屏蔽寄存器的内容进行比较,以决定是否将接收的消息写入接收FIFO。数据接收模块将要发送的数据组成帧并进行CRC计算,之后送入移位寄存器进行并串转换,然后将串行数据编码(位填充)后送到总线上。错误监视模块根据协议规范中描述的错误监视机制检测系统错误,并设置相应的寄存器,通知设备控制器。模块根据协议描述的12种错误监视规则,在适当情况下对计数器进行加、减或清除。控制器根据这两个计数器的值以及错误限制寄存器的值来决定自己的故障状态:错误激活(Error Active),错误认可(Error Passire)或总线关闭(Bus off On)。

2硬件电路设计

根据系统的总体设计方案,因为现有的CAN总线收发器最大的工作频率为1 MHz,在提高CAN的通信速度后,现有的CAN总线收发器就不能满足需要了,因此改用RS485收发器。由于RS485收发器是差分传输,不能完成通信卡的自发自收功能,因此需要外置的CAN Hub。另外,要进行光纤传输,要完成光的逻辑总线结构,也需要外置Hub。因此,本硬件设计分为CAN通信板的设计和CAN Hub的设计两部分。

(1)CAN通信板硬件电路设计

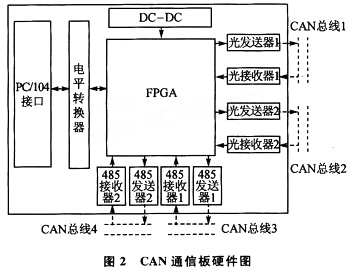

CAN通信板的核心器件是FPGA,同时完成“双光双电”通信,硬件通信板结构如图2所示。

作为PC/104系统的模块,要接在PC/104总线上,所以要在数据、地址、控制总线上与PC/104标准规定的总线标准一致。

本设计要进行四冗余设计,在设计中要添加4个CAN核,选用Altera公司Cyclone II系列的FPGA EP3C25。

由于PC/104的工作电压为5 V,而FPGA的工作电压为3.3 V,因此在PC/104和FPGA之间要加入1个电平转换器74LVC245来保护FPGA。

(2)光收发电路

本系统的高速光发射器采用HFBR-1414低功耗高速光发射器件,其光发射波长为820 nm。此发射器能够与以下4种光纤配合使用:50/125 μm、62.5/125 μm、100/140 μm、200 μm(HCS)。HFBR-1414采用了双镜片的光学系统,光发射效率高,当驱动电流为60 mA时,在50/125 μm光纤上可得到-15 dBm的光功率。光接收器采用HFBR-2412,其内部集成了光电二极管、直流电路和开集电极的肖特基晶体管。HFBR-2412光接收器能与光发射器HFBR-1414及50/125 μm、62.5/125 μm、100/140 μm、200 μm(HCS)的光纤配合使用,最高通信速率可达5 MB。由于采用了开集电极电路,此接收器兼容TTL及CMOS电平。该电路的通信距离最远可达1.7 km。

为提高CAN通信板的抗震性,抗干扰性等综合性能,采用了双面布线设计。该通信板尺寸规格严格按照PC/104板的要求做。

(3)冗余设计及CAN Hub设计

该通信板设计了4路冗余,工作时只有1路CAN通道进行工作,采用高位片选的方式进行工作通道的选择,其片选模块在FPGA内部设计完成。

(4)GAN Hub的设计

由于本系统采用“双光双电”四冗余的电路设计,为提高通信速度,采用485收发器代替标准的CAN收发器。光是“点对点”的传输,485收发器是差分传输,在形式上都无法构成总线式结构。因此,引入CAN Hub来对信号进行处理,在逻辑上达到总线式的结构。

3软件设计

CAN通信板的正常工作离不开强大的软件支持,本系统中控制部分的核心采用PC/104嵌入式计算机系统。PC/104嵌入式计算机拥有可以和PC机媲美的强大功能,CAN通信板软件部分的开发和设计就是在PC/104计算机上完成的,采用C语言进行设计。C语言具有通用性、高效性和实时性,能满足仪器的实时性要求。在设计过程中采用了模块化、结构化的设计方法,把软件按功能分成若干个模块,这些模块既有一定的独立性,又有一定联系。每个模块的编制要求相对独立,以便对各模块进行检验调试和修改、维护。这种框架模式的程序可以保证良好的通用性、可维护性、可扩展性、移植性、互换性和独立性。

由于CAN核的内部结构和SJA1000一样,因此,开发时就像面对SJA1000一样,编写起来简单方便。本设计采用中断处理的方式来进行任务的处理。在中断到来后进行相应的处理就可以了。

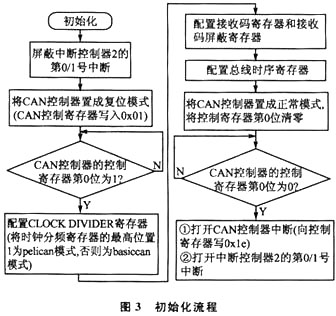

通信板初始化流程如图3所示。

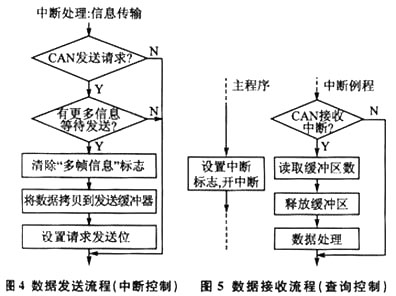

数据发送流程如图4所示,数据接收流程如图5所示。

4系统的仿真

采用Modelsim进行仿真。

系统的测试平台(TestBench),例化了模块can4core和1个CAN核cantop,并仿真它们之间的通信。

本仿真完全按照CAN核正常工作过程进行,仿真过程如下:

①初始化设置。首先进行时间寄存器的设置和数据格式的设置。通过平台对本系统设计模块和CAN核进行设置。

②同步测试。包括硬同步测试和重新同步测试。一个硬同步后,内部的位时间以同步段重新开始。硬同步使引起硬同步的跳变沿位于重新开始的位时间同步段之内。

③空FIFO测试(test_empty_fifo_ext)。该测试通过接收2个数据帧,然后读取接收缓冲器,接着清空缓冲器,再读取缓冲器,反复清空和读取,看FIFO中的数据是否被完全清除。

④满FIFO测试(test_full_fifo_ext)。首先清空寄存器,然后通过不断地接收数据帧来填满FIFO并读取信息,检测是否能正常工作。

⑤总线空闲测试(bus-off-test)。通过不断发送数据来使总线处于忙状态,致使总线产生错误,测试中断寄存器是否能检测到错误,以及错误清除后CAN核能否继续正常工作。

⑥Basic CAN模式发送帧检测。测试CAN核能否正常发送帧。

⑦寄存器测试。通过不停地读写寄存器,检测CAN核寄存器是否正常工作。

⑧总线上数据的传输。仿真过程中重要的一点就是总线上是否能够正常传输数据信息。

经过仿真可以看到该CAN通信板突破了SJA1000在速度方面的限制,传输速度可达2 MHz,有效传输速率得到了大幅提高,工作性能良好。

结语

本文设计的CAN总线通信板完成了PC/104与CAN总线的通信转换,改变了传统的应用CAN控制器加外部控制器的设计方法,在设计CAN核的基础上,将通信板中所有数字信号处理部分都放在FPGA内部来实现,使通信速度得到很大提高。无论是在传输速率还是在抗干扰、抗震性等方面,CAN核应用的综合性能都得到了很大的提高。