基于RVM的可重用性SoC测试平台设计

2008-05-29

作者:张旭峰, 杨丰瑞, 郑建宏

摘 要: 简要介绍了一种基于事务的用于SoC系统芯片验证的RVM验证方法" title="验证方法">验证方法学,以及应用该方法学搭建的具有分层结构的测试平台" title="测试平台">测试平台,该测试平台具有良好的可重用性" title="可重用性">可重用性。为了对该方法进行示范,验证了TD-SCDMA手机芯片中的I2C模块的RTL级实现,并给出了相应的测试平台模型及其在系统级" title="系统级">系统级上的重用。

关键词: RVM 可重用性测试平台 基于事务的验证 寄存器传输级验证

随着芯片复杂度的上升,验证工作的复杂度和工作量呈指数形式上升。芯片系统要想尽快推向市场,验证已经成为极其重要的一环,甚至是最重要的一环,这就迫使系统芯片验证工程师要尽可能多地重用已有的验证资源。和设计重用类似,验证的重用可以大大提高验证的效率,减小验证代价,得到高质量的设计。

本文介绍的Synopsys的RVM(Reference Verification Methodology)验证方法学,是采用Vera硬件验证语言建立目标模型环境、激励自动生成、含错误指示的自核对式测试、覆盖状况分析能力[1]。通过简化问题和建立复杂的测试平台,为验证工程师提供了更高的设计生产率,并使测试平台具有良好的可重用性。

1 搭建可重用测试平台的关键技术

在传统验证方法的许多情况下,测试平台是在信号级(Signal Level)的接口上直接与可验证性" title="可验证性">可验证性设计(Design Under Test,DUT)相通信的,即使用激励直接驱动DUT的引脚,并通过检查接口信号的值和变化,达到验证设计功能的目的。这种验证方法的抽象层次较低,平台的开发与设计的接口协议紧密相关,从而使得测试平台的重用变得十分困难。所以测试平台要想在不同的项目之间重复使用,至少是部分重用,首先测试平台的结构要被有效地模块化,使得构成平台的各个模块的改变和重用变得容易;其次测试平台必须有明确的层次化定义,并要清晰地定义层和层之间的接口,使得各层之间具有一定的独立性,改变底层并不会影响上层的重用[2]。

基于上述考虑,在验证过程中提出了基于事务的验证思想[3]。基于事务的验证:可以在一个更高的层次上进行验证,可以明显地减少测试工作量,简化调试,并有助于统计测量功能覆盖率。所谓事务[4](Transaction)是指设计对象与事务处理器(Transactor)之间通过接口所做的一次数据或控制的传输。事务可以是一个简单事务,如读取某个存储器单元,也可以是一个复杂事务,如传输整个结构式数据报文;同时可以把单独信号的特殊性、比特和字节的繁琐性都模型化并且包装起来,这样把验证提高到更高的抽象的层次上,这个层就是事务层,这样能够更有效地完成更多的功能。具体在RTL级的验证中,可以设计一个用户定义的事务处理器[5],将可验证性设计(DUT)与所构建的测试平台连接起来,其中用户定义的事务处理器能够将事务级的测试激励与RTL级的信号(Singal)进行相互转换。

基于事务的验证工具让验证工程师除了可以在信号/引脚级上进行验证,还可以在事务级上进行验证,从而提高了验证工程师的设计效率,同时验证的模块化也大大地提高了验证的可重用性。

2 RVM验证方法学

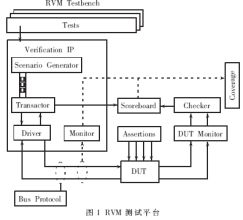

RVM验证方法学主要是基于事务验证的思想,结合随机化验证和覆盖率驱动技术,帮助验证工程师快速建立一个可重用的验证环境。RVM采用了易于验证重用的分层测试平台结构,同时它还具有全面的采用面向对象技术的库,从而使RVM验证环境模块化、实用化。从基于事务验证思想的角度来分析,RVM可以分为三层:信号层、事务层和测试层。RVM测试平台结构如图1[6]所示。

其中,信号层是与被测设计对象(DUT)直接联系的,主要起到事务层和DUT连通的作用。事务层则包括了Scenario Generator、Driver、Monitor、Transactor、Scoreboard和Checker,它将根据上层测试层的请求,将测试层协议映射到信号层。测试层(Tests)用于在系统中协调事务层的处理。

RVM的分层结构使验证的抽象层次从信号层提升到了事务层,很好地利用了事务级验证的思想。这样验证工程师就可以不用太关心DUT内部的具体实现过程,只需根据设计工程师提供的设计文档,提取出DUT工作所需的激励和输入输出的端口信息以及相应的时序关系,就可以进行测试平台的设计和验证代码的编写工作了,设计出的测试平台具有明显的模块化特征,易于重用。

为了更好地构建RVM验证环境,完成层与层之间的通讯,RVM还可以直接调用RVM验证基类函数库,里面定义了很多标准的函数类[7]。主要包括构造事务对象的RVM_DATA类、构造处理事务对象的处理器(Transactor)的RVM_XACTOR类、构造传输事物对象的通道(Channel)的RVM_CHANNEL类、构造控制整个验证环境的RVM_ENV类和反馈信息的消息类RVM_LOG等。有了这些基类后,验证工程师很容易实现各个组件间的同步关系和事物对象在组件间的传输等,不仅使得验证工程师能很容易地编写一些较复杂的测试平台,而且还使得编写出的验证环境更容易理解、调试和重用。

3 RVM验证方法学在芯片验证中的应用

笔者在重邮信科TD-SCDMA手机芯片的验证中运用了RVM验证方法学来搭建测试平台,提高了验证的效率,同时也大大提高了验证资源的可重用性。本文重点介绍芯片中I2C总线的寄存器传输级(Register Transfer Level,RTL)验证及相应测试平台的搭建。I2C总线(即IIC总线,Inter Integrated Circuit Bus)是一种用于IC控制的简单的双向两线串行总线,系统中每个I2C器件都有一个唯一的地址。发送器或接收器可以在主模式或从模式下操作。I2C总线最重要的特征就是只要求两条总线线路:一条串行数据线SDA,一条串行时钟线SCL。简单的两线串行I2C总线将IC间互联减到最小。

3.1 I2C的RTL级验证

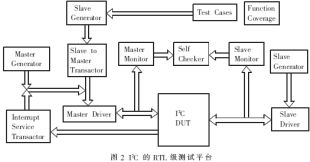

在验证过程中,需要对逻辑功能、模块行为、波形定时关系等进行检查,如果不满足要求,会输出仿真错误信息,以引起验证人员注意。其中,I2C的RTL级测试平台的结构如图2所示。

3.1.1测试平台中的主要模块

(1)可验证性设计模块(DUT):即被测试设计模块,在测试中提供给信号层端口信息,实现与整个验证模块的正常通讯。本文中的I2C DUT主要支持三种工作方式:写、连续读(直接读取)和复合读(先写后读)。DUT对外的主要通信端口如表1所示。

(2)测试例模块(Testcases):Testcase是顶层模块,控制着整个环境的运行。主要是验证工程师根据设计人员提供的设计分析文档编写随机测试例,限制底层模块激励的产生和驱动,验证工程师可以根据需要编写的多个测试例来完成模块所有功能的测试。I2C模块共写了四个测试例,分别是写、连续读、复合读和随机产生错误ACK的测试例。

(3)激励产生模块(Generator):这个模块主要是产生验证DUT的随机激励。这些激励被封装在一个数据对象(data object)或事务(transaction)中,Generator将产生的这些数据对象或者事务通过输出通道传到下层模块。I2C包括两个Generator:Master Generator和Slave Generator。Master Generator主要是随机产生DUT的配置数据,如:寄存器的地址配置信息等。Slave Generator主要是随机产生读、写的数据和类型等事务序列。

(4)驱动模块(Driver):包括主机驱动(Master Driver)、从机驱动(Slave Driver)和中断服务程序(Interrupt Service Transactor)。在Master Driver中定义了写、读两个任务(task),将写或读过程中的所有激励都封装在任务(task)中。Master Driver模仿外围设备(APB)通过对DUT与APB的外部接口进行驱动,将产生的数据传给DUT。Slave Driver主要是模仿Master要访问的外设,通过Slave Generator随机产生一些读时需要的数据,根据端口i2c_scl和i2c_sda_o来判断何时主机开始读数据,然后驱动i2c_sda_i来输出数据并送到DUT的读寄存器。Interrupt Service Transactor是一个中断服务程序,当接收到中断时,会把中断信息传给Master Driver。

(5)监控器(Monitor)和自检器(Checker):I2C共有两个Monitor:Master Monitor和Slave Monitor,分别负责监测主机和从机的端口信息。Monitor时刻监测DUT的端口信息,将DUT端口变化的数据信息记录在一个事务中,通过相应的事务通道将这个事务送到Checker中。Checker将从两个Monitor中接收到的事务进行自动比较,检查DUT是否存在bugs。

(6)功能覆盖(Function Coverage):功能覆盖模块和测试平台中的所有模块都有联系,使用功能覆盖可以帮助找出功能上的缺陷,主要用来衡量模块设计是否符合设计需求的所有功能。在I2C模块中主要考察了寄存器配置、中断和使能等覆盖的情况。

3.1.2 测试结果

通过编写随机测试例使DUT的验证达到了代码覆盖率96.65%和功能覆盖率100%。根据验证的要求,代码覆盖率应该达到100%。通过和设计工程师的交流,找出没有覆盖到的代码,查找原因,发现了一些验证中的不足和源程序中的冗余及缺陷(bug),通过修改源代码,同时增加一些直接的测试例,使代码达到了完全的覆盖。

在验证中采用了含错误指示的自核对式测试技术,在生成的.log文件中根据是否有错误报警来判断模块设计或验证代码是否存在缺陷,免去了直接从仿真波形上查找错误的繁琐性。但在测试中,通过仿真出来的波形来检验验证的过程及结果也是非常必要的,特别是牵涉到时序方面的验证时,仿真波形更显示出其在验证过程中的作用;从波形上可以直接获取信号的信息,对验证代码进行修改完善,同时也能观察到存在于DUT内部的信号,查找出更多的bug。在验证I2C模块中仿真出来的写操作部分波形如图3所示。

通过采用RVM设计的测试平台,I2C模块的RTL级验证很成功,达到了预期的效果,设计的测试平台模块性强,易于理解和重用。

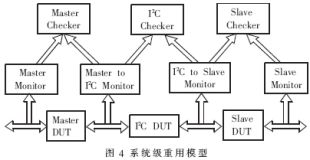

3.2 I2C验证模块在整个系统级验证中的重用

进行完RTL级的验证后,需要把SoC芯片中的各个模块通过接口连接起来,进行整个系统级的验证。在系统级验证时,验证工程师需要对自己的验证模块进行监控,检查各个模块的输入和输出端口,进行输入输出结果的比较。此时,可以将模块级测试平台中的部分模块重用到系统级验证中来。由于此时的激励是由系统产生的,所以验证工程师只需要把各自模块里面的Monitor、Checker及Functional Coverage模块重用到系统级即可。系统级中I2C验证模型如图4所示。

图2中的Master Monitor、Self checker和Slave Monitor分别被重用到图4中的Master to I2C Monitor、I2C Checker和I2C to Slave Monitor,同时功能覆盖模块也可以重用到系统级,为系统级的验证节省了很多重新编写新代码的工作和宝贵的时间。

通过实际验证设计,与传统的测试平台比较,基于RVM的可重用性SoC测试平台具有更高的抽象性、更清晰的层次性和结构的模块化,易于验证的重用,提高了验证的效率,加快了产品设计和面市时间。

参考文献

1孙海平,丁 健.系统芯片(SoC)验证方法与技术[M].北京:电子工业出版社,2005

2 Keating M, Bricaud P. Reuse methodology manual for system on a chip designs(third edition).[M] Kluwer Academic Pub-lishers,2002

3 詹文法. 测试平台的可重用性研究.合肥工业大学硕士学位论文[D],2004:22~35

4 孟 庆,何乐年等.基于事务的SoC验证策略.半导体技术[J],2002;27(6):29~32

5 王锦程,李德识等.SCV及其在SoC验证中的应用.武汉大学学报[J],2004;37(5):116~119

6 SYNOPSYS data sheet. VCS verificaton library. Printed in the U.S.A,2005

7 SYNOPSYS. Reference verification methodology user guild. Version 8.5.11, December 2004