基于ADSP—TS101S的高性能中频处理模块设计

2008-05-29

作者:罗 毅, 明 望, 候文斌, 陶

摘 要: 结合软件无线电的思想提出了一种宽带数字下变频的设计方案,并从硬件上实现了基于ADSP—TS101S的高性能" title="高性能">高性能中频处理模块" title="处理模块">处理模块。

关键词: TS101S 软件无线电 宽带数字下变频

宽带接收是快速发现、全景监控短波频段信号的基础,它的出现为接收跳频、扩频等快速复杂的信号提供了一种很好的解决方案。高性能中频数字处理模块是宽带信号接收系统的重要组成部分,如何高效地从宽带中频数据流中提取出系统感兴趣的窄带信号是本模块所要解决的关键技术难题。

1 系统主要组成部分

1.1 实现功能

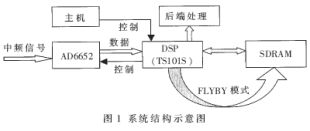

本设计采用二级DDC的方案,第一级宽带DDC采用专用DDC芯片技术,以降低系统对射频前端和信号处理的要求,提高接收系统中频的选择性能。第二级DDC则利用DSP技术和多相" title="多相">多相滤波高效算法实现了在单片DSP(TS101)中同时提取四路窄带中频数字信号的功能。采用大容量数据缓冲池,保证了关键报头的捕获。其硬件平台如图1所示。

1.2 工作流程

如图1所示,模拟中频信号输入到AD6652,主机控制DSP(TS101S),通过软件改变AD6652的下变频参数,完成A/D" title="A/D">A/D变换与第一级DDC抽取,之后数据通过与TS101S互接的高速Link口输入DSP;DSP对输入的数据进行滤波,抽出窄带信号输出到后端进行处理。为了避免处理中丢失报头,数据在输入到TS101S处理的同时通过DMA通道储存到SDRAM缓存一段时间以便查找。

(1) TS101S 简介

本模块中ADC采样频率为40MHz , 经第一级DDC后输出到DSP。DSP对信号进行处理,根据主机指定的多个信号中心频率同时实现四路软件DDC。从带宽为500kHz的信号中输出带宽为125Hz~3kHz的信号,需要DSP具有很高的运算能力,故选用 ADSP—TS101S。

TS101S 是AD公司新近推出的高性能浮点DSP,具有极高的处理能力,峰值浮点性能1800MFLOPS,主频可达250MHz或300MHz;TigerSHARC静态超标量结构使DSP每周期能够执行多达4条指令、24个16位定点运算和6个浮点运算;3条相互独立的128位宽的内部数据总线,每条连接了3个2Mbit内部存储器块中的一个,提供4字(word)的数据、指令及I/O" title="I/O">I/O访问和14.4Gbps的内部存储器带宽;此外还有4个8bit全双工高速Link口,每个Link口传输率达到250Mbps,可以方便灵活地进行高速数据传输。

(2) AD6652简介

AD6652是ANALOG公司的高速AD&DDC器件,它包含1个集成双通道并具有12 位精度的ADC和1个集成4通道并具有最高带宽为120kHz(单通道)的DDC。由于该器件内部高速采样保持电路性能优良,故适合带通采样。

ADC 为差分输入,最高采样率为65MSPS,最高模拟输入信号频率为200MHz。DDC 为矩阵输入,输入更加灵活,减少了交叉连接产生的寄生信号;同时可以根据应用的不同在CIC5 滤波后进行多相合并,增加带宽;在后端有数字AGC 功能,适合于ADC 的宽带输入信号经过DDC变成几路窄带信号后的增益调整。ADC 的数据输出在内部直接连接到接收器的DDC 的输入矩阵,简化了设计,减少了交叉连接产生的寄生信号,大大改善了中频数字处理模块的性能,具有并行数据和Link口两种输出方式。

(3) 数据缓冲池

TS101S内部集成了一个SDRAM控制器,能够直接驱动最大容量为256MB的外部SDRAM。本设计采用MICRON公司的128M DIMM168内存条MT4LSDT1664AG作为数据缓冲池。

AD6652到数据缓冲池的数据传输采用TS101S的FLYBY模式:数据从外部I/O设备通过TS101S的DMA通道直接输入SDRAM,不涉及核操作,非常经济。采用FLYBY模式实现高速缓存示意图如图2所示。

(4) 软件接收机模块

AD6652处理后输出的信号带宽为500kHz,在TS101S中进行第二级DDC处理,同时实现四路软件DDC,最终输出的信号带宽为125Hz~3kHz。

本模块采用多相滤波方式实现第二级DDC,每一路DDC分三级FIR滤波器。

当FIR滤波器为r阶,则转移函数为:

利用多采样率系统中结构的等效变换原理,将滤波器多相分析分量与抽取操作进行如图3 所示的互换,这种互换对系统特性不做任何改变,却大大减少了运算量。运用这种多相分解使滤波器的滤波操作运算量减少到原来的1/M。

(5) 数据通讯

中频处理模块与主控计算机通过HOST接口通讯,通过TS101S的高速Link口将抽取的窄带数据送入后端处理。

2 系统硬件电路设计

2.1 系统电源设计

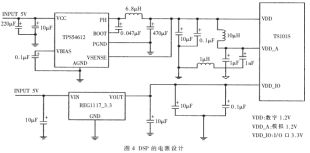

本模块的电源共四种,分别为1.2V、2.5V、3V、3.3V。其中,为数字电路供电的有1.2V、3.3V、2.5V三种,为模拟电路供电的有1.2V和3V两种。为了保证系统正常工作,模拟电路和数字电路的电源分别提供。

为了保证输入“洁净”的电源,在紧贴AD6652和TS101S的电源引脚处用两个电容进行高频滤波;地分为数字地与模拟地,并通过一个磁珠单点连接。

TS101S要求核供电不能晚于I/O供电,故对TS101S核和I/O供电分别由两个电源提供。TS101S供电设计如图4所示。

2.2 时钟设计

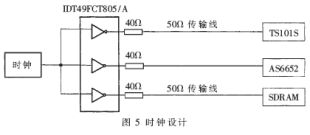

时钟设计对于系统是十分重要的。本设计中使用同一个时钟源,通过时钟驱动芯片IDT49FCT3805统一供给所有器件。时钟线应做到基本等长且尽量短,并通过阻抗匹配,提供一个统一的时钟基准,如图5所示。

2.3 系统的复位设计

本系统中需要复位的有TS101S和AD6652,TS101S对复位的要求较高,其复位设计如下:

(1)上电复位

上电复位时序如图6所示。

DSP要求上电且strap选项稳定后,reset引脚必须保持至少2ms的低电平,然后产生高脉冲至少50个时钟周期(最大100个时钟周期),再次为低有效,要求维持至少100个时钟周期。

(2)正常复位(上电稳定后的热复位)

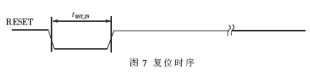

复位时序如图7所示。

DSP的正常复位要求RESET引脚必须保持至少100个时钟周期,strap选项稳定后,RESET引脚必须保持至少2ms的低电平。

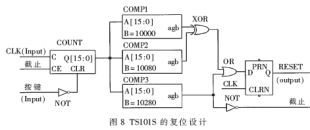

(3)对TS101S两种复位的处理

对上电复位采用CPLD来实现,热复位用按键人工复位,也在CPLD中一并配置实现。复位逻辑电路如图8所示。

3 硬件设计时需注意的问题

(1)高速PCB设计时,如果时钟信号不由外部提供,最好只使用一个时钟源,驱动后分配给各所需的部分。注意将时钟驱动芯片置于适当位置,使输出时钟线基本等长。时钟芯片下应大面积铺地,并避免离信号线太近。

(2)电源输入时应加多个旁路电容,提高系统配电的质量,降低共模射频能量并进行电源滤波。TS101S和AD6652接入电源前,需紧贴芯片在电源脚和地脚之间直接接去耦电容;芯片周围布上电网,以减少外界干扰。设计中应区分数字和模拟电路并分别供电,数字地和模拟地之间通过磁珠单点连接。这样可以最大限度保障模拟电源不受污染,这是保证系统正常工作的重要条件。

(3)在TS101S电路中,对所有的输入信号必须有明确的处理,不能悬浮或置之不理。

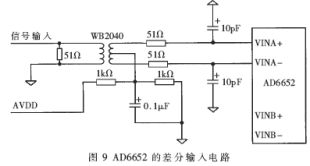

(4)对A/D 部件的设计必须保证其功能和性能的实现。AD6652可同时进行两路A/D 转换,每个A/D通道模拟信号采用差分输入,额定模拟输入电压的最大范围的峰-峰值为1V。为了获得较好的动态性能,2个差分输入端的阻抗必须匹配,常采用变压器匹配的方法。AD6652的差分输入电路如图9所示。

(5)DSP指令周期为ns级,因而DSP硬件系统中最易出现的问题是高频干扰,因此在制作DSP硬件系统的印制电路板(PCB)时,应特别注意对地址线和数据线等重要信号线的布线要做到正确合理。布线时尽量使高频线短而粗,且远离易受干扰的信号线,如模拟信号线和时钟线等。

经过测试,该模块实现了从宽带数据流中同时提取四路窄带中频数字信号的功能。利用TS101S的Link口还可以方便地进行模块扩展及板间互联,以适应更复杂的系统。

参考文献

1 ADSP-TS101S tigerSharc embedded processor datasheet.Analog Device Inc, 2004

2 ADSP-TS101S TigerSharc hardware reference.Analog Device Inc, 2004

3 12 bit 65MSPS IF to baseband deversity receiver AD6652 datasheet. Anglog Device Inc, 2004

4 杨小牛.软件无线电原理与应用,北京:电子工业出版社,2001

5 刘书明, 罗军辉. TigerSHARC DSP应用系统设计.北京:电子工业出版社, 2004