大多数的现代电源都要求从输入线路所吸收的电流包含谐波含量。实际上,规范标准要求线路电流接近正弦波形,而且相位与线路电压同相。为此,通常在桥电路与大电容之间插入所谓的PFC预稳压器。这个中间段设计输出恒定的直流电压,同时从输入线路吸收正弦电流。PFC段通常采用升压配置,要求输出电压比线路可能最高的电压电平都要高。这就是为什么欧洲或是通用主电源输入条件下输出稳压电平普遍设定在约390V的原因。

对于较低功率的应用而言,临界导电模式(CrM)(也称作边界、边界线甚至是瞬态导电模式)通常是首选的控制技术。这种控制技术简单,市场上有采用这种技术的不同的商用控制器,容易设计。然而,高输入电压时,如果输入和输出电压之间的差距小,PFC段会变得不稳定。本文将说明解决这种问题的方法。PFC段一个更加常见的问题是通常发生在启动时的大电流过冲,而不论采用的是何种控制技术。

临界导电模式工作

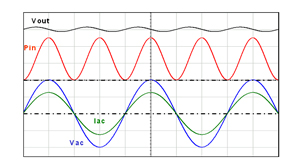

临界导电模式(CrM)工作是低功率应用中最常见的解决方案。这种控制方法可以采用可变频率控制原理来描述特征,即电感电流先上升至所需线路电流的2倍,然后下降至零,接着再上升至正电流,期间没有死区时间(dead-time),如图1所示。这种控制方法需要电路精确地检测电感的磁芯复位。

图1 临界导电模式工作

零电流检测

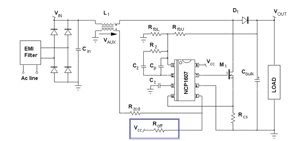

确定退磁完成的常见解决方案在于感测电感电压,更具体地说,就是检测电感电压何时降至零。监测线圈电压并非经济的解决方案。相反,这升压电感与小型绕组相关,这绕组(称作“零电压检测器”或ZCD绕组)提供了电感电压的一个缩小版本,能够用于控制器上,如图2所示。ZCD绕组采用耦合形式,因而它在MOSFET导电时间(反激配置)期间呈现出负电压,如图3中所示。这绕组提供:

VAUX=-NVIN,当MOSFET导通时;

VAUX=N(VOUT-VIN),当MOSFET开路时。

其中,N是辅助绕组与主绕组之间的匝数比。

NCP1607驱动的应用段典型应用示意图" border="0" height="144" hspace="0" src="http://files.chinaaet.com/images/20100812/c9af1cfa-3ddc-4333-b3ad-1ed2fa38917f.jpg" width="300" />

图2 NCP1607驱动的应用段典型应用示意图

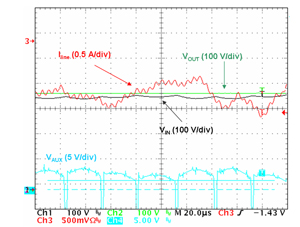

图3 波形

当ZCD电压(VAUX)开始下降时线圈电流会达到零。许多CrM控制器内部比较VAUX与接近0V的ZCD参考电压,检测出下降沿,并准时启动下一个驱动信号。为了实现强固的工作,应用了磁滞机制,并实际上产生较高的(upper)阈值(VAUX上升时有效)及较低的(lower)阈值(VAUX下降时有效)。出于不同原因(如安森美半导体NCP1607 PFC控制器中的ZCD引脚的多功能性),在大多数商用器件中这些阈值都相对较高(在1V及2V之间)。

例如,NCP1607数据表中可以发现下述的ZCD阈值规范(引脚5是监测ZCD信号的电路)。

Vpin5上升:最低值为2.1V,典型值为2.3V,最大值为2.5V;

Vpin5下降:最低值为1.5V,典型值为1.6V,最大值为1.8V。

要恰当地检测零电流,VAUX信号必须高于较高的阈值。

极高输入线路时的不精确零电流检测

图4及图5显示出在高线路时会面对的一个问题。VAUX电压在退磁相位期间较小,而这时Vin较高,因为VAUX与输出输入电压差成正比VAUX=N(VOUT-VIN)。此外,如图4所示,输入电压在开关频率呈现出交流含量。因此,VAUX波形并不平坦,相反,它还包含纹波。在低线路时,这纹波可以忽略不计。在高线路时,VAUX幅度在退磁相位期间较小。因此,这些振荡可能大到足以导致过早检测电感磁芯复位。事实上,如图4和图5所示的那样,零电流检测的精度降低了。

图4 不精确零电流检测导致的不稳定性

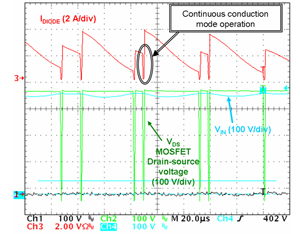

图5 连续导电模式工作

图4显示出现不稳定性问题时高输入线路(正弦波顶端,此处Vin约为380V)下的VAUX电压。我们可以看到MOSFET关闭时,VAUX电压轻微跃升至高于ZCD阈值。由于其大纹波的缘故,在退磁相位期间,VAUX电压首先增加,然后下降。由于在某些开关周期的末段VAUX接近ZCD阈值,这VAUX电压下降导致零电压比较器在电感磁芯完全复位前就翻转(trip)。图5证实了这一论断。有时,升压二极管仍在导电时,PFC段开始新的周期。这个现象主要导致线路电流失真(见红色迹线)、功率因数退化,并可能有一些频率处在人耳可听到的噪声。

改善高线路工作的简单调整方法

如图6所示,在VCC与引脚5(ZCD引脚)之间布设一颗电阻,能够减轻或抑制这个现象。这样一来,ZCD引脚上就产生了偏置。

图6 ZCD引脚上的调整

在测试的应用中,VCC为15V,且Rzcd=68kΩ。在VCC与引脚5之间增加一颗电阻Roff=680kΩ,就改变了施加在引脚5(ZCD引脚)上的电压。退磁相位期间ZCD引脚上施加的实际VAUX电压就变为:

![]() (1)

(1)

然后,施加在引脚5上的电压就偏置。事实上,这就像是VAUX电压与减小了1.36V的ZCD阈值比较。这样一来,新的实际ZCD阈值就是:

Vpin5上升:最低值为0.74V,典型值为0.94V,最大值为1.14V;

Vpin5下降:最低值为0.14V,典型值为0.24V,最大值为0.44V。

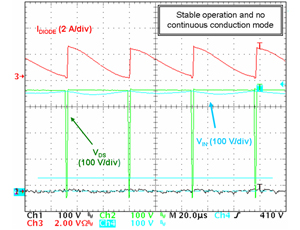

这些降低的ZCD阈值增加了ZCD的精度,并能抑制CCM工作,在相同条件下获得的波特图(见图7)就证实了这一点。

图7 调整改善器件工作

必须注意,Vpin5下降(我们的案例中是1.5V)时,偏置必须保持在低于ZCD最低阈值。这是为了确保新的实际ZCD阈值(Vpin5下降时) 保持高于0V。否则,系统可能难于检测磁芯复位并因此启动新的开关序列。出于这个目的,应当考虑到VCC的变化。

启动时的大过冲

PFC段从输入线路正弦波电压源吸收正弦电流,因此,它们为负载提供仅匹配平均需求的方波正弦功率。输出电容(大电容)“吸收”实际提供的功率与负载消耗的功率之差值。

● 馈送给负载的功率低于需求时,输出电容放电,补偿功率差额。

● 提供的功率超过负载功耗时,输出电容充电,存储多余的能量。

因此,输出电压呈现出输入线路频率2倍的低频交流含量。不利的是,PFC电流整形(current-shaping)方法均基于控制信号无纹波的假设。否则,就不能够优化功率因数,因为输入线路电流重新复制了控制信号失真。这就是众所周知的PFC电路动态性能差的原因。它们的稳压环路带宽设得极低,从而抑制100Hz或120Hz纹波,否则输出电压就会注入这纹波。

由于系统极慢,PFC段遭受陡峭的负载或输入电压变化时,会在大电容上呈现出大的过冲(over-shoot)或欠冲(under-shoot)。启动序列就是这些瞬态中的一种,能够产生大的电压过应力(over-stress)。

图8 输出电压纹波

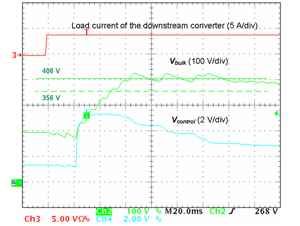

图9展示能在启动相位期间观察到的那类过冲。这波特图是使用由NCP1607驱动、负载是下行转换器的PFC段获得的。

图9 启动相位期间的过冲

承受启动过冲

应用软启动是减小过冲的一种自然选择。然而,设计人员所选择的控制器并不必须具有这个功能特性。此外,从定义来看,这种功能减缓了启动速度,而这并非总是可以接受。

另外一种简单的选择涉及在反馈感测电阻分压器处增加一个电容,如图10所示。在这个图中,我们假定感测网络中上部的电阻分割为两个电阻,而电容Cfb并联连接在其中一个电阻的两端。

图10 小幅调整反馈网络

如果控制电路中嵌入了传统的误差放大器,让我们分析电容Cfb的影响。在稳态,Cfb改变了传递函数。通过检测,我们立即注意到它增加了:

处于下述频率的一个零点:

(2)

(2)

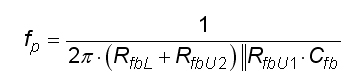

处于下述频率的一个极点:

(3)

(3)

控制器集成了传导误差放大器(OTA)时,情况就有点不同。这是因为反馈引脚(误差放大器的反相输入)不再是虚接地(virtual ground)。因此,电阻分压器中下部位置的电阻(RfbL)影响了极点频率的表达式。实际上,采用OTA时:

(4)

(4)

然而,PFC输出电压的稳压电平通常处于390V范围,而控制器参考电压处在少数几伏的范围。因此,与(RfbU1+RfbU2)相比,RfbL极小;如果RfbU1与RfbU2处在相同范围,或如果RfbU1小于RfbU2,我们就可以考虑:RfbL=RfbU2。事实上,设计人员基于这些考虑因素,能够得出近似Cfb产生的极点频率,即:

(5)

(5)

最后,两种配置中都获得相同的极点。

这些条件(RfbU1≈RfbU2)或(RfbU1≤RfbU2)并非限制性条件。相反,满足这些条件是明智之举,因为RfbU1两端的电压及相应的Cfb两端的电压取决于RfbU1值与(RfbU1+RfbU2+RfbL)总电阻值的相对比较关系。这就是为什么它们是现实可行的原因。

如果RfbU1与RfbU2这两个电阻拥有类似阻值,

![]() (6)

(6)

如果RfbL=RfbU2:

![]() (7)

(7)

最后,如果与RfbU2相比RfbU1极小,我们就获得在控制至输出传递函数中抵消(cancel)的极点和零点。这样,增加Cfb就对环路和交越频率没有影响。如果RfbU1与RfbU2处在相同范围,低频增益就略微增加,交越频率就以跟fp与fz的相同比率增加。事实上,特别是在RfbL=RfbU2时,这个增加的电容并不会大幅改变PFC段的动态性能。

然而,在启动相位期间,这个电容发挥重要作用。当输出电压上升时,Cfb电容也充电。Cfb充电电流增加到反馈电流中,所以稳压电平临时降低。这增加的电流与Cfb电容值成正比,并取决于输出电压的陡峭度,因此,在输出电压快速充电时,这个影响更引人注目。

实际验证

在应用中已经测试了调整方法,反馈网络如下所示:

RfbU1≈RfbU2=470kΩ

RfbL=6.2kΩ

电阻RfbU1两端放置了一个100nF电容。它必须是一种高压电容,因为若我们假定输出电压最大值为450V,它两端的电压可能达到223V。作为一项经验法则(rule of the thumb),我们选择了100nF电容值,这样,在观测到过冲时,时间常数(RfbU1Cfb)就处在启动时间的范围之内。

图11比较没有时的启动序列(左图)与有Cfb时的启动相位(右图)。这些波特图清楚显示电容的影响。Cfb充电电流人为地增加了输出电压(即图中的Vbulk)充电期间的反馈电流,导致预期的控制信号(Vcontrol)放电。因此就没有观测到输出电压过冲。我们可进一步指明,启动时间未受明显影响。

图11 有Cfb(左图)及没有Cfb(右图)时的启动特性

图12显示了没有Cfb时(左图)及有Cfb时(右图)PFC段对突兀的负载改变(120W阶跃)的响应。我们的案例中(RfbU1=RfbU2),Cfb产生并不会相互抵消的额外极点及额外零点,且轻微改变环路特性。然而,最重要的是,采用Cfb还是改善了响应,因为较大的输出偏差(Output deviation)使这些负载阶跃类似于启动瞬态。因此,Cfb在这里同样帮助控制电路出现预料中的所期望的电平恢复。

12 没有Cfb时(左图)及有Cfb时(右图)PFC段对负载阶跃变化的响应

结论

本文讨论了如何解决PFC段经常会面对的两个问题。首先,在CrM应用中,零电流检测在高输入线路时精度不高,而当输入线路电压非常接近输出电压时,可能会出现某些不需要的连续导电模式周期,导致一些功率因数退化,及可能出现一些人耳可听到的噪声。能够使用一颗简单的电阻来改善这功能。其次,在启动序列期间,PFC段也可能呈现出过大的过冲。可以在反馈感测网络中放置一颗电容来限制或抑制这过应力。即便是在电源设计的极晚阶段,这两种调整方法都易于实施。