多天线软件无线电平台中多片AD9238与DSP接口设计

2008-07-03

作者:谢泽明,刘樟华,林武呈

摘 要: 设计了一个应用于多天线" title="多天线">多天线软件无线电" title="软件无线电">软件无线电平台的阵列数据采集" title="数据采集">数据采集系统,重点设计了ADC转换和DSP之间通过EMIF总线进行数据传输的接口电路" title="接口电路">接口电路。提出了一种类似数字复用技术的共享总线,采用同步转换、分时读取的多路AD信号与FIFO存储接口机制,取得良好的数据传输效率。

关键词: 软件无线电 A/D" title="A/D">A/D转换器 FPGA DSP EMIF

软件无线电的中心思想是构造一个具有开放性、标准化、模块化的通用硬件平台,用软件完成各种功能,从而研制出具有高度灵活性、开放性的新一代无线通信系统[1]。本文基于软件无线电的思想,提出并实现了一种多天线软件无线电接收机[2]。基本思想如下:4路天线同时进行分集接收,接收信号零中频变换后得到4路基带I/Q信号,基带I/Q信号同时送入4片双通道A/D转换器进行模数转换,模数转换后数据送入DSP中进行处理。本文重点研究了多天线系统中对多片ADC的控制及其与DSP之间接口电路的设计和实现。

应用FPGA的可重复编程性,可以灵活地设计各种控制和接口电路。采用FPGA直接控制A/D转换的方式可以达到高速数据采集的目的。但对于此多天线、多通道的多片并行A/D系统,如不优化设计,则接入到FPGA的管脚数太多,这样会造成FPGA系统的资源浪费和成本增加。本设计给出一种类似于多路数字复接的共享总线,采用同步采集、分时读取的方法,达到了对A/D进行有效控制和数据高速传输的目的,同时合理地应用了FPGA的资源,降低了硬件成本。

1 控制与接口电路的基本原理和设计

A/D数据采集与DSP接口电路的系统结构如图1所示。由图可知,系统主要包括A/D数据采集和控制、FIFO数据存储、EMIF总线接口等部分。4路射频信号经过前期的处理得到4组共8路I、Q信号。将8路I、Q信号分别送入四片双通道A/D转换器同时进行模数转换,转换数据经A/D控制单元分时,轮转存入FPGA中的FIFO单元,由EMIF接口模块送入DSP进行处理。

1.1 基本原理

共享总线、同步转换、分时读取方法借鉴了分时操作的数字复用思想,按照时间片来对A/D转换结果进行轮换读取。如图1所示:在硬件设计上,4片8路A/D转换器的时钟信号由DSP外部时钟经过分频电路提供,所有的A/D共用同一时钟,共享数据总线,共享时钟保证了4片A/D转换芯片的同步,共享数据总线节约了FPGA的管脚,合理地利用了FPGA的资源。通过分别使能OE1~OE4信号,在A/D转换完成后的数据有效时间内,分时读取转换结果并存入FIFO缓冲单元。当FIFO内部存储的数据达到设定的数量时,就触发DSP中断,调用中断服务程序从EMIF总线通过EDMA控制器将数据读入DSP中。

1.2 模数转换器AD9238简介

本文采用ADI公司的AD9238作为A/D转换芯片。AD9238为双通道,每个通道具有独立的时钟,可以灵活设置进行隔离模数变换的12位高速A/D变换芯片[4]。AD9238有20MSPS、40MSPS和65MSPS三种速度级别可供选择。本设计最高采样频率20MHz,并行采集4组共8路I、Q信号。A/D采样时序如图2所示,AD9238的数据输出有7个时钟周期的流水线延迟,所以在开始采样后前7个数据是无用的,应该在后端数字信号处理时舍弃掉。AD9238两个通道的12bit数字信号输出是独立的,在本设计使用共同时钟的条件下,各自独立输出转换结果。在转换结束后,通过控制各片A/D的输出使能信号OEA/OEB就可以把输出数据通过总线输入到FPGA中的FIFO中。完成整个4片A/D采样和读取控制的步骤如下:

(1)FPGA为ADC提供采样时钟CLK;

(2)在CLK高电平时段,顺次使得OE1~OE4分别有效,数据轮换读入FIFO中;

(3)OE无效,进入下一个转换周期。

1.3 EMIF总线控制原理

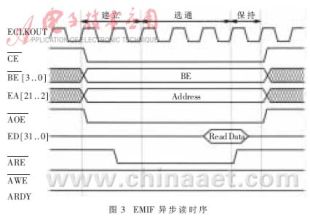

EMIF总线是C6000系列DSP与外部存储器的接口,C6713的EMIF接口具有很强的接口能力,其数据总线为32位,可寻址空间为4GB,可以实现与SBSRAM、SDRAM、SRAM、ROM、FIFO等的无缝接口[3]。本文通过EMIF异步读写外部FIFO,其读时序要求如图3所示。每个读/写周期由建立、选通、保持这三个阶段组成。相关的信号/CS为外部存储器片选信号;/BE为字节选择信号,确定数据宽度;时序设计时,先按照器件的典型参数计算读/写周期,并保持一定的时间裕量,然后实际测试,验证通过。/ARE为异步读使能;/AOE为异步输出使能;/AWE为异步写使能;EA为外部地址线;ED为外部数据线。

2 FPGA逻辑控制功能的实现

本文采用ALTERA公司的ACEX1K系列FPGA完成逻辑控制功能,主要包括时钟分频及控制,4路并行双通道A/D数据采集与控制,FIFO数据存储与传输控制,与DSP的EMIF接口,EDMA事件触发控制等。

2.1 A/D控制模块

根据前面介绍的A/D数据采集时序图可知:在采样频率CLOCK为高电平的半个周期内,输出转换结果是可靠和稳定的,在时钟信号CLOCK的半个周期内,以共享总线方式可以完成4路A/D的数据采集。图4为4路A/D共享数据总线的控制时序图,采用quarts II 仿真工具完成,其中EQ0为A/D采样时钟,EQ1~EQ4分别为4片A/D的片选信号(低电平有效),在有效时,允许A/D转换数据输出,输出数据的同时,必须把数据写入FIFO,否则数据会丢失。当EQ1-EQ4有效时,WRREQ输出高电平作为FIFO的写允许,CLKN的非信号WRCLK作为FIFO的写时钟,在WRCLK的上升沿刚好把ADC的输出数据写入FIFO。

2.2 FIFO 数据缓冲模块

FIFO模块暂存A/D转换数据;在FIFO中开辟一定大小的数据存储区,在每个A/D转换周期内,通过数据总线读入4×24bit数据;在FIFO中数据达到设定的容量后,FPGA向DSP发中断信号,触发DSP读取FIFO数据。在DSP读取数据的同时,为了防止数据的丢失,此期间内的A/D转换数据也要同时存入到FIFO中,所以,要求使用可以同时进行读写的双口FIFO实现此模块。用MAX+Plus II自带的可调参数模块LPM-FIFO-DC可快速实现,此FIFO是双时钟同步FIFO,具有异步清零ACLR、读时钟RDCLK、读允许RDREQ、写时钟WRCLK、写允许可自定义容量。定义大容量可以减少DSP外部中断次数,EDMA每次可以搬移的数据块增大。根据DSP异步读外部存储器的时序[3],控制信号/CE2、/AOE、/ARE把FIFO数据读入DSP,仿真时序如图5所示。

3 试验测试及性能分析

实测数据传输率及性能分析是设计数据采集系统的重要步骤。在本文中,ADC到FIFO数据传输和DSP读取FIFO速度测试是两个主要内容。

3.1 ADC 模块数据传输测试

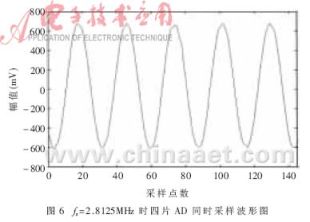

本平台的4个ADC模块数据写入FIFO时共用数据总线,使用74VHC541作为总线控制开关。在接口设计中,综合考虑74VHC541的传输延迟,选通延迟、写FIFO的建立和保持时间以及控制接口和ADC模块的排线及PCB传输延迟。实测结果表明:4个ADC模块同时采样速率为2.8125MSPS时,采样数据正确。此种情况下,相当于单板ADC采样频率可达11.25MSPS。图6是该情况下一个ADC通道采样波形,可看出采样波形完整。

3.2 DSP数据传输测试

DSP通过异步方式读取外部FIFO,在设置读取过程的建立、选通和保持时间等时序参数后,当DSP的外部存储器时钟为90MHz时,实测表明:若采用CPU中断,中断服务程序通过执行语句的方式从FIFO中读入512×32bit的数据块,即使中断服务程序经过优化,数据吞吐率也只有4.5×32Mbps。且此时CPU时间全部消耗在数据搬移工作上,无力进行数据的处理工作。

若采用外部中断触发EDMA传输的机制,利用存储器的乒乓操作,则同样从FIFO中读入512×32bit的数据块,控制接口到DSP中L2的传输数率可以达到22.5×32Mbps的理想传输效率。

本文设计了一种多片双通道ADC与DSP的传输接口电路。实测结果表明:采用共享总线、同步转换、分时读取的方法,可以有效减少FPGA管脚的使用,同时达到数据高速传输的效果。本文中,若要进一步提高ADC的数据传输速率,可以选用内部自带FIFO的ADC或者选用性能较好的缓冲器作为总线控制开关。

参考文献

[1] 杨小牛,楼才义,徐建良.软件无线电原理与应用.北京:电子工业出版社,2001:1-7,88-173

[2] 谢泽明,赖声礼,龙智文.智能天线实验平台研究.电子技术应用,2004,30(3):39-42.

[3] Texas Instruments Incorporated.TMS320C6000 EMIF to External FIFO Interface.pdf.

[4] Analog Devices,Inc.AD9238.pdf,REV.A.