2.4GHz 0.18μm CMOS低噪声放大器分析与设计

2008-07-04

作者:王宁章,周长川

摘 要: 基于低噪声放大器设计原理,从噪声、线性度" title="线性度">线性度、阻抗匹配" title="阻抗匹配">阻抗匹配等方面详细讨论了低噪声放大器的设计。电路采用TSMC 0.18μm CMOS工艺进行设计,利用ADS2005A对电路进行谐波平衡、S参数分析及双音测试,结果表明,其噪声系数" title="噪声系数">噪声系数为1.795dB,正向增益为17.35dB,IIP3约为-1.43dBm,功耗约8.96mW。

关键词: 低噪声放大器(LNA) 线性度 匹配

现代无线通讯设备不断向着低成本、便携式的方向发展。而传统的射频集成电路主要采用GaAs工艺,成本较高,且集成度很低。随着CMOS工艺的进步,已经能够满足射频集成电路的要求,基于CMOS 工艺的射频集成电路设计成为近年来的研究热点。低噪声放大器(LNA)是射频接收机前端的关键模块,应用中要求其必须提供足够的增益以抑制后续级模块的噪声,提供良好的线性度,使其在较大的信号动态范围内正常工作。同时必须要有优异的噪声性能,这几乎决定整个接收机的噪声性能的优越程度。

通常采用CMOS工艺设计低噪声放大器(LNA)时,需要在增益、噪声、线性度、功耗、阻抗匹配等指标之间权衡。本文针对LNA的噪声、线性度、增益及功耗等指标,提出了优化的设计方法。设计了一个基于TSMC 0.18μm CMOS工艺,工作频率" title="工作频率">工作频率为2.4GHz的低噪声放大器,通过优化达到了较好的性能。

1 电路设计

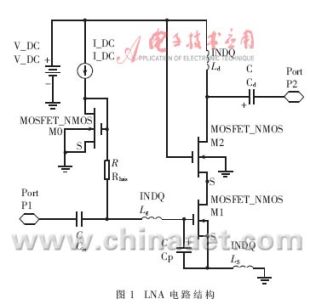

本文设计的单端低噪声放大器电路结构如图1所示。电路采用的是电感源极负反馈的共源-共栅结构(Cascode 结构),这种结构可以在提供较低噪声系数的同时,实现50Ω的输入阻抗。放大器由共源晶体管M1和共栅晶体管M2级联而成,M1的源极接电感Ls形成源极去耦结构, 栅极接电感Lg调整输入电路的谐振频率,M2用于减小输入与输出之间的相互作用,提供良好的隔离,并减小了M1漏栅电容Cgd的影响。电路的噪声性能主要由M1决定,而电路的线性度主要由M2决定,可以通过选择M1、M2栅宽度,以实现优异的噪声性能和线性度。

M1和M0组成电流镜,由于电阻的阻值随温度变化,为了保持偏置支路稳定,采用电流源I_DC提供稳定的偏置电流。Rbais是偏置电阻,它和电流源I_DC一起组成电流偏置支路。Lg、Ls和Cp主要完成输入端口阻抗匹配,Ld和Cd主要完成输出端口阻抗匹配。P1和P2 是输入输出端口,Cin、Cd用于隔离直流信号,V_DC是直流电源。

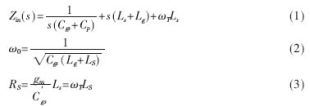

1.1 输入、输出阻抗匹配

电路采用源极电感负反馈结构,在MOS管的栅极、源极各引入一个电感Lg、Ls,在M1的栅-源之间并联一个电容Cp来增大栅-源之间电容。计算M1管栅-源极间的电容,合理选取Lg、Ls,使电路谐振于工作频率,同时获得50Ω输入阻抗Zin(s),满足Zin(s)=Rs=50Ω,当输入端口阻抗匹配时,需要满足:

当输入端口阻抗匹配时,需要满足:

其中gm是M1的跨导,Cgs是M1的栅-源电容,ωT是截止频率,ω0是工作频率。由于LNA的工作频率ω0一定,Cgs可以根据工艺参数计算出来,根据公式(2)、(3)可以得到Lg和Ls的值。输出匹配主要由Ld和Cd相匹配完成,由于中心频率ω0=2π×2.4×109,通过计算,选取合适的Ld、Cd的值,实现输出阻抗匹配。根据公式(2),在ω0确定的情况下,通过在M1的栅-源极之间并联一个电容CP,增大了栅-源电容Cgs,从而使Lg、Ls的值变小,改善了LNA的噪声性能,也易于使用CMOS工艺实现。

1.2 选取合适的栅宽及其他关键参数

电路的噪声性能主要是由M1决定,要选择合适的栅宽度,以实现优异的噪声性能。M1的栅宽越大,噪声越小,但同时会使面积增大,导致功耗增加、增益降低。按照功率约束条件下的设计方法,可以得到M1的最优器件宽度为[3]:

其中:Cox是单位面积氧化层电容,Leff是有效栅长,Qsp是最佳品质因数,Cox的值可以根据工艺参数计算得到。噪声系数对于在3.5~5.5范围内的Qsp值是不敏感的[3],因此取Qsp值为4.5。根据公式(4)得到Wopt约为270μm。M0的栅宽度取M1栅宽度的1/10。

MOS管M1本身栅-源电容![]() ,CP并联接入M1栅-源之间。由于0.18μm CMOS工艺的截止频率fT可以达到40GHz以上,所以根据公式(2)、(3)可以得到LS约等于0.5nH。根据公式(2)可以计算得到Lg等于6nH,由于电感与衬底之间寄生电容以及栅电阻的影响,Lg的值要比计算得到的值小。

,CP并联接入M1栅-源之间。由于0.18μm CMOS工艺的截止频率fT可以达到40GHz以上,所以根据公式(2)、(3)可以得到LS约等于0.5nH。根据公式(2)可以计算得到Lg等于6nH,由于电感与衬底之间寄生电容以及栅电阻的影响,Lg的值要比计算得到的值小。

1.3 线性度分析和M2宽度的选取

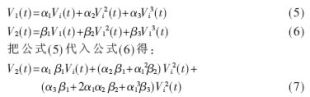

图1所示电路中,MOS管M1、M2可以等效为两级非线性级联结构。设输入信号Vi(t)=Vm(cosω1t+cosω2t),则M1和M2的输出信号分别为:

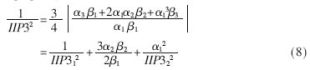

系统的输入三阶交调点IIP3(input-referred third-order intercept point),可以表示为[4]:

其中IIP31、IIP32分别是M1和M2的输入三阶交调点;α1是M1的增益,α1远大于1;系统的线性度主要由 这一项决定,即系统的线性度主要由M2决定。短沟道MOS管的IIP3表达式为[5]:

这一项决定,即系统的线性度主要由M2决定。短沟道MOS管的IIP3表达式为[5]:

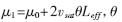

其中:vsat是MOS管的饱和速度,Vod=VGS-VTH称为栅过驱电压, ,θ为迁移率的衰减系数,θ的估计值为[3]:

,θ为迁移率的衰减系数,θ的估计值为[3]:![]() ,tox为栅氧化层厚度。

,tox为栅氧化层厚度。

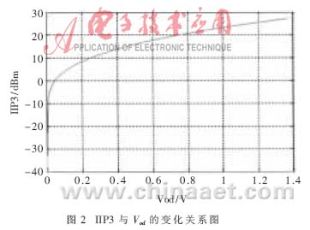

从图2看出,要提高M2管的IIP3值,可以加大它的栅过驱电压Vod,但这会使直流电压变大,电路的功耗增大。根据公式(9),MOS管的线性度与栅宽度W无关,但是当栅宽度变化时,会引起Vod的变化,间接影响线性度。不增大偏置电压的情况下,通过改变M2管的栅宽度,来改变Vod,可以提高M2的线性度。

当M2管的栅宽度变大时,栅过驱电压Vod变小,线性度变差;当M2管的栅宽度减小时, Vod变大,线性度变大。为得到较好的线性度,M2管的栅宽度取M1管的一半。测量M1管和M2管的栅过驱电压Vod1和Vod2,根据公式(9),计算得到M1管和M2管的IIP31、IIP32。根据公式(8),估计出系统的IIP3点。

2 电路仿真结果及讨论

本设计基于TSMC的0.18μm工艺,采用BSIM2V3.2模型进行建模,利用ADS2005A进行设计、仿真,取得了较好的效果。考虑到片上电感的Q值不高,大电感不易制作的实际情况,在设计工程中,充分考虑了电感Q值对噪声的影响。采用INDQ模型来模拟片上电感,Q值设为6,中心频率设为2.4GHz,电感的值一般不超过8nH。采用2V电源,直流功耗约为8.96mW。为了得到1dB压缩点P1dB,对电路进行谐波平衡法仿真,为计算线性度,对电路进行双音测试,仿真结果如图3所示。

图3(a)显示了1dB压缩点的仿真结果,m1点和m2点的增益差约为1dB,即增益的1dB压缩点P1dB约为-13.9dBm。图3(b)是双音测试输出频谱图,根据公式(10),计算得到输入三阶交调点IIP3大约为-1.429dBm。

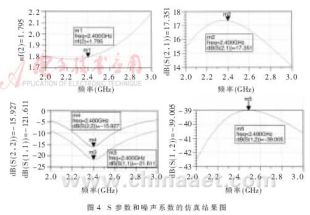

对电路进行S参数仿真,得到噪声系数和S参数的仿真结果如图4所示。

由图4可以看出,当低噪声放大器工作在2.4GHz时,噪声系数为1.795dB,噪声系数较低;正向传输增益S21约为17.35dB,具有较高的增益;S11、S22参数在工作频率2.4GHz处达到极值,说明输入、输出阻抗匹配良好,S11约为-21.61dB,S22约为-15.93dB,回波损耗很小;S12约为-39dB说明反向隔离特性比较理想。仿真过程中发现,在保证输入输出匹配的情况下,如果提高电感的值,同时减小电容的值,可以使增益(S21参数)提高;而减小电感的值,同时增大电容的值可以改善系统的线性度,这就为增益和线性度的调节提供了一种可行的方法。

本文采用先进的TSMC 0.18μm CMOS射频工艺库参数,通过理论推导和ADS的仿真,设计出符合要求的低噪声、低功耗、高增益、高线性度的低噪声放大器,并且满足了低功耗和全集成的要求。放大器的性能达到了设计要求,与国内外有关设计相比达到了先进水平[1][2][6]。通过对M1的栅-源之间引入并联电容CP,极大地降低了系统的噪声系数。随着CMOS工艺和电感工艺的不断改进,0.18μm CMOS工艺已经可以全部利用片上电感设计出符合设计要求的射频集成电路。

参考文献

[1] KIM N.A Cellular-Band CDMA 0.25μm CMOS LNA linearized using active Postdistortion.IEEE journal of olid-state circuits,2006,41(7):1530-1541.

[2] LISCIDINI A.A 0.13μm CMOS front-end for DCS 1800/UMTS/802.11b-g with multiband position feedback Low-Noise amplifier.IEEE journal of solid-state circuits,2006,41(4).

[3] LEE T H.The design of CMOS radio frequency integrated circuits,second edition.北京:电子工业出版社,2005

[4] RAZAVI B著,余志平,周润德译.射频微电子.北京:清华大学出版社,2006

[5] SOORAPANTH T,LEE T H.RF Linearity of Short-Channel MOSFETs.IEEE Journal of solid state circuits,1997,32(5)

[6] 詹福春,王文骐,李长生.2.4GHz 0.25μm CMOS集成低噪声放大器的设计.半导体技术.2004,29(5):81-85.