CAN总线的PCI接口通信卡设计

2008-07-09

作者:高 强, 任恩恩, 张 涛

摘 要: 介绍了CAN总线的PCI接口通信卡的硬件电路和通信主控程序的设计以及驱动程序的开发,利用PCI接口芯片" title="接口芯片">接口芯片和双口" title="双口">双口RAM以及微控制器实现工业现场总线CAN总线节点与工控机之间的通信,设备驱动程序" title="设备驱动程序">设备驱动程序在实时嵌入式操作系统Vxworks下开发。

关键词: PCI CAN总线 CPLD Vxworks

CAN总线是目前最流行的工业现场总线之一,而PCI总线是目前应用最广泛的一种高速同步总线,具有32bit宽度,总线时钟频率为0~33MHz,最大传输速率可达132MBps,广泛应用于数字图形、图像、语音处理以及高速数据实时采集与处理等领域。本设计利用通用PCI接口芯片PCI9052和微控制器AVR128辅以CPLD xc9536和双口RAM实现CAN总线上各节点与工业控制计算机之间的通信。

1 系统概述

PCI接口通信卡主要功能是完成上位机(工业控制计算机)与CAN总线上各节点之间的信息和数据交换。本设计通过PCI接口芯片将来自上位机的数据信息暂时保存于双口RAM中,由单片机控制通过CAN控制器将这些信息数据下发给CAN总线上各个节点,同时CAN总线上各节点的状态信息上传" title="上传">上传给总线控制器,由单片机控制将其送入双口RAM中,再经PCI接口上传至上位机作进一步数据处理分析。整个过程可看作是数据的下发和上传过程。而CPLD完成对接口芯片、双口RAM以及单片机三者之间的逻辑控制、总线仲裁等任务。

2 硬件实现

2.1 硬件框图及实现过程

系统框图如图1所示。图中,PCI接口芯片采用PLX公司的PCI9052,该芯片实质上是PCI总线与局部总线设备之间的桥梁,以保证局部总线一端的设备在符合PCI 总线的规范时连接到PCI总线上。

在设计中,PCI9052的局部总线设计是较为复杂的环节。PCI9052内部提供了两种配置寄存器" title="配置寄存器">配置寄存器:PCI configuration registers 和local configuration registers。PCI9052本地端提供了26根地址线(27:2)、32根数据线和4根LBE线(可以翻译成不同的地址线),本卡用的LOCAL端是8位数据,在这种模式下,LBE1和LBE0提供地址线[1:0]。PCI配置寄存器提供了6个基地址寄存器,这些基地址是在系统中的物理地址,其中,BASE1和BASE2都是用来访问LOCAL 配置寄存器的基地址,BASE1是映射到内存的基地址,BASE2是映射到I/O的基地址,所以可以通过内存和I/O来访问LOCAL 配置寄存器。BASE2~5四个空间提供了访问本地端所接的四个芯片,它们将本地的芯片映射到系统的内存或I/O口。本设计使用的是内存映射,如果本地端的芯片地址是0x0cc000,本卡设计中将此地址放入local配置寄存器的相应位置space0,同时配置此空间的大小,这样在PCI总线端,系统会根据这个大小分配相应的内存空间(或I/O空间)供PCI9052使用,以映射LOCAL上所接的芯片,且系统分配的内存空间的信息会写入PCI配置寄存器中,读出即可。PCI9052工作时需一片配置芯片EEPROM,本设计中选用93CS46。EEPROM会在PCI卡上电的时候配置PCI9052,主要配置PCI卡的vendorID和deviceID(实质上是对该通信卡的标识)LOCAL端的四个space的LOCAL基地址和大小,以及每个space的其他一些参数。

在该通信卡中,CPLD完成的主要功能包括:地址控制、译码以及地址数据线的分离,双口RAM操作权的获取和释放控制。当有信息数据从PCI接口下发时,CPLD的控制逻辑首先让PCI9052 取得双口RAM的控制权(在这之前,双口RAM已映射为PCI9052的某一内存空间),数据存入双口RAM的过程可看成对PCI本身内存空间的操作。数据下发完毕后,PCI9052则释放控制权,由CPLD通知AVR128获取双口RAM控制权,AVR128与双口RAM的连接采用地址数据复用方式,由CPLD控制其地址数据的分离,AVR128将下发数据首先搬移至自己内存空间,并将这些数据按照CAN通信协议打包,从SJA1000发送至各节点。

当各种状态信息数据从CAN 总线上各节点上传时,其功能与数据下发过程中CPLD所起的作用基本相同,不过应注意一个问题:对于双口RAM的操作,PCI9052和AVR128都有可能要执行。但双口RAM的同一个地址单元不能同时进行写操作,为解决地址竞争问题,需要CPLD附加上总线仲裁功能。CAN总线上各节点的信息中有可能包括某节点的故障信息,一般情况下,应该是信息数据的上传优先。采用VHDL语音较易实现该逻辑功能。

2.2 地址空间分配问题

从整个系统来看,双口RAM要同时映射为PCI9052和AVR128的内存空间,而AVR128要同时将双口RAM和两片SJA1000映射进自己的可寻址空间,所以:(1)在数据下发过程中又突然有数据上传时,应由CPLD保证总线不冲突。(2)映射到AVR128的可寻址空间的三块地址,最好分配时留有一定的间隔,以避免冲突。

3 软件设计

软件设计包括单片机数据收发主控程序设计、工控机的PCI总线设备驱动程序开发以及CPLD的逻辑控制程序设计。

3.1 设备驱动程序开发

设备驱动程序的开发是软件设计中比较复杂的工作。Vxworks中设备驱动程序有查询方式和中断方式两种。中段方式下,事件发生是由中断信号确定的,在中断信号没有出现时,驱动程序处于空闲状态;查询方式下,驱动程序需生成一个任务不断地查询相关寄存器以确定事件的发生。但无论在何种方式下,设备驱动程序的基本流程是相同的。首先应获取硬件接口参数,包括内存映射地址、端口和系统中断控制器的输入(IRQ)。而获取参数的方法由硬件接口方式决定PCI作为一种即插即用的总线结构,在BIOS和操作系统支持下,可自动为设备分配合适的硬件接口参数。本设计中基于PCI总线的系统采用内存映射访问寄存器,接口函数中实现中断服务子程序,且该子程序不能有运行时间过长的代码,以避免死锁而且应该尽快返回。驱动程序框架如下:

//定义常量和全局变量

#define VENDOR_ID xxx

//定义信息数据结构

Typedef struct xxx_info

{

UNIT pciBus,pciDevice

Char irq;

}XXX_INFO;

//获取硬件接口参数

Void xxxInit()

{

//利用PCIdeviceID,VavdorID及总线号功能号

//查找设备

for ( i=0;i

{

重新查找

}

Else

{确定出映射到系统中的设备的基地址}

}

//确定设备的IRQ

pciConfigInbyte(busNo,deviceNo,funcNo,PCI_

CFG_DEV_INT_LINE,&irq);

}

//中断服务子程序

Void xxxIntr()

{

}

//设备初始化子程序

{

//初始化设备

//连接中断服务程序

3.2 单片机数据收发主控程序设计

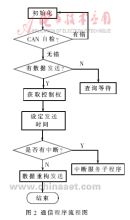

主控程序由两大模块构成:上位机的控制信息数据的下发模块和各节点的状态信息数据的上传模块。整个通信功能的实现须严格按照CAN通信协议,两大模块均须完成与双口RAM通信接口的初始化和SJA1000的初始化。双口RAM通信接口初始化指的是AVR128接到CPLD通知后获取对双口RAM的操控权,而SJA1000初始化需要将SJA1000的内部寄存器编程,且须按如下顺序初始化:检测接口→复位→输出模式及时钟分频设置→通信对象设置→波特率设置→命令寄存器及终端使能寄存器设置→退出复位→工作模式。通信程序流程图如图2所示。

本通信卡设计采用主流芯片及总线技术,充分利用了PCI总线的优点,使其能在工业控制以及数字领域得到广泛应用。利用嵌入式技术的高性能、硬件电路采用的双路逻辑,并结合CAN总线的高可靠性及安全性,使工业控制设备的性能大为改善。将该通信卡应用于铁路交通领域、智能交通等的通信系统中,完全可满足实时性以及安全可靠性的要求,其应用前景广阔。

参考文献

[1] PLX Technology Inc. PCI9052 data book. 1997.

[2] Philips Semiconductors. SJA1000 Stand-alone CAN controller. 2000.

[3] Integrated Device Technology Inc. IDT7005. 1998.

[4] 姚利民,孙逢春.用双端口RAM实现与PCI总线接口的数据通讯.电子技术应用,2006,32(8).

[5] 王军,燕永田,白海威.基于CAN 总线车站信号微机连锁系统的实现.铁路计算机应用,2001,(2).