变参差工作雷达数据采集系统

2008-07-10

作者:王 帅,邓思颖,刘 钊

摘 要: 介绍了基于计算机PCI总线的变参差工作雷达数据采集" title="数据采集">数据采集系统的设计和实现方法。该系统提供一路20MHz最高采样频率、8位采样精度的数据采集通道,在FPGA逻辑控制下,系统可以对16种参差模式的雷达信号" title="雷达信号">雷达信号进行预置采样。实验证明,数据采集速率满足设计要求,数据传输最高达到100MB/s,可供后续雷达信号实时处理。

关键词: PCI总线 数据采集 变参差工作模式 PLX9054 FPGA SDRAM

数据采集技术是现代信号处理的基础,广泛应用于雷达、通信等领域。为了给雷达数据处理提供更加精细的数据,高速、大容量并具有可变参差模式的雷达数据采集系统" title="数据采集系统">数据采集系统是现代雷达需要解决的迫切问题。利用计算机通用平台,可以将16种参差工作模式的雷达信号采集到计算机上,为后续信号处理做好准备。在板卡向计算机进行数据传输时, PCI总线[1][2]以其峰值传输速率高达132MB/s、支持突发传输等突出的性能,成为雷达数据采集首选的计算机I/O接口。

1 雷达信号及采集容量

本课题涉及的雷达天线扫描周期为1s;雷达脉冲重复频率可为2kHz、4kHz、6kHz、8kHz,在一个天线扫描周期内可以指定变换频率;每个雷达回波采样有效个数可为1000、800、600、400。在天线扫描一个周期内,4个可变采样频率和4个可变采样点数构成了16种参差工作模式。密耳为圆周方位角刻度单位,一个圆周有6000个密耳。用户可以任意设定在不同的密耳之间,选择任意的参差工作模式。

从最高脉冲重复频率8kHz计算,两次发射脉冲方位角差为0.75密耳。一帧雷达扫描时间内需要存储的采集样本容量至少为8MB。

16种参差模式体现在不同的触发信号上,分为帧同步信号和脉冲同步信号。帧同步信号(Frame_syn)也叫正北信号,代表雷达扫描线为正北方向,每一秒产生一次。脉冲同步信号(Pulse_syn)代表脉冲回波的开始,即对每个回波采样的开始,由雷达脉冲重复频率确定,如图1所示。

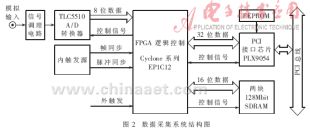

2 数据采集系统的结构

数据采集系统的结构如图2所示。具有16种参差模式的雷达输出视频信号通过数据采集卡的信号调理电路,经隔离限幅放大后,送到模数转换器。这里,采用TI公司的TLC5510芯片,模拟信号将被转换成8位的数字信号。然后将8位数字信号经过FPGA内部生成的双口RAM,并在FPGA的控制下以16位的数据宽度送入SDRAM中缓存。由于需要充足的RAM资源和PLL资源,选用Altera公司的低成本高效Cyclone系列的EP1C12型号芯片。两片SDRAM起到乒乓缓存的作用,当一块SDRAM存满一帧数据后,在FPGA的控制下,这一帧缓存数据以32位的数据宽度通过PCI桥接芯片PLX9054,以DMA方式传输到计算机内存,并生成雷达数据文件,留给后续信号处理用。同时,FPGA向另一个SDRAM写入下一帧雷达数据。SDRAM大小为8M×16位,满足缓存要求。

采集卡上电后,用户通过程序界面设置16种参差模式,由PLX9054将参数传入FPGA内部寄存器中,完成初始化工作。16种参差模式体现在不同的触发信号上。在FPGA内部生成了一个内触发源,用于产生帧同步信号(Frame_syn)和脉冲同步信号(Pulse_syn)。内触发源和外触发信号一起接到FPGA逻辑控制模块,由控制模块根据用户设置的参差来选择使用不同的触发信号。

3 数据采集卡主要功能模块的实现

3.1 PCI接口模块

实现PCI总线接口的方法主要有2种:一种是采用可编程器件实现,这种方法比较灵活,多用于实现PCI接口部分的功能,但设计难度大。另一种采用专用的PCI接口芯片,它可提供可靠的PCI逻辑和功能模块,实现简便。综合考虑,本设计采用PLX公司的PLX9054作为PCI总线接口芯片。

PLX9054[3]是一种符合PCI V2.2规范的32位33MHz PCI总线接口控制器,它可以作为PCI总线的主控设备控制总线,也可以作为目标设备响应总线。PLX9054提供了PCI总线、LOCAL总线、EEPROM三个接口。LOCAL总线是与PCI总线相对应的用户端总线,PCI端的接口由PLX9054完成,它可以完成完整的PCI总线规范2.2版的要求。LOCAL总线有M、C和J三种模式。本设计采用C模式工作。

C模式下的数据传输模式分为PCI Initiator操作和PCI Target操作。在PCI Initiator操作过程中,本地处理器或本地总线主控设备能够直接通过PLX9054访问PCI总线,发起Local-to-PCI的数据传输。而在PCI Target操作过程中,PCI总线主控设备可以以可编程的等待状态、总线宽度和突发传输功能访问PLX9054的三个本地空间(空间0、空间1和扩充ROM空间)。

PLX9054还支持DMA数据传输模式,它作为PCI和LOCAL总线的主设备,从PCI总线存储空间读数据到LOCAL总线存储空间或者从LOCAL总线存储空间读数据到PCI总线存储空间。

在实际的数据采集中。PCI Target模式用于将16种参差模式写入到FPGA内部的采集卡工作参数寄存器。DMA模式用于雷达数据采集后,从LOCAL端到PCI端的数据传输。

PLX9054提供一个串行EEPROM配置接口。在EEPROM中存放了厂家标示、设备标示、本地总线的基地址空间、I/O空间、中断控制信号等信息。当初始化时,系统自动将EEPROM中的配置参数装入PCI配置寄存器,并根据本地总线对内存、I/O口和中断的需求统一划分,自动配置。在设计时采用93LC56作为EEPROM。

3.2 信号调理和模数转换

本设计的雷达信号峰峰值为1V,而模数转换器TLC5510的输入量程为2V,所以需要对输入的雷达信号进行隔离限幅放大。信号调理模块由运放MAX4223构成。经过调理后的雷达信号送到模数转换芯片TLC5510进行模数转换,模数转换时钟由FPGA产生,并且根据参差设置的不同,模数转换时钟将进行变化。

3.3 FPGA逻辑控制模块

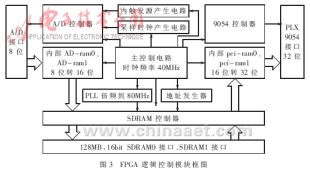

设计中对A/D转换器、PLX9054、SDRAM的控制都是在FPGA中完成的。选用EP1C12型号芯片,采用Verilog语言设计[4]~[6]。在自顶向下的模块设计中,主要划分了三个模块:AD_control,sdram_control,9054_control,以同步状态机的形式实现。图3为FPGA逻辑控制模块框图。

具体工作流程为:

(1)开机或者复位后,系统进入初始化状态,对SDRAM进行初始化,并且等待主机发出的配置命令REG_CMD。当REG_CMD有效时,主机通过PLX9054以PCI Target方式向FPGA内部工作参数寄存器写入16种参差工作模式参数,完成系统初始化。A/D转换器将按照工作参数在采样过程中运行。

(2)系统进入空闲状态,当接收到触发源产生的帧同步信号Frame_syn后,系统进入工作状态,开始采样和传输。

(3)系统进入工作状态后,又分为以下子过程:

①将第一个脉冲同步信号Pulse_syn后的采样数据存入FPGA内部生成的AD_ram0中,将第二个Pulse_syn后的采样数据存入AD_ram1中,同时将AD_ram0中数据读到SDRAM0中。二者交替,AD_ram0和AD_ram1形成乒乓式存储。

②当SDRAM0存满第一帧数据后,FPGA向PLX9054发出sdram0_ready信号,进而PLX9054向主机发出INTA#中断,要求主机读SDRAM0。同时由SDRAM1存放第二帧数据。SDRAM0和SDRAM1形成乒乓式存储。

③主机响应中断,向PLX9054发出读命令Lwr#、Ads#、Blast#等,在FPGA的控制下,把SDRAM0中数据读到FPGA内部生成的PCI_ram0或PCI_ram1中,又从PCI_ram0或PCI_ram1中将数据通过PLX9054读到主机内存中。PCI_ram0和PCI_ram1形成乒乓式存储。

④主机内存读满一帧数据,可以进行后续处理或将其保存成雷达数据文件。

用FPGA生成内部RAM的目的有两点:一是作为缓存,实现时序匹配;二是数据位扩展,将8位A/D数据扩展到16位SDRAM数据,再扩展到32位PCI数据,提高传输效率。

3.4 SDRAM模块

高速数据采集具有数据吞吐率高的特点,大容量的数据存储能力是设计关键之一。SRAM和FIFO存在容量小的缺点,所以本设计应用两块Mircon公司产128Mbit的16位SDRAM组成乒乓式缓存空间,完全满足采集要求。

SDRAM的控制涉及刷新、预充电、行列地址复用等复杂问题,为此自行设计了SDRAM控制器。SDRAM采取了8字节突发读写模式,工作于80MHz,工作时钟由FPGA的PLL倍频得到。SDRAM控制器包括:命令产生器" title="产生器">产生器、地址产生器、刷新定时器、仲裁电路等。SDRAM控制器实现对SDRAM的初始化,产生SDRAM存储器工作时所需要的各种时序信号。其中,命令产生器根据时序要求产生读、写、刷新、预充电、配置等命令;地址产生器产生SDRAM控制器所需的行地址和列地址;刷新定时器对SDRAM控制器进行定时刷新;当PCI读请求和刷新定时电路的刷新请求同时到达时,由仲裁电路对两者进行优先权判定。SDRAM控制器的时序状态图见图4。

4 数据采集卡配套软件的开发

数据采集系统应用于通用的计算机平台,其配套软件的开发要做到:设定16种参差模式(即在可变方位内设定采样频率和设定有效采样点数)、传达主机命令、返回板卡的配置和状态信息、按每一帧存储雷达数据等功能。采用PCI SDK软件开发包4.2版,在Windows XP下利用Visual C++开发驱动程序和相应的应用程序。PCI SDK软件开发包向用户提供自己的PCI产品的总线开发驱动程序。其中,将用到的开发驱动程序包括:PLX主机端API函数库、PLX器件驱动、用户API函数。使用PCI SDK可以很容易地执行DMA操作、访问IO端口和存储器空间、处理器中断以及访问PCI寄存器空间和LOCAL寄存器空间。这种易用性是通过开发者调用API来产生驱动程序代码。这样就不需要详细学习操作系统的内部原理和内核API(DDK),降低了开发难度。

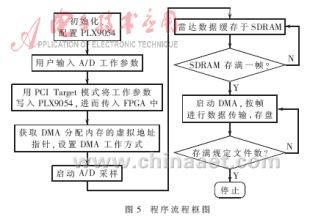

利用PCI SDK开发设备驱动程序的步骤如下:

(1)安装PCI SDK软件开发包。

(2)经过硬件调试,确认板卡设计正确后,将板卡插入PCI插槽,上电。系统显示发现新硬件,安装PLX9054.sys驱动文件。

(3)用Visual C++生成基于对话框的工程文件,将plxapi.lib以及其余所需的SDK提供的源文件和头文件加入工程。

(4)调用合适的API函数,并按照实际需要修改,编译并运行程序。

程序流程如图5所示。

采集的数据利用DMA方式传输到计算机内存,需要为DMA在计算机存储空间分配缓冲区,并且需要修改注册表,达到相应设置。

本文以16种可变参差工作模式为核心介绍了基于PCI总线的变参差工作雷达数据采集系统的硬件、软件设计方案。在FPGA逻辑控制下,系统能够对16种参差模式的雷达信号进行预置采样。PCI总线桥接芯片PLX9054功能强大、接口简洁,用户只需要关心Local总线接口电路的设计,使用方便。实验证明,在DMA方式的数据传输下,成功实现最高100MBps的雷达数据高速传输,解决了数据采集的瓶颈问题,使得系统可以满足实时性的要求。

参考文献

[1] 李贵山,戚德虎.PCI局部总线开发者指南.西安:西安电子科技大学出版社,1997.

[2] SHANLEY T,ANDERSON D.PCI系统结构.北京:电子工业出版社,2000.

[3] PCI9054 Data Book,Version 2.1.PLX Technology,2000.

[4] 夏宇闻.Verilog数字系统设计教程.北京:北京航空航天大学出版社,2003.

[5] 王诚,吴继华,范丽珍,等.Altera FPGA/CPLD 设计(基础篇).北京:人民邮电出版社,2005.

[6] 吴继华,王诚.Altera FPGA/CPLD设计(高级篇).北京:人民邮电出版社,2005.