基于DSP的声效处理器硬件设计与时序研究

2008-07-10

作者:战岳祥,宋占伟,徐 刚

摘 要: 针对特定环境(车内空间)内的声场重建,给出了声效处理器的硬件设计方案。以TI公司的数字信号处理器TMS320VC5402为硬件中心,对声音信号进行算法处理;串行16位模数转换芯片AD1870实现对音频信号" title="音频信号">音频信号的采集;串行数模转换" title="数模转换">数模转换芯片AD1858完成对处理后的音频信号的输出。详细叙述了TMS320VC5402和AD1870、AD1858之间的连接和时序。实验表明,此系统可靠、稳定,为完成音频信号的实时编解码提供了硬件支持,使在非规范空间播放高品质立体声音效成为可能。

关键词: 声场重建 声效处理 数字信号处理

随着现代科技的迅猛发展,立体声音频制作系统日臻完美,声场的信息几乎被全部收集。由于大部分放音声学环境不可能像录制环境那么完善,这些“声音画面”的恢复就成为研究的难点[1]。在大空间放音环境中(如露天环境),需要大量的放声设备来完成对声场的重建。因为这些设备占用了很多空间,阻碍了这种技术在小空间放音环境(如车内环境)下的应用。这些小空间放音环境的声场效果的采集、传输、恢复与重建是音频信号处理的研究热点[2]。从经过传输混叠的双声道信号重建模拟声效是电声技术的核心,本文据此设计了一种基于数字信号处理器(DSP)的音频实时处理的硬件系统[3-5]。本系统可以用来对立体声音频信号进行实时编解码与特定环境(车内空间)下声场效果重现处理,还可以用作同步的实时信号采集与处理。

1 声效处理器的DSP实现

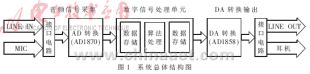

本系统由TMS320VC5402[6](以下简称C5402)芯片、闪存(Flash)、双通道随机存储器(DRAM)、模数转换电路、数模转换电路和电平转换芯片等组成。系统框图如图1所示。

由麦克或数据线传来模拟声音信号,首先经过ADC(AD1870)进行采集转换,转换后的数字音频信号通过串行方式传入DSP单元,DSP单元对接收的数字音频信号进行存储、运算、再存储等一系列处理,处理后的数字音频信号通过串口" title="串口">串口传给DAC(AD1858),AD1858完成对音频信号的恢复,把数字音频信号转换为模拟声音信号,DA转换后模拟声音信号通过接口电路传给耳机输出或通过数据线由放音设备输出。从而实现对音频信号的采集、传输、恢复与重建,完成了对声音效果的处理。

其中DSP芯片C5402具有100MIPS的运算速度,配有专用的硬件乘法-累加器,可以进行高速实时运算,为音频数字信号的实时编解码提供了高速、可靠的硬件基础;在对音频信号处理时会产成缓存数据,这些数据需要占有大量的存储空间,双口RAM则主要负责数据的存储;模数、数模转换的实现在本系统中选用的是AD公司的音频专用芯片:模数转换芯片AD1870、数模转换芯片AD1858。它们具有转换速度快、采样频率符合声音信号的要求、串行传输数据、无软件控制寄存器、操作简单等特点。

2 ADC、DAC与DSP的硬件连接与工作时序

DSP芯片C5402具有两个独立的多功能串口McBSP0、McBSP1,在此声效处理系统中被用来分别与AD1870和AD1858通信。下面详细介绍它们之间的连接和工作时序。

2.1 DSP串口与AD1870的连接

在本设计中,ADC与DSP以及DSP与DAC之间的通信采用的都是串行传输方式,C5402芯片内部集成了两个高速、双向、多通道带缓冲串行端口McBSP[7],每个串口提供了6个功能引脚和多个可程序读写的寄存器。C5402内部CPU通过对这些控制寄存器的读写完成数据的发送、接收以及对数据传输时序的控制。6个功能引脚分别为:

(1)接收、发送引脚DR、DX;

(2)接收、发送时钟引脚CLKR、CLKX;

(3)接收、发送帧同步引脚FSR、FSX。

AD1870[8]是一个基于Σ-Δ技术的高速串行16位模数转换芯片,主要用于双声道音频模拟量的采集。AD1870可以以48kHz、44.1kHz、32kHz等三种采样频率对音频模拟量进行采集。主要的引脚有:

(1)VINL、VINR——左右声道模拟声音信号的输入引脚;

(2)BCLK、L CLK——位时钟、左右时钟;

CLK——位时钟、左右时钟;

(3)WCLK——字时钟;

(4)SOUT——串行数据输出引脚;

(5)RDEDGE——读边沿的极性选择引脚;

(6) ——复位引脚。

——复位引脚。

其他的引脚还有:

(1)CLKIN为模数转换器AD1870的工作时钟输入端,fCLKIN=384×fS或者fCLKIN=256×fS;

(2)引脚384/ 用来选择采用上述两种模式的哪一种,如果384/

用来选择采用上述两种模式的哪一种,如果384/ =HI,则选用384模式;如果384/

=HI,则选用384模式;如果384/ =LO,则选用256模式;

=LO,则选用256模式;

(3)引脚S/ 、RLJUST、

、RLJUST、 用来设置AD1870数据传输模式,AD1870提供了8种数据传输模式,其中5种AD1870用做主设备,3种AD1870用做从设备。

用来设置AD1870数据传输模式,AD1870提供了8种数据传输模式,其中5种AD1870用做主设备,3种AD1870用做从设备。

结合本系统的应用,经过分析把AD1870作为从设备使用,它们之间的连接如图2所示。C5402的串口McBSP0用以和AD1870通信。C5402的主时钟输出引脚CLKOUT和AD1870的CLKIN引脚,这样由DSP处理单元向AD1870提供工作时钟。选用AD1870工作在从模式、32位数据传送格式[5],需要做如下设置:S/ =HI、LRJUST=LO、

=HI、LRJUST=LO、 =LO。在这种模式下,要求fLRJUST=fBCLK/32,即在两个左右时钟LRJUST脉冲之间位时钟BCLK要经历32个周期。每一位时钟BCLK周期时间传送一位数据,共传送32位数据,其中前16位为左声道的数据,后16位为右声道的数据。根据这种要求把C5402的BCLKXO、BCLKRO与AD1870的BCLK连在一起,由BCLKXO向BCLKRO和BCLK提供位时钟信号" title="时钟信号">时钟信号;把C5402的BFSX0、BFSR0与AD1870的LRCLK连在一起,由BFSX0向BFSR0和LRCLK提供频率为时钟信号频率的1/32的左右时钟信号;把C5402的BDR0和AD1870的SOUT连在一起,这样C5402就可以接收来自AD1870的数字音频信号了,C5402的接收数据引脚接收来自AD1870串行数据输出引脚输出的数字音频信号。为满足数据传输要求需要对McBSP0的串口寄存器进行设置,主要设置如下:

=LO。在这种模式下,要求fLRJUST=fBCLK/32,即在两个左右时钟LRJUST脉冲之间位时钟BCLK要经历32个周期。每一位时钟BCLK周期时间传送一位数据,共传送32位数据,其中前16位为左声道的数据,后16位为右声道的数据。根据这种要求把C5402的BCLKXO、BCLKRO与AD1870的BCLK连在一起,由BCLKXO向BCLKRO和BCLK提供位时钟信号" title="时钟信号">时钟信号;把C5402的BFSX0、BFSR0与AD1870的LRCLK连在一起,由BFSX0向BFSR0和LRCLK提供频率为时钟信号频率的1/32的左右时钟信号;把C5402的BDR0和AD1870的SOUT连在一起,这样C5402就可以接收来自AD1870的数字音频信号了,C5402的接收数据引脚接收来自AD1870串行数据输出引脚输出的数字音频信号。为满足数据传输要求需要对McBSP0的串口寄存器进行设置,主要设置如下:

(1)串口引脚控制寄存器PCR:FSXM(11)=1;FSRM(10)=0;CLKXM(9)=1;CLKRM(8)=0

(2)接收控制寄存器RCR1:RFRLEN1(14-8)=0000001;RWDLEN(7-5)=010。

在数据传送期间AD1870的字时钟WCLK一直输出高电平,据此把C5402的通用IO口 与它连在一起,用于DSP单元检测AD1870是否工作。另外,C5402的通用IO口XF与AD1870的

与它连在一起,用于DSP单元检测AD1870是否工作。另外,C5402的通用IO口XF与AD1870的 直接连接,这样就可以对AD1870进行软件复位操作。

直接连接,这样就可以对AD1870进行软件复位操作。

2.2 AD1870到C5402工作时序

从AD1870到TMS320VC5402的数据传输工作时序如图3所示。由图可知,在接电源后C5402通过主时钟输出引脚CLKOUT向AD1870的工作时钟输入引脚发送工作时钟,AD1870开始工作,把模拟信号转换为数字信号,即把左右声道模拟声音信号的输入引脚VINL、VINR采集来的模拟声音信号转换为数字音频信号。同时C5402的CPU通过对串口McBSP0寄存器的读写使串口McBSP0通过发送时钟引脚BCLX0向C5402的接收时钟引脚BCLR0和AD1870的位时钟引脚BCLK发送位时钟;通过发送帧同步引脚BFSX0向C5402的接收帧同步引脚BFSR0和AD1870的左右时钟引脚发送左右时钟。按照图3所示的时序数字音频信号由AD1870向DSP单元传送:在第一个左右时钟脉冲的触发下,第一帧数据开始向DSP单元传送,共32位数据。首先传送的是左声道的第一帧数据(16位);然后传送右声道的第一帧数据。接着出现第二个左右时钟脉冲,第二帧数据也是按照先前的顺序传入DSP单元。数据按照这种模式连续传向DSP单元。

2.3 DSP串口与AD1858的连接

在DSP单元处理好的音频数字信号需要经过数模转换,转换成模拟声音量输出。本系统选用的数模转换芯片是同为AD公司生产的AD1858数模转换芯片。AD1858[9]是一个双通道高速串行DA转换芯片,用于对数字音频信号的数模转换。主要引脚有:

(1)SDATA——串行输入引脚;

(2)BCLK、LRCLK——位时钟、左右时钟;

(3)MODE——输入串行数据模式控制;

(4) ——上电/复位引脚;

——上电/复位引脚;

(5)MUTE——利用此引脚可以控制数模转换通路的通和断;

(6)MCLK——主时钟输入;

(7)OUTL、OUTR——左右声道输出引脚;

(8)MCLK为数模转换器AD1858的工作时钟输入端,fMCLK=384×fS或者fMCLK= ×fS;

×fS;

(9)引脚384/256用来选择采用上述两种模式的哪一种。如果384/ =HI,选用384模式;如果384/256=LO,选用256模式;

=HI,选用384模式;如果384/256=LO,选用256模式;

(10)MODE用来设置AD1858数据接收模式,AD1858提供了二种数据传输模式。

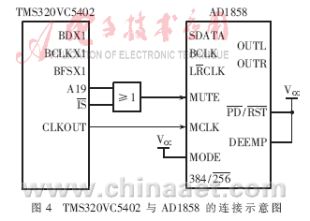

与C5402的连接如图4所示。由图可知,C5402的串口McBSP1用以和AD1858通信。C5402的主时钟输出引脚CLKOUT和AD1858的MCLK引脚,由DSP处理单元向AD1858提供工作时钟。将AD1858的引脚MODE接高电平,使AD1858工作在L-J DSP串行口模式[6]。这种工作模式要求fLRCLK≤fBLCK/16,即在两个LRCLK脉冲之间BCLK要经历多于16个周期。每一BCLK周期时间传送一位数据,共传送16位数据,在16位数据传送完后等待下一个帧脉冲。在第一个帧同步脉冲到来时,传送左声道的16位数据,下一个帧同步脉冲,传送右声道的16位数据,这样在LRCLK时钟的调节下依次轮流进行传送左右声道的数据。根据这种要求把C5402的BCLKX1与AD1858的BCLK连在一起,由BCLKX1向BCLK提供位时钟信号;把C5402的BFSX0与AD1858的LRCLK连在一起,由BFSX0向LRCLK提供频率为时钟信号频率1/16的左右时钟信号;把C5402的BDX1和AD1858的SDATA连在一起,这样C5402就可以把经过算法处理的数字音频信号传送给AD1858了。为了使数据传输需要对McBSP1的串口控制寄存器进行设置,设置如下:

(1)串口引脚控制寄存器PCR:FSXM(11)=1;CLKXM(9)=1;

(2)发送控制寄存器XCR1:XFRLEN1=0000000;XWDLEN1=010。

另外,C5402的A19、IS通过或门与AD1858的引脚MUTE连接,这样C5402就可以软件控制数模转换的开启与关闭了。

2.4 C5402到AD1858时序逻辑

由C5402到AD1858的工作时序如图5所示。由图可知,上电以后AD1858开始工作。DSP单元中处理好的音频数字量在时钟调节下向AD1858传送,在第一个左右时钟脉冲的的触发下,数据开始传送,AD1858根据左右时钟先接收左声道的一帧数据(16位)转化为模拟量由OUTL引脚输出;然后出现第二个左右脉冲,AD1858接着接收右声道的一帧数据,数模转换后由OUTR引脚输出模拟声音信号。接着出现第三个左右脉冲,第二帧左声道的数据也是按照先前的顺序传入AD1858进而进行数模转换,数模转换依次进行下去。

2.5 电平匹配

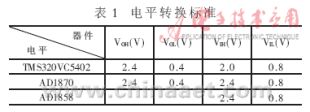

在设计DSP硬件系统时,由于DSP芯片C5402的I/O工作电压是3.3V,而ADC芯片AD1870和DAC芯片DA1858的工作电压却是5V,因此要分析它们之间的电平转换标准,以满足电压的兼容性和接口条件。电平转换标准从器件的电气特性中获得,如表1所示。

由表1可知,C5402与AD1870和AD1858的电平转换标准是一致的,因此从C5402到AD1870和AD1858的时钟、数据线可以直接连接。但是,由于C5402不能承受5V的电压,因此从AD1870到C5402的数据线不能直接相连,解决的办法是在它们之间加入一个3.3V电压供电并能承受5V电压的缓冲器SN74LVC245A[10]。SN74LVC245A有8路数据通道,引脚DIR用来控制数据的传输方向,SN74LVC245A的接口示意见图2,基本功能如表2所示。

3 工作流程

综上所述,系统上电后,AD1870启动开始模数转换,DSP单元开始向AD1870和AD1858输出时钟信号,由C5402的串口McBSP0向AD1870发送左右时钟信号,数据开始传输;根据位时钟的调节,AD1870连续向DSP单元传送数据,在DSP单元内数据经过缓存、算法处理,最后处理好的数据存在固定的数据空间;这时串口McBSP1向AD1858发送的左右时钟信号,信号启动向AD1858传输数据;同样根据串口McBSP1送给AD1858 BCLK的位时钟,AD1858连续接收DSP单元传过来的数据,进行数模转换,模拟声音量由引脚OUTL、OUTR输出。

该系统设计已通过实验运行验证,达到了相应的设计要求,可用于不规范空间声场效果的恢复。

参考文献

[1] 惠特克 J.C.数字音频技术宝典[M].北京:科学出版社,2004.

[2] 莫伟源.音响技术在汽车中的应用[J].音响技术,2006(1):68-69.

[3] 周霖.算法设计与系统方案[M].北京:国防工业出版社,2004.

[4] 王建平.基于DSP的多路音/视频采集处理系统设计[J].国外电子元器件,2006,(6):27-31.

[5] 刘耦耕.语音信号变速算法及其TMS320C5402实时实现[J].中南大学学报(自然科学版),2004,35(1):117-121.

[6] TMS320VC5402 fixed-point digital signal processor.Texas Instruments Incorporated,2000.

[7] 邹彦.DSP原理及应用[M].北京:电子工业出版社,2005.

[8] Single-Supply 16-Bit Σ-Δ Stereo ADC AD1870.Analog Device,Inc,2001.

[9] Stereo,Single Supply 16-,18- and 20-Bit Sigma-Delta DACs AD1857/AD1858.Analog Device,Inc,2001.

[10] SN74LVC245 Aoctal bus transceiver with 3-state outputs.Texas Instruments Incorporated,1998.