大规模SoC设计中的高效FPGA验证技术的研究与实现

2008-07-17

作者:丰玉田, 付宇卓, 赵 峰

摘 要: 一种针对大规模SoC设计的高效FPGA验证流程,分析了该流程所涉及的关键技术:通用硬件平台" title="硬件平台">硬件平台设计、FPGA软件环境设计和软硬件协同验证等。采用这些技术,FPGA平台可以快速且真实地模拟芯片应用平台,从而实现软硬件并行设计和协同验证。该验证流程已灵活应用于大规模SoC项目设计中,大大提高了SoC产品的研发效率。

关键词: SoC FPGA验证 软硬件协同验证

随着SoC(System on Chip)设计的规模不断扩大以及市场竞争日趋激烈,如何更快速设计出更高性能的SoC产品已经成为IC设计公司能否成功的关键。这其中,验证的工作量平均占据总设计工作量的80%甚至更多,对于一个大规模SoC系统,验证的效率和可靠性往往决定了项目的成败。

最常用的验证方法是通过软件仿真验证设计的功能,但由于软件仿真速度和仿真模型" title="仿真模型">仿真模型的局限性,验证往往难以达到令人满意的要求。而FPGA验证凭借速度和真实性的优势,已经成为VLSI设计中非常重要的环节。

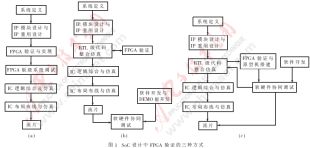

对于IC设计,一般来说有三种FPGA验证方式,如图1所示。

流程(a)只适用于结构简单且对设计周期要求不高的应用。IC设计经过简单的仿真即可尝试在FPGA上运行,若实现结果真实可靠,再进行IC后端设计,然后流片。但当芯片比较复杂时,在FPGA开发板上的调试将花费大量时间,且由于FPGA本身的局限性,并不能完美地验证SoC设计中的某些特殊任务,如低功耗设计、多时钟域交互、数模混和等。

对于大规模且有特殊设计要求的IC设计可采用流程(b),它要求建立一个完善的SoC软件仿真环境,IC设计的主要功能都可以在软件虚拟平台上得到比较全面的验证。之后再把SoC设计在FPGA平台上实现,凭借FPGA速度快和结果真实的优势,可在FPGA平台上运行大量的测试程序,以提高验证的完备性。但该流程要求花费很多经费和时间构建硬件平台,并且在验证过程中,研究如何产生激励和分析FPGA运行情况也将花费非常多的时间。考虑到项目周期和经费等因素,这种FPGA验证流程很难对SoC设计进行彻底的验证。同时,软件人员必须在流片后才能在真实的环境下调试应用程序,这也就增加了项目风险和研发周期。

随着市场竞争日趋激烈,SoC设计公司越来越需要找到一种更加完备的设计与验证方法来提高SoC设计的效率和可靠性,验证流程(c)则是最好的选择。它是一个可适应于各种项目的通用的FPGA硬件验证平台,不必经常重新设计硬件平台。该平台具有强大验证能力,可以非常真实地模拟各种SoC设计的功能和应用平台,从而可以对其进行全面的验证。该流程要求建立一个完善的FPGA综合与仿真环境,与IC设计的环境统一起来,使得任何一个仿真的激励都可以类比地在IC设计前端仿真、在IC后端仿真和在FPGA后端仿真。通过比较它们的结果,很容易地找到设计中的缺陷。这样,整个验证工作都将变得轻松而且透明。

在成功建立FPGA软硬件设计环境后,软件研发人员就可以并行的在该平台上开发和调试应用软件,并及时把系统级调试结果反馈到IC设计前端,这大大提高了研发效率,也非常全面地验证了整个IC设计。同时,还可以在FPGA中加入某些监测分析模块,真实地反馈芯片内部的运行数据,如处理器执行效率、总线利用率、带宽等,这些对SoC项目的决策都是至关重要的。

下面将详细阐述通用硬件平台建设、软件环境建设和软硬件协同验证等相关技术。

1 FPGA硬件平台建设

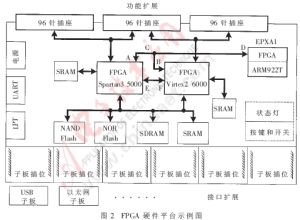

对于不同项目情况,FPGA硬件平台建设有所不同,但主要应考虑FPGA逻辑资源、应用资源、扩展能力、PCB信号质量、易于调试、组态和成本等方面因素。下面结合项目实例(图2)进行介绍。

1.1 FPGA逻辑资源

该硬件平台采用Xilinx公司FPGA芯片 virtex2 6000(X2V6000)和spartan3 5000(X3S5000)各一片,它们分别具有600万门和500万门的逻辑资源。virtex2 6000面向于高端应用,时钟和存储资源更多、速度更快,主要用于实现对性能要求较高的DSP内核;spartan3 5000具有更低的成本,用于实现对性能要求稍低的片上IP应用模块。该平台还包含一片Altera公司的FPGA芯片EPXA1,该芯片包含ARM922T硬核,它将保证该FPGA硬件平台能验证ARM+DSP等多核的SoC项目,也方便了验证和调试。

1.2 应用资源

为了能更广泛地适应SoC应用方案,两片大容量FPGA都各自与SRAM相连,以弥补片内RAM资源的不足。该硬件平台还包含一个公共存储器总线,用于连接常用的RAM和FLASH资源。这样硬件平台基本满足了SoC应用方案对存储资源的需求。

1.3 扩展能力

一个SoC的应用方案可能用到各种特殊的资源,通用的FPGA硬件平台应该能承载这些资源。示例中采用了两种扩展方式:一种是功能扩展,由三个96针的插座构成,它们与FPGA的距离近、延迟小、连接FPGA的I/O" title="I/O">I/O数量多,可用于连接功能扩展板,也可以通过该插座使两块FPGA板互连,使FPGA资源加倍,从而验证更大规模的SoC设计。另一种是接口扩展,用于扩展SoC的外设资源,如SoC中常用到的USB总线收发器、以太网控制器等,都可以单独作为子板来扩充,这些子板尺寸相同、引脚排列相似、且大多可采用两层板实现,即灵活又降低了风险和成本。

1.4 PCB信号质量

由于FPGA具有非常多的I/O资源,使得保证PCB信号质量成为难点。该硬件平台设计为14层板,采用Cadence公司的软件Allegro进行PCB设计,采用sigXplore进行信号完整性分析。对各种拓扑情况下的信号质量仿真表明,由于FPGA自带数控匹配电阻,两点互连线可以得到较好的信号质量,加大布线间距后,串扰也可以小到令人满意的水平,但连接多个器件的信号反射比较严重。对于公共存储器总线,布局时应尽量拉近芯片间的距离,并设置最大线长约束。当线长足够短时,经仿真,信号质量可以达到要求。对于三个FPGA间的互连线,由于线数非常多,很难全部缩短它们的长度,这时应设置布线约束,如图2,使AC与BC的距离相等,从而使A点和B点对C点的反射贡献相同,AD或BD可以得到较好的通信质量。然而AB间的通信质量却由于D点的反射而变得很差,但这两块FPGA间可以通过EF点来通信。这样,三片FPGA间的通信就都可获得较好的信号质量。

综上所述,FPGA硬件验证平台的搭建应根据项目情况有所不同,但所考虑的因素大体上可以分为以上四类,本文所提出的开发平台示例已经针对这四个方面提出了较好的解决方案,该硬件平台已成功应用于FPGA验证项目中。

2 FPGA软件环境建设

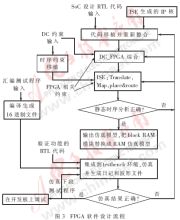

FPGA软件环境部分的工作,不仅包括对特殊的RTL代码及相关约束的修改,如门控" title="门控">门控时钟处理、硬IP核替换等,还要根据特定的硬件平台,增加FPGA相关的约束,并搭建一个能够自动仿真和验证的环境。因为在这一过程中RTL代码和约束要经过多次版本的变化,靠手工进行维护非常容易出错,这些错误很难检验,甚至可能损坏开发板。所以必须建立一个足够完善的软件环境,能够在人的稍微干预下,自动完成以上处理,并易于定位错误。图3所示是FPGA软件环境设计流程图,下面将分类介绍搭建软件环境的几个重要环节。

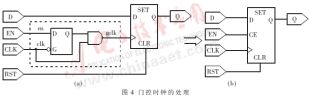

2.1 门控时钟的处理

在SoC的设计中,经常会用到门控时钟。如图4(a)所示,当en为‘1’时,时钟clk可传送到gclk;当en为‘0’时,gclk恒为‘0’。为了防止真实芯片中en和clk延迟差异可能造成的毛刺,该电路还需要一个latch锁住en的状态。对于SoC设计,使用者可以根据芯片使用情况把一些不用的模块的时钟关闭,这大大降低了芯片的功耗。

由于FPGA芯片特定的结构,它的全局时钟线数非常有限,并且经过与门输出的信号传输到全局时钟需要很大的额外延时,这使得图4(a)电路很难在FPGA中实现。通常的办法是,在FPGA中采用如图4(b)所示的电路来代替门控时钟的功能,该电路把源时钟clk和en信号分别接到每个触发器端。当en信号为‘0’时,clk信号虽不停止,但触发器并不触发,这使得该电路的功能与4(a)相同。该方法把芯片内的时钟线数大大缩小,使之可以采用全局时钟线布线,这充分利用了FPGA中全局时钟0偏斜的特点,避免了由于时钟线的延时所产生的时序问题,提高了系统的性能。目前,DC_FPGA综合工具可以支持门控时钟的自动处理,它要求把RTL代码中门控时钟单元改写成特定的风格,并增加几条约束语句,即可自动实现如图3所示的处理。该方法使时钟树非常复杂的SoC设计的FPGA验证变得简单,在实用中取得了非常好的效果。

2.2 硬IP核替换与RTL重新整合

在SoC设计中,经常会使用一些硬IP核,如PLL、SRAM、ADC、USB transceiver等,这些电路大部分属于模拟电路,无法在FPGA中实现。对于PLL、SRAM等模块,一般采用FPGA内部的时钟管理资源和存储资源来实现,只要在RTL调用关系上作些调整即可。对于其他硬IP核,需要在开发板上选用同样功能的芯片,与FPGA共同实现它们的功能。在RTL级,首先要取消对硬IP核的调用,然后在ISE软件约束中,把原先连接IP的信号绑定" title="绑定">绑定到FPGA的I/O上,并与功能芯片的特定信号相接。由于用于替换硬IP的资源很难做到在引脚和功能上完全一致,还需要根据具体情况对RTL代码稍作修改。

对于多FPGA验证,需要把SoC设计分成几个部分,分别在不同的FPGA上实现。这时主要应考虑FPGA资源的合理利用以及功能的完整性,让各个FPGA完成相对独立的功能,这将简化RTL代码的分割,也使调试工作变得相对容易。

2.3 约束的移植

在IC的后端设计中,需要加入很多时序、功能等约束,如最大时钟周期、false path、重命名等。这些约束在FPGA实现过程中也要求有效,但因FPGA工具软件约束语法不同,需要进行约束的移植。在汉芯的FPGA验证项目中,综合工具DC_FPGA与DC的约束语法兼容,可以直接采用DC的约束语句。DC_FPGA综合生成EDIF文件,在ISE下进行布局与布线操作,这时应采用perl语言把DC中的时序相关约束转换成ISE的约束,这种做法减少了人为错误,提高了执行效率。

另外,还要加入FPGA的相关约束,主要包括FPGA后端布局布线策略的设置、存储器初始化和I/O的绑定等约束。对于前两种,可根据项目的要求和ISE的语法加入适当约束即可。但对于I/O非常多的FPGA,I/O绑定约束靠手工维护很容易出错,而且如果绑定到错误的位置,有可能造成比较大的故障,甚至损坏硬件。这里建议在RTL级为每块FPGA写一个通用的顶层模块,信号的命名与原理图中一致,并在约束文件中绑定到正确位置,再由该顶层文件调用实际的SoC设计代码,这种做法将会大大降低版本变更中人为出错的可能。

2.4 自动仿真环境搭建

FPGA后端仿真对于检验FPGA操作流程中各个步骤的正确性是至关重要的一步,没有一个比较完善的后端仿真,SoC设计就很难成功地在FPGA平台上实现。在汉芯的项目中,RTL代码的前端仿真环境已经实现了激励的自动生成与结果的自动比对功能。如图3所示,验证人员把测试各个模块的汇编程序和RTL代码输入,仿真环境会自动编译程序并把生成的指令和数据初始化到RAM中,并开始仿真。在仿真过程中会自动把所要求的寄存器或RAM中的内容与正确的值相比较,并给出正确与否的结论,同时也会生成相应的波形和日记文件以供分析。对于FPGA后端仿真环境,应该具备前端仿真环境的验证功能,并且与前端仿真环境保持一致,这保证了同一个激励程序分别在前后端的环境下仿真,可以得到相同的结果。当出现不一致时,比较生成的波形就很容易定位FPGA后端操作中的问题。

基于上述分析,建立FPGA后端仿真环境首先要求在FPGA后端工作的每个步骤中,从层次结构、命名规则等方面都要与前端RTL代码保持一致,这可以通过工具软件中相应的约束来实现。另外,仿真中要求能把汇编程序下载到片内RAM中,而ISE软件生成的仿真模型中,片内RAM已经变成了由很多块block RAM拼成,对它们的初始化会很复杂。一个好的解决方案是在后端静态时序分析都正确的前提下,把ISE软件生成的仿真模型文件中的RAM替换成与前端仿真模型中的RAM相一致,这即保证了与前端一致,也方便了对其初始化和检测内容。

3 软硬件协同验证

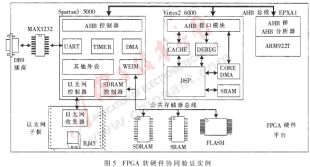

下面将结合项目实例介绍软硬件协同验证技术,如图5所示。该项目采用具有10级流水线的低功耗高性能DSP核,与ARM922T构成双核的SoC,面向移动平台应用。由于在仿真环境中难以对整个系统进行充分的分析和验证,故将该SoC在FPGA平台上实现。该平台通过以太网采用DMA方式把图像数据传给DSP,由DSP程序实现各种图像处理的算法,并把处理结果从以太网传回PC机,同时通过UART报告处理进度。利用该验证平台可实现如下任务。

3.1 系统验证

进一步验证在真实应用情况下整个SoC设计的功能的正确性。由于ARM具有一套完善的开发工具,可以非常容易地控制它产生激励并监测DSP和外围模块的运行情况。首先,通过ARM实现调试DSP的功能,在DSP内部加入DEBUG模块后,就可以通过它对DSP进行程序下载、单步、断点等功能调试。另外,还可以在ARM上运行测试程序,把系统运行到特定时间和步骤的执行结果提取出来并自动比较是否正确,然后把这些信息通过UART传到PC机,这将使整个系统的运行完全透明。

3.2 架构分析

对于一个SoC设计,架构的设计是至关重要的,它要求根据SoC具体应用情况对芯片的功耗、带宽、成本等多方面因素进行折中,超过实际需要的性能或带宽将会带来成本和功耗的增加,这些都将影响产品的市场竞争力。通过加入一些特定的分析监测模块,就可以在FPGA平台上更加容易地分析系统架构的性能。如图5所示,AHB分析器可以把AHB总线上的主从设备的切换频率和效率、最大总线利用率等细节情况真实地反馈到PC机,为SoC架构的分析提供非常真实的资料。

3.3 软件优化与分析

对于一个SoC平台系统,软件的设计与优化也是非常重要的。在FPGA平台上有上述提到的多种手段监控和分析软件运行情况,这样可以更好地优化软件,发挥SOC平台的最大潜力。还可以通过分析不同功能的应用软件对系统带宽和处理能力的真实需求,研究增加硬件协处理功能的可行性和必要性,做到真正的软硬件协同设计与验证。

上述SoC项目实例已在FPGA开发板上实现,成功地运行了小目标检测等多个图像处理程序,并实时反馈了DSP指令流水中断、DMA数据搬移、AHB总线竞争等许多芯片运行情况的信息。其中,基于对AHB总线竞争信息的分析,优化了软件的数据调度机制,同时改进了总线仲裁机制,切实地提高了AHB总线的数据吞吐率。

参考文献

1 Hauck S, Borriello G.Pin Assignment for Multi FPGA Sys-tems.IEEE Transactions on Computer-aided Design of Integ-rated Circuit and Systems, 1997;16(9)

2 Gschwind M. FPGA Prototyping of a RISC Processor Core for Embedded Applications. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2001;9(2)

3 Synopsys. Design Compiler FPGA user guide. CA: Synopsys Inc., Mar., 2004

4 Synopsys. VCS user guide. CA: Synopsys Inc., Sep., 2003