嵌入式计算机加密存储系统研究

2008-07-17

作者:黄君凯1,吴延军2

摘 要: Flash存储器有着功耗低、数据容量大、可整片擦除和分扇区擦除等优点,在嵌入式系统" title="嵌入式系统">嵌入式系统中得到了广泛的应用,但其中所存储程序代码容易被读取出来,易被非法拷贝,是其致命弱点。提出了一种加密技术,由PC机上运行的预加密软件" title="加密软件">加密软件和安全芯片" title="安全芯片">安全芯片两部分组成,可以有效地防范当前各种针对嵌入式计算机的软件程序的恶意窃取,牢牢锁住Flash存储器中的嵌入式软件" title="嵌入式软件">嵌入式软件和数据,使得知识窃贼无法得逞。

关键词: Flash 嵌入式系统 加密 Verilog

Flash作为当今嵌入式设备中的主流存储器件,有着极其广泛的应用前景,但它所存储的数据可以被轻易读取出来,很少有加密保护功能,成为制约其应用的致命缺点。当前针对Flash中数据进行加密的方法主要有两种,一种是对Flash中所存储的数据进行混乱加密,另一种是对Flash提供的器件唯一识别号进行加密。这两种加密方式都有着致命的缺陷,使用硬件总线侦听法和静态反汇编跟踪方法可以成功破解。针对这种现状,根据Flash技术的特点,本文设计一套完善的加密机制,提出一个系统化的解决方案,以此来有效地对抗现有的破解手段,从而大大增强嵌入式系统的安全性。

本文提出的Flash加密存储方案,独立于需要进行加密的嵌入式" title="的嵌入式">的嵌入式系统,它不改变嵌入式软件的功能和结构,不改变原程序和数据的组织方式,密文与明文数据量相同,无需增减原存储空间,无需功能性更改硬件电路。

1 加密存储方案构成

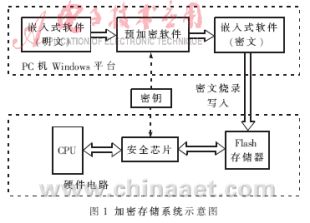

Flash加密存储方案由两部分构成:PC机上运行的预加密软件和硬件电路中隔离CPU与Flash存储器的安全芯片。预加密软件运行在PC机的Windows操作系统上,对嵌入式软件进行加密,生成密文形式的数据,并烧录写入Flash,供嵌入式系统使用。预加密软件完全独立于嵌入式软件,不改变嵌入式软件的任何功能和结构框架,仅使用密钥对其进行加密操作,生成密文形式的数据。安全芯片内嵌于嵌入式系统的硬件电路中,它跨接在CPU与Flash之间,隔离两端的数据总线、地址总线、控制总线,任何针对Flash的数据操作都要经过安全芯片的拦截过滤。Flash中的数据是以密文的方式存在的,在送给CPU执行之前,需由安全芯片解密;当CPU有数据需要存储于Flash时,安全芯片先对其进行加密,再送给Flash存储。整个加密体系如图1所示。

2 预加密软件设计

预加密软件运行在PC机的Windows操作系统上,它使用密钥,将明文形式的嵌入式软件加密成密文形式的数据,以二进制可烧录文件的形式写入Flash存储器。该软件在嵌入式软件烧录写入Flash芯片之前对其进行加密处理,所以称之为预加密软件。预加密软件不改变嵌入式软件的功能和结构框架,独立于嵌入式软件的开发,作为第三方软件加密解决方案提供给嵌入式微计算机的设计者使用。

预加密软件和安全芯片在时间使用顺序上和空间使用场合上都没有直接联系,密钥是它们之间唯一的逻辑纽带,使得预加密软件处理过的嵌入式软件和数据能够被安全芯片所识别,使得安全芯片动态加密写入Flash存储器中的数据和预加密软件处理过的已经存在于Flash存储器中的数据在格式与加密方式上保持一致。密钥以硬件电路的形式固化在安全芯片中,使得安全芯片与密钥一一对应。同样的安全芯片,因为密钥不同,不能相互替换,即便破译了安全芯片,但每一片安全芯片均采用不同的密钥,只能与预加密软件处理过的密钥一致的嵌入式软件配合使用,使得这种破译没有任何意义,从而保护Flash存储器中的嵌入式软件和数据不被窃取。

3 安全芯片设计

安全芯片处于CPU和Flash之间,如图2所示。它隔离CPU总线与Flash 的接入总线,控制Flash存储器的数据出入,任何对Flash存储器的数据读取和写入都要经过安全芯片的甄别和处理,确保Flash中的数据始终以密文形式存在。安全芯片同时加密地址总线和数据总线。数据操作满足可读可写,数据可在CPU与Flash间双向传输,CPU可在运行中写入、修改、删除Flash中密文数据,对特定密文数据的操作不影响其他密文数据的完整性。

3.1 安全芯片内部结构设计

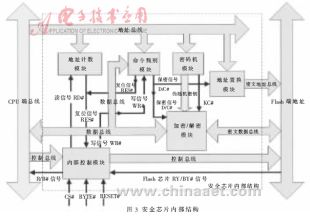

安全芯片内部由六个模块组成:地址计数模块、 命令甄别模块、密码机模块、地址置换模块、加密/解密模块、内部控制模块,如图3所示。

命令甄别模块负责区分Flash存储器的访问操作模式,若是数据访问,则通知加密/解密模块和地址置换模块进行加密操作。

密码机模块负责生成本文中的伪随机密钥,供加密/解密模块使用,以便有效抗击唯密文攻击方法和频率分析攻击。

当CPU读取Flash中的数据时,加密/解密模块使用密钥将密文数据解密成可执行的指令和运行所需的数据;当CPU写入数据进行存储时,加密/解密使用密钥对数据进行加密。

地址置换模块对数据的地址进行置换加密,使得原始的指令与数据所存储的地址变换为另一个地址。

地址计数模块用于抵抗来自CPU端的读取转存破解方法。

内部控制模块主要为其他各个模块提供控制信号。

当CPU读取Flash中的指令与数据时,安全芯片根据CPU的控制信号,读取Flash中的密文,使用与加密软件相同的密钥进行解密操作,生成明文后送给CPU;当需要写入Flash时,安全芯片使用密钥对该数据加密,再写入Flash。在没有安全芯片配合使用的情况下,读出Flash中的密文形式的嵌入式软件没有任何实际意义,既无法正确执行,也无法进行软件功能分析。当嵌入式系统有数据需要写入Flash存储器保存时,安全芯片在总线上截取这些数据,使用与预加密软件相同的密钥加密,送Flash存储器存储。

3.2 安全芯片设计实现

本文中设计的安全芯片使用Verilog语言进行功能仿真和功能验证,使用FPGA芯片进行硬件在板功能测试。安全芯片的硬件实现直接使用FPGA芯片作为硬件载体,由Verilog语言完成安全芯片的功能实现、仿真与验证。

Am29F160D是本文数据加密存储系统的Flash存储器设计蓝本, Am29F160D支持的最快总线读写速度为70ns,而其他的主流Flash存储器,如Intel公司的28F320J5,其总线读速度为120ns,写速度为150ns。考虑到当今嵌入式系统中,典型总线读写时钟频率为5MHz,兼容其他较为低速Flash存储器的总线速度,所以安全芯片的总线读写时钟频率取为5MHz,足以满足嵌入式微型计算机的数据读写速度。

本文所设计的嵌入式加密机制,已经成功地使用在某款车载GPS的设计中,取得了令人满意的效果。虽然加密和解密的过程降低嵌入式系统的运行速度,但随着硬件技术和软件设计技术的进步,以少量降低性能换取更高的安全性与稳定性是完全可以接受的,它在军事、通信、航天航空等高附加值的高科技嵌入式产品中,有着极为广阔的前景。

参考文献

[1] SUTTER E.嵌入式系统固件解密[M]. 张晓琳译. 北京:电子工业出版社,2003.

[2] 章照止.现代密码学基础[M].北京:北京邮电大学出版社.2004.

[3] FERGUSON N, SCHNEIER B. 密码学实践[M].北京:电子工业出版社,2005.

[4] GEE S. Basic methods of Cryptography[M]. Cambridge University Press,1998.

[5] MOLLIN R A. An introduction to cryptography [M]. Chapman&Hall/CRC Press, 2001.

[6] KOBLITZ N. A course in number theory and cryptography[M]. World Publishing Corp,1994.

[7] LUBY M. Pseudorandomness and cryptography applications[M]. Princeton University Press,1996.

[8] 郭春霞,裘雪红. 嵌入式系统安全的研究与设计[J]. 电子科技,2005,(8).