CPU寄存器集的实现方法与重叠寄存器窗口技术

2008-07-18

作者:刘 研

摘 要: 简要介绍了CPU通用寄存器" title="通用寄存器">通用寄存器及窗口技术" title="窗口技术">窗口技术的产生和发展背景,提出了以CALL和RETURN为代表的指令存在的问题,并给出了解决方法,讨论了大寄存器集及窗口技术的缺点和一些相关应用。

关键词: 寄存器 RISC MIPS 重叠寄存器窗口技术 CPU

CPU的通用寄存器是数据存储体系的最内层。寄存器操作避免了内存地址计算,其访问时间远小于Cache和主存。RISC MPU都具有较CISC大的寄存器集(Register file),而且都是LOAD/STORE体系结构,即所有运算的操作数都只针对寄存器中的数据施行,仅用LOAD/STORE类指令访问内存。从RISC CPU高速处理时间(单周期执行指令)的角度来看,这些主存访问是非常昂贵的开销。为了减少LOAD/STORE操作,使CPU与内存间的通讯量最小,不同的RISC体系结构采用了不同的寄存器集设计。从RISC早期开创性研究开始,就存在着两种不同的风格。

(1)Berkeley风格:在美国加州大学伯克利分校RISC I(1981)和RISC II(1983)项目中,CPU采用100个以上的寄存器,组成相互重叠的多寄存器窗口,用这种硬件结构实现寄存器的高效率使用。SUN SPARC是这种风格体系结构的典型范例。

(2)IBM/Stanford风格:在IBM 801(1975~1982)和斯坦福大学MIPS(1981~l983)项目中,体系结构设计人员(包括编译软件专家)采用非常高级、复杂的优化编译算法实现对寄存器的最佳分配。目前在这类设计中,以MIPS的优化编译软件及其配套的RISC R3000 CPU芯片最为典型,功能最强,发展最成熟。MIPS是高效精简指令集计算机(RISC)体系结构中最优雅的一种,即使是MIPS的竞争对手也这样认为。这可以从MIPS对于后来研制的新型体系结构,如DEC的Alpha和HP的Precision产生的强烈影响看出来。虽然自身的优雅设计并不能保证在充满竞争的市场上长盛不衰,但是MIPS微处理器却经常能在处理器的每个技术发展阶段保持速度最快的同时保持设计的简洁。

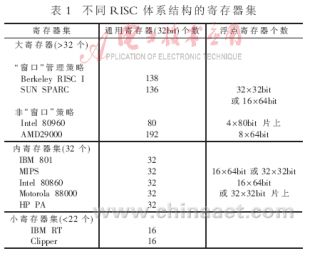

表1列出了不同RISC体系结构的寄存器集的寄存器个数,包括通用寄存器个数及浮点寄存器个数。

1 寄存器窗口技术

RISC的指令系统比较简单,CISC中的一条复杂指令,在RISC中通常要用一段子程序" title="子程序">子程序来实现。因此,RISC程序中的CALL和RETURN的子程序指令要比CISC程序中多。为了使CALL和RETURN操作尽量少地访问存储器,美国加洲大学伯克利分校的F.Baskett提出重叠寄存器窗口(Overlapping Register Window)技术,并且首先在RISC I上应用。重叠寄存器窗口的基本思想基于在处理机中设置一个数量比较大的寄存器堆,并把它划分成多个窗口。在RISC II中,寄存器的数量增加到138个。目前,重叠寄存器窗口技术已经成为RISC的一种基本技术。

RISC技术的主要设计技巧为:短周期时间;单周期执行指令;LOAD/STORE结构;简单固定格式的指令系统;不用微码技术;大寄存器堆;哈佛(Harvard)总线结构;高效的流水线操作;延迟转移;硬连线控制;重叠寄存器窗口技术;优化编译程序" title="编译程序">编译程序;增强存储管理功能;面向高级语言。

2 存在的问题

指令执行过程中,某些指令占据与其自身在程序中所占比例不相称的大量访存信息量。这一点,在CALL和RETURN指令上表现最为明显。

在执行CALL指令时,必须把硬件现场(主要包括程序计数器和处理机状态字)和程序本身的软件现场(主要指在子程序中要使用的通用寄存器等)保存到主存储器中。另外,还要把执行子程序所需要的参数从主程序传送过去。在执行RETURN指令时,要做相反的工作,最后把运算结果传送回主程序。因此,执行CALL和RETURN指令时,访问存储器的信息量非常大。据统计,在PASCAL语言和C语言中分别有15%和12%的CALL和RETURN指令,而它们访问存储器的信息量却占整个访存信息量的44%和45%。

3 问题解决

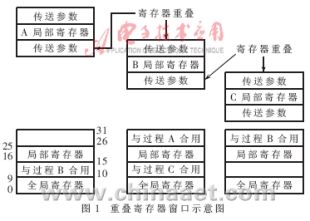

重叠寄存器窗口的基本思想:在处理机中设置一个数量比较大的寄存器堆,并把它划分成很多个窗口。每个过程使用其中相邻的三个窗口和一个公共窗口,而在这些窗口中有一个窗口是与前一个过程共用,还有一个窗口是与下一个过程共用的。与前一过程共用的窗口可以用来存放前一过程传送给本过程的参数,同时也存放本过程传送给前一过程的计算结果。同样,与下一过程共用窗口可以用来存放本过程传送给下一过程的参数和存放下一过程传送给本过程的计算结果。图1表现了重叠寄存器窗口的基本思想。

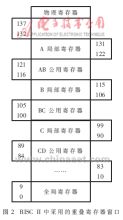

图2是RISC II中采用的重叠寄存器窗口,共有138个寄存器,分成17个窗口。其中,有一个由10个寄存器组成的窗口是全局窗口,能被所有过程访问;另外有8个窗口,每个窗口各10个寄存器,分别作为8个过程的局部寄存器;还有8个窗口,每个窗口各有6个寄存器,是相邻两个过程公用的,称为重叠寄存器窗口。每个过程均可以访问32个寄存器,其中,有10个是所有过程公用的全局寄存器,有10个是只供本过程使用的局部寄存器,有6个是与上一过程公用的寄存器,还有6个是与下一过程公用的寄存器。

只要调用的深度不超过规定的层数(如8层),重叠寄存器窗口技术可以减少大量的访存操作。当调用层数超过规定层数时,称为寄存器溢出,这时,可以在主存中开辟一个堆栈,把超过规定层数的寄存器中的内容压入堆栈中。

在SUN公司的SPARC处理机以及后来的Super SPARC和Utra SPARC处理机中,还把最后一个过程的公用寄存器与第一个过程的公用寄存器重叠起来,形成一个循环圈。在调用层数很多时,可以循环使用。

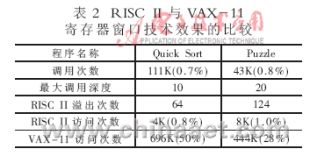

F.Baskett等人使用Quick sort和Puzzle两个程序对寄存器窗口技术的有效性进行了测试。Quick sort程序的特点是过程调用的次数在整个程序中所占的比例比较大,但调用的深度不大;而Puzzle程序正好相反。RISC II与VAX-11两种机器的比较结果如表2所示。RISC II的访存次数主要是寄存器窗口溢出引起的,而VAX-11访存次数是为了保持和恢复通用寄存器中内容而引起的。从表2可以看出,RISC II寄存器溢出的次数很少,只占千分之一左右,影响也不大。由于采用了寄存器窗口技术,由程序调用引起的访问存储器次数只占程序总访存次数的1%左右。

4 开销比较

表3是RISC II处理机与几种CISC处理机的每次过程调用的开销比较。从表3可以看出,在执行时间、执行指令条数、访问存储器次数等方面,采用重叠寄存器窗口技术都十分有效。

5 大寄存器集及窗口技术的缺点

大寄存器集及窗口技术在有效支持高级语言过程调用结构的同时,也不可避免地出现了一些缺点:

(1)窗口策略只是在比较理想的情况下,即嵌套深度在满足一定限制的时候才非常有效。

(2)对关联转换(Context Switch)时需将CPU寄存器存入内存的系统来说,大寄存器集的Save/Restore 需较长的时间才能完成,这直接影响多任务转换和中断响应时系统的响应速度, 而这对多用户系统和实时控制是非常关键的。

(3)对于采用流水线的结构处理器来说,指令译码是非常关键的一个功能段。RSIC MPU获得高处理速度的一个重要原因就是其极简单的指令格式、指令集和寻址方式带来了极快的指令译码时间。但采用大寄存器及窗口结构后就需要在指令译码通路中增加电路进行寄存器地址的译码,如选择当前窗口及窗口移动。特别是窗口指针需要计算,更增加了寄存器地址的译码时间,而且寄存器集越大,寄存器地址译码硬件也越复杂,对每一个寄存器的访问时间也越长,由此在指令流水线译码段内引起的时间延迟对系统整体性能的影响也越大(如目前采用寄存器窗口的体系结构都很难实现快速LOAD/STORE指令,需要两个或更多的周期)。若像SPARC那样窗口大小固定,则所需译码和加法器电路还较简单,由此引起的附加延迟也较小,系统性能所受影响也不大(但另一方面窗口较大和窗口个数较少,使窗口上溢" title="上溢">上溢次数和每次上溢后所需保存寄存器的数目都增加了)。

若像AMD29000那样采用可变大小的寄存器窗口, 则对于把窗口上溢次数和上溢后需要保存寄存器的个数减至最少非常有利,但却必须在指令译码通路中采用更复杂的电路,这最终可能导致指令译码时间成为制约处理器芯片采用更高时钟频率的瓶颈。

(4)大寄存器集及窗口结构需占用较大的CPU芯片面积,限制在片上实现其他关键硬件。

6 当前寄存器窗口技术的一些应用

高效的函数调用:大多数RSIC处理器的函数调用需要卸出和重新装入寄存器,开销很大。IA-64增加了一个通用寄存器窗来支持高效的函数调用。这个128项的通用寄存器窗口被分为一个32项的全程存储器和一个96项的堆栈存储器。IA-64允许编译程序在被调用的函数过程入口设置一条ALLOC指令,创立一个最多包含96项的新寄存器堆栈;在返回时,恢复调用程序的寄存器堆栈帧。对编译程序来说,似乎有长度无限的物理寄存器堆栈,从而降低了函数调用的开支、提高了效率;如果在调用和返回时,没有足够的寄存器可供使用(堆栈溢出),则处理器将被阻塞,等待卸出和装入寄存器,直到有足够的寄存器为止。

参考文献

[1] 白中英,杨旭东.计算机系统结构(第2版).北京:科学出版社,2004.

[2] 郑纬民,汤志忠.计算机组成原理.北京:清华大学出版社,2004.

[3] 张晨曦.计算机体系结构.北京:高等教育出版社,2003.

[4] Dominic Sweetman.MIPS处理器设计透视See MIPS Run.北京:北京航空航天大学出版社,2005.