采用双体DMA的无线NIC收发器的核心模块设计

2008-07-21

作者:张明武, 刘才兴

摘 要: 介绍了一种无线网络接口卡的核心硬件模块的实现原理,通过双DMA实现对无线网络数据的快速收发。对NIC接收模块" title="接收模块">接收模块和发送模块" title="发送模块">发送模块的硬件实现电路作出了详细分析。

关键词: 收发器" title="收发器">收发器 无线网络 DMA 曼彻斯特编码 DP8391

随着无线通信技术的不断成熟和应用,各种各样的智能化和网络化的无线通信产品不断涌现,无线网络产品也得到飞速发展。无线网络接口卡收发器作为无线网络的重要组成部分,为可靠的无线传输提供重要的硬件接口及物理层和数据链路层的协议支撑。

本文详细分析10Mbps无线网络接口卡的核心——收发器的设计过程中的问题,提出无线网络接口卡NIC实现方案,并对其核心的发送和接收模块电路作出分析和探讨。

1 无线NIC总体实现方案

无线NIC的基本结构如图1。它主要由三部分组成,即数据链路控制器、Manchester代码转换器和无线收发电路。链路控制器采用DP8390,以实现数据层路层协议的控制,NIC中设计了8K×2bits的RAM作为网卡的缓冲区,以提高系统的执行速度。系统采用PCI总线与主机相连[1]。为了与以太网卡兼容,设计中增加了PROM自举电路模块[2]。

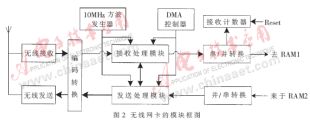

内部硬件基本模块如图2。它主要由无线收发模块、编码转换模块、接收处理模块" title="处理模块">处理模块、发送处理模块、DMA控制器模块、串并转换模块等组成。系统时钟统一采用10MHz方波发生器的时钟[3~4],以进行数据帧的同步。

2 收发器模块设计" title="模块设计">模块设计

2.1发送模块设计

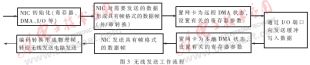

发送模块通过DMA方式读取RAM中的数据并将数据交给无线发送模块进行发送[5],其工作过程如图3。网卡向无线网络发送数据过程如下:

(1)NIC初始化。计算机对NIC中各寄存器的读写是利用主机的I/O方式,网卡的基地址一般为300H。初始化NIC实际上是利用OUT指令对NIC中有关的寄存器写控制字。

(2)微机与网卡中缓冲RAM交换数据是使用NIC远程DMA模式。开动远程DMA后,微机不断读写网卡的数据端口,就能成功地执行远程DMA过程,完成微机与网卡中缓冲RAM的数据交换。

(3)缓冲RAM收发网上的数据使用NIC的本地DMA模式。当初始化过程后,网卡处在接收状态,一旦接收网上来的数据,就自动执行本地DMA过程,对缓冲RAM进行本地DMA写。

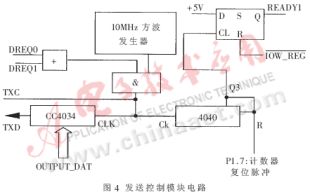

发送电路模块的设计原理图如图4。发送模块主要由10MHz标准方波发生器、一个D触发器、4034并/串双向移位寄存器、一个4040计数器和两个双端与门。

10MHz标准方波发生器用于产生10MHz标准方波,提供发送数据的时钟信息。4040用于发送位计数。在发送完一个字节后,4040用其Q3送出完成信号,在D触发器中锁存,即生成字节转换完毕信号,允许送出下一字节;待接收到第二字节后,复位D触发器,重复前述过程。4034在10MHz脉冲控制下,将数据总线上的并行数据转换成10MHz的串行数据发往曼彻斯特编码器。

图4中P1.7为计数器的初始复位信号线,由其在发送开始、全部发送完成以及发送未完中断后发出复位脉冲。发送未完中断是用来处理发送过程中在同轴电缆上的冲突,此时将终止当前发送。D触发器用来锁存计数器4040的Q3输出端状态,告知CPU此时外设已准备就绪。

2.2 接收模块设计

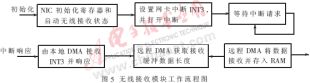

接收模块由初始化模块和接收中断模块两部分组成。初始化模块完成对NIC寄存器的初始化,并对网卡中断INT3和DMA参数进行初始化,等待中断。

当网络有数据需要接收时,引发网卡中断INT3,接收处理模块通过DMA与RAM进行数据传送。这种不需要CPU干预的、成批量的数据传送,可以极大地提高数据的接收速度。

接收处理模块完成数据帧的处理(主要是以太帧),判断是控制帧还是数据帧,并进行帧的校验,利用串并转换模块转换成并行数据[6]。主要功能如下:

(1)远程DMA读过程设置在微机的中断子程序中,本地DMA写完成后,中断微机主程序,执行远程DMA,完成微机接收数据过程。微机发送过程是由微机一方先执行远程DMA写,然后执行本地DMA读。

(2)如果是发送数据,则发送模块完成与接收模块相反的过程。不过,发送时还要判断能否发送,即用改进冲突检测方式进行冲突检测。由于无线传输无法进行载波侦听,只能利用接收方是否忙判断线路状态,用软件实现。接收处理模块的执行过程如图5。

2.3 编码转换、计数部件与时钟

编码转换环节主要用于将接收来的信号通过曼彻斯特编码器DP8391进行解码,产生相应的数据流,并进行同步的帧头与校验判断,进行锁存,产生10MHz串行位流,并将之转换成并行数据字节流,交给接收模块,送入缓冲区。在发送时,其过程与接收过程相反。编码器与计数器配合使用,对发送和接收到的数据进行计数。

2.3.1 编码转换

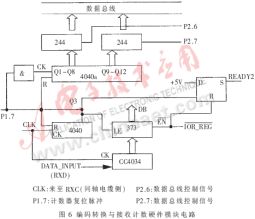

编码模块连接DP8391,其主要包括4034串/并双向移位寄存器、373三态锁存器、两片4040计数器、两片244 三态缓冲器及一片D触发器,其硬件原理图如图6所示。

4034作为串/并转换器件,其输入信号取自DP8391 RXD端,373用于转换之后的并行数据的缓冲与锁存,然后将它们送至数据总线上。4034时钟信号来自DP8391的RXC端,另外用一片4040对输入数据位进行计数,取完8bit后,其Q3脚输出一脉冲给D触发器和字节计数器4040a,D触发器收到信号后则发出READY2信号,告知其一字节转换完成,可从373 上取走数据。在取走数据后,通过D触发器异步复位端复位触发器状态。

2.3.2 计数器部件

接收计数器是对接收到的数据字节进行计数,它主要由4040a实现,其输入是4040的Q3,输出则通过两片244 接入数据总线,不破坏总线上的其他数据。一个计数器实现数据帧的提取,形成一个完整的字节。另一个计数器用于对接收的字符个数进行计数。

2.3.3 恢复时钟

恢复时钟REC功能用一个片内锁相环完成。恢复时钟用来监测串行数据输入信号的完整性。如果接收到的串行数据不符合频率要求,电路将强行锁定局部参考时钟INT,使系统在数据或原锁定丢失时仍能得到正确的恢复时钟频率。如果这个恢复时钟频率与局部参考时钟频率的偏离量大于50ppm,将通知锁定输出,同时电路将作出反应并努力将输入数据流拉回到锁定数据中。

无线网络在许多场合作为有线网络的替代,如野外联网作业及只需短期临时的通信场合,都有很好的应用前景。本课题设计的无线网卡,能有效地应用于无线网络。

本无线网卡,对于网络终端的快速移动产生的网络信号接入与识别的误码率还比较高,有待于进一步解决;对于静止的终端,其通信速度较快、误码率很低。

参考文献

1 Walter A.Tribel.16-bit Microprocessor Architecture, software,and Interface Techniques[M]. New Jersey: Prentice-Hall, Inc. 1988

2 Ethernet/Cheapernet Physical Layer Made Easy with DP8391/92. National Semiconductor Application [EB/OL]. http://www.nalanda.nitc.ac.in /industry/appnotes/ Natsemi/AN-442. pdf

3 黄振海, 李建东,刘乃安等. 宽带无线IP网卡的研究和实现[J]. 西安电子科技大学学报,2002;(4)

4 吴光荣, 郭峰,刘乃安.无线网卡微波收发机设计[J].西安电子科技大学学报,1999;(1)

5 王福勋. 单片蓝牙控制器AT76C551[J].半导体技术,2002;(4)

6 PCI SIG. PCI Local Bus Specification Revision 2.2[S]. PCI Special Interest Group,1998;(12):21~105