一款集成HUB的USB设备控制器的设计

2008-07-22

作者:杨存永, 詹克团, 杨 英,

摘 要: 介绍了USB设备控制器" title="设备控制器">设备控制器的基本功能和原理,提出了一款基于6502MCU的通用的带HUB的全速USB设备控制器的体系结构,并完成了整个芯片的设计,而且通过了FPGA验证。这款芯片可以用来开发带HUB的全速USB设备、全速USB设备或全速USB HUB。

关键词: USB HUB SIE 转发器 FPGA

近年来,USB技术已经成为计算机领域发展最快的技术之一,得到了广泛的应用。早在1998年,由于USB1.1规范的推出以及Windows98加强了对USB的支持,USB就得到了飞速的发展和普及,各种USB设备不断涌现。2000年,USB2.0规范推出之后,USB一改只能适用于中低速设备的局面,在高速传输领域也占领了大量的市场份额。2001年推出的USB-OTG解决了大量USB设备之间的直接互连问题,因此USB规范将得到更加迅速的发展。

根据USB规范,USB系统的拓扑结构呈金字塔状,集线器(HUB)是金字塔中不可或缺的部件,是主机与设备之间建立连接的桥梁。根据USB2.0规范,全速USB HUB可以连接低速、全速和高速下行设备(高速设备降为全速运行)。

本文提出一款基于6502 MCU的通用的带HUB的全速USB设备控制器的体系结构,并完成整个芯片的设计。这款芯片可以用来开发带HUB的全速USB设备、全速USB设备和全速USB HUB。

1 系统设计

常见的USB设备控制器的功能结构框图如图1所示。收发器" title="收发器">收发器用于实现物理层的USB规范,它包含一个接收器和一个发送器,接收器用于接收和判决总线D+、D-的信号,发送器用于驱动D+、D-的信号。串行接口引擎(SIE)主要用于解析协议层的USB规范,如时钟提取、NRZI编码/解码、比特填充/抽取、CRC校验、PID检测/产生、串并/并串转换等。功能控制器主要用于处理功能层的USB规范。缓冲区是功能控制器与SIE互相通信的桥梁,通常SIE把总线上接收到的数据存放在缓冲区中,供功能控制器读取并解析;同时,功能控制器又会把需要发送的数据存放在缓冲区中,供SIE读取并发送。

集成HUB的USB设备控制器又称为复合设备控制器,它在本质上是两个USB设备,在系统中拥有两个不同的设备地址。因为USB是分时复用的串行总线,在正常情况下,任何时候主机都只能与系统中的某一个设备进行通信,所以复合设备控制器也可以把设备控制器和HUB控制器的很多部件合二为一,分时复用。

本文提出的集成HUB的全速USB设备控制器的设计方案如图2所示。该控制器支持一个上行端口和四个下行端口,并实现了USB键盘的功能。SIE主要负责物理层和协议层的协议解析,MCU主要负责设备层的协议解析,缓冲区是SIE和MCU之间通信的桥梁,SIE把接收到的数据包存放在缓冲区中供MCU读取,MCU把需要发送的数据存放在缓冲区中供SIE读取。数据转发功能主要由HUB 转发器实现。

2 SIE设计

在USB HUB内部需要有一个全速SIE用来处理USB规范第八章规定的大部分协议,它的主要功能包括:

·包的识别与组织;

·时钟与数据分离;

·NRZI编码和解码;

·比特填充和提取;

·CRC校验码的识别和产生;

·地址检测;

·PID检测和产生;

·串/并转换和并/串转换。

在设计SIE的时候,根据它的功能又将其分成几个不同的模块,如图3所示。PHY模块主要完成数据的串/并转换和并/串转换、比特填充和提取、NRZI编码和解码、时钟与数据的分离等功能,此模块内部数据主要以串行状态存在。PL模块负责数据包的解析与组织、PID检测和产生、CRC检验码的识别和产生、地址检测等功能。FUNCTION模块完成SIE与MCU的接口逻辑功能。

3 转发器设计

转发器是HUB实现数据转发功能的核心模块。转发器实现的功能主要有:数据转发、帧同步、挂起唤醒处理、总线冲突检测与解决、往低速下行端口发送Keep-alive等。

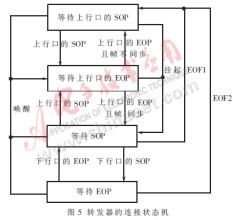

在设计转发器的时候,根据数据的流向对转发器进行了进一步的模块细分,如图4所示。hub_up模块负责接收来自上行端口的信号,并检测出SOP和EOP;同时转发来自内部端口和下行端口的信号。hub_dp模块包含四个子模块,支持四个下行端口,负责接收来自下行端口的信号,并检测出SOP和EOP;同时往下行设备转发合法的下行数据。rpt_engine模块中有一个重要的连接状态机,其状态转换如图5所示,它以数据包为单位控制上行端口和下行端口之间的连接的建立和拆除,同时控制集线器正确地挂起和唤醒。

在图5所示的连接状态机中,状态跳转主要通过SOP(包开始)和EOP(包结束)信号实现,所以SOP和EOP信号直接影响状态机的正确跳转,从而影响了转发器的稳定性。检测SOP信号时要考虑两个重要的因素:首先,SOP信号要产生得尽可能快,从而可以较快地打开数据通道,减小数据流中SYNC的损失;其次,检测与本地时钟异步的数据流而产生的SOP信号要与本地时钟同步,否则会使寄存器建立时间和保持时间得不到满足。检测EOP信号时也要考虑两个因素:首先,要排除长度不够的SE0的干扰和SE0状态向J状态跳变的抖动干扰;其次,EOP信号也要与本地时钟同步。

全速HUB的上行端口始终是一个全速连接,但是它的下行端口可能是全速连接也可能是低速连接。低速数据经过上行端口时,虽然它的速率是低速的,但是它的极性却是全速的。全速数据的极性与低速数据的极性是相反的,所以转发低速数据时需要先对数据的极性进行转换。HUB在转发数据的时候需要遵循以下原则:来自上行端口的低速数据广播给所有处于允许状态的下行设备(包括全速设备和低速设备);来自上行端口的全速数据转发给所有处于允许状态的全速下行设备。

4 固件" title="固件">固件设计

本文提出的USB设备控制器是一个软硬件结合的系统,即整个系统由MCU、SIE、转发器等硬件和运行于MCU中的固件组成。

系统的设计原则是:凡是固件能够完成的任务尽量由固件来实现,硬件的主要工作是对协议层的解析,解析完之后会设置某些控制寄存器,有时会产生中断,固件通过查询这些寄存器执行相应的操作。

为了验证整个系统,通过编写固件实现集成HUB的USB键盘的功能。

5 对于异步信号的处理

USB属于异步总线,本地时钟和主机时钟是由两个不同的晶振产生的,所以SIE必须采用适当的方法实现位同步" title="位同步">位同步。一个典型的位同步方法就是采用一种特定结构的数字锁相环[1]。其原理是:分别用本地48MHz时钟的正负沿采样接收到的12MHz数据流,再用采样后的信号控制状态机的跳转并产生12MHz的位接收时钟(它的有效沿位于12MHz数据流每个比特位的中间),然后用新产生的时钟去采样12MHz的数据流从而实现位同步。

整个系统中采用的是异步复位" title="异步复位">异步复位。异步复位的好处是可以保证系统在初始状态时处于已知的状态,对于有三态总线的系统来说,这是非常重要的[2]。异步复位的处理非常重要,关系到系统的稳定性。对于异步复位信号来说,重要的不是什么时候复位而是什么时候复位结束,异步复位有两个关键的参数恢复时间和迁移时间,如图6所示[3]。如果以上两个参数不满足,就会产生亚稳态[4]。为了解决这个问题,设计了如图7所示的复位电路。

在该电路中,复位的产生是不受时钟控制的,但复位结束是受时钟控制的。之所以要用两个级联的触发器,是为了避免第一级触发器有可能产生的亚稳态传给整个芯片的复位信号reset。在这个电路中不存在恢复时间的问题,因为复位结束肯定在时钟沿的后面。迁移时间的问题也可以解决,只要Tclk_q (clock to Q)+ Tpd(复位信号的传输延时) > Trem(触发器的迁移时间)即可。对于上电复位来说还要进行进一步的处理,要保证复位时间足够长,因为电源稳定需要一定的时间。

6 设备的低功耗设计

对于USB设备来说,当总线上超过3ms没有总线活动时,设备就要自动进入休眠状态,此时从总线上获得的电流不能超过500μA[5]。为了满足此要求,设计了如图8所示的设备唤醒和休眠电路。

当设备需要休眠时,给出一个sleep信号控制晶体振荡器(OSC)停止振荡,整个设备进入节电模式。对于CMOS电路来说,时钟停止振荡以后所消耗的功率极小,当有总线活动时,收发器会产生总线活动标志信号wakeup,wakeup信号首先控制振荡器重新开始振荡,然后和clkDelay信号一块控制设备的时钟(Clock),晶振稳定后则输出时钟信号。复位时不对时钟信号进行控制。

7 FPGA实现和系统验证

系统进行实现和验证时,串行接口引擎和转发器采用Verilog进行RTL描述,然后采用Xilinx公司的XC2S200PQ208 FPGA实现。缓冲区和RAM由FPGA内部集成的RAM实现,收发器采用Philips公司的PDIUSBP11A,MCU采用MICETEK公司的65C02仿真器。

整个系统经验证后,工作正常,内置键盘可以正常工作,在下行端口插入低速USB设备和全速USB设备都可以工作。图9是用立肯科技公司的USBMobile测试仪对FPGA系统进行测试的结果的一部分。

参考文献

1 Designing a Robust USB Serial Interface Engine(SIE). USB-IF.http://www.usb.org/developers/whitepapers/

2 Michael Keating, Pierre Bricaud. Reuse Methodology Manual for System-on-a-Chip Designs. Kluwer Academic Publishers,2000

3 Design Compiler Manual. Synopsys Corp., 2003

4 Mike Stein.跨越鸿沟:同步世界中的异步信号.EDN电子设计技术,2004 (7)

5 Universal Serial Bus Specification 1.1. Compaq, Intel, Mi-crosoft, NEC,1998-09-23