一种提高STN型单色点阵液晶显示器灰度级数的算法

2008-07-28

作者:曹志香

摘 要: 根据图像的分解、传送、合成的原理以及STN型单色点阵液晶显示器件的灰度显示机理,提出了一种既能减小芯片面积、降低功耗又能提高灰度级数的多公式算法;利用Verilog HDL语言工具完成了灰度控制模块" title="控制模块">控制模块的设计;利用SYNOPSYS公司的EDA工具对该灰度控制模块进行了仿真、综合,并在FPGA上进行了验证。

关键词: 灰度 公式算法 模块设计 FPGA

由于人眼能区分光信号的强弱明暗,所以要获得优良的显示效果,必须实现灰度显示。特别是在图像方面,灰度级数越多,图像层次越分明,图像越柔和。液晶显示器作为一种显示器件,总是希望它能显示生动逼真且稳定无闪烁的图像,所以灰度的表达对于液晶显示器来说是极其重要的。嵌入式系统要求整个芯片面积和功耗越小越好,并能实现集成化。因此,在支持液晶显示板的嵌入式LCD控制器中,如何实现灰度控制并有效地降低整个芯片面积和功耗、降低信号损失、提高画质是IC设计者的一个研究热点。

本文首先根据STN型单色点阵液晶显示器件的灰度显示机理并利用相邻像素的通、断进行控制的规则,提出一种基于面积-帧调制的公式算法,从而利用多个公式达到减小芯片面积、降低功耗、降低成本、提高灰度级别、消除图像闪烁的目的;然后利用Verilog HDL语言工具编写RTL级代码,完成灰度控制模块的设计;最后对该模块进行仿真、综合,并在FPGA上进行验证。

1 灰度公式算法的提出

我们知道,从图像到显示屏的显示过程一般分为分解、传送与合成三个过程[1]。也就是首先把整个画面分解成许多黑白程度(亮度)不同的小点,即“像素”,它们具有单值的光特性(亮度)和几何位置(x,y);然后利用人眼视觉特性,采用扫描方法,按时间顺序逐一传送空间分布的每一像素的亮度;最后再将各个像素合成为整个画面。只要确保发送端坐标与接收端坐标(x,y)的一一对应关系,就可以使被传送的图像不失真。可见,这里所说的像素亮度实际上是(x,y,t)的函数,t代表传送时间。

STN型单色点阵液晶显示器件采用的是一种无源矩阵型结构[2],其数据位列选择信号是处于锁定状态的二值(黑、白)信号,即所写入的灰度图像显示数据是用“1”(选通为黑)和“0”(非选通为白)表示的脉冲信号。一个像素点的亮度是由若干帧选通该点的次数决定的,选通次数越多,该像素点越亮,否则就越暗。因此,只要在若干帧内该像素点被选通的次数一定,不管选通和非选通的次序(即“1”和“0”的输出顺序)如何,它们的亮度是一致的。由于点阵式液晶显示屏上相邻像素之间相互有影响,而图像稳定与否又与各像素点之间能否有效配合密不可分,这就要求尽可能地使得空间上相邻像素的激发随时间扩散,而同一时刻激发的像素在空间上又能扩散。为了实现整幅画面的灰度显示效果,若从整幅画面考虑,势必增加控制难度,因为一幅画可能由几千、几万乃至几百万个像素组成。如果将显示区域按事先预定的大小划分成块,对每个方阵采用相同的控制规则,那么对整幅画面的控制将转化为对一个方阵的控制,这样可以大大降低对各像素点的控制难度。本文以16级灰度为例,将显示区域划分成15×15的方阵,以15帧为一循环周期,将16种亮度在单位时间内的脉冲输出次序用0、1、2、...的顺序标注,如表1所示。

16级灰度的原始图像数据" title="图像数据">图像数据信号被划分为四组:

数据信号Ⅰ(0000 1111),

数据信号Ⅱ(0101 0110 0111 1000 1001 1010),

数据信号Ⅲ(0011 0100 1011 1100),

数据信号Ⅳ(0001 0010 1101 1110)。

对于数据信号Ⅰ,所有15帧中的相应点都置成“0”或“1”。

对于数据信号Ⅱ,脉冲序列值的计算公式如下:

k=mod[(c+r+f)/15](1)

对于数据信号Ⅲ,脉冲序列值的计算公式如下:

k=mod[(2c+r+f)/15](2)

对于数据信号Ⅳ,脉冲序列值的计算公式如下:

k=mod[(4c+r+2f)/15](3)

式中,c、r表示方阵中像素的几何位置(c=0,1,2,...,14;r=0,1,2,...,14),f表示单位时间内所处的帧数(f=0,1,2,...,14),mod表示取余运算,k表示脉冲序列值(k=0,1,2,...,14)。根据公式算出的脉冲序列值和代表亮度的图像数据,可从查找表" title="查找表">查找表(表1)上确定任何一个像素在任何时刻的选通情况。在这些公式中,(c,r)反映的是面积灰度调制,同一帧中不同的像素有不同的k值;而f反映的是帧灰度调制,某一个像素的f值变化时,其k值也在变化,且在一个单位时间内其k值不重复。因此,这种公式算法使得各像素在时间上有累加的效果,同时还可利用分散激活产生半色调像素点来增加像素明暗变化率,从而使原始图像在进行灰度调制时能够得到稳定的显示。

2 灰度控制模块设计

灰度控制模块主要控制像素灰度数据的输出,一方面要保证LCD显示器件上每个像素的几何位置要与原始画面上的每个像素的几何位置一一对应,另一方面要保证在一定帧数之内能够输出表示原始像素数据所要表示的灰度效果。

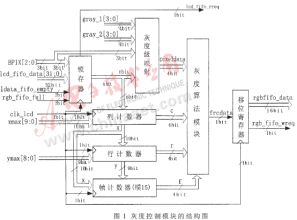

公式(1)、(2)、(3)中有三个参数:c、r、f,在灰度控制模块中可以采用三个计数器(列计数器、行计数器和帧计数器)来实现。前两个计数器完成显示区域的划分工作,同时产生c、r值。而帧计数器用于产生f值,然后根据这三个计数器的值计算出各像素点在任何时刻的脉冲序列值k。根据此分析,可以画出如图1所示的灰度控制模块的结构图。

本灰度控制电路实现两种灰度显示模式:2bpp和4bpp,由BPIX的值定义。在硬件中,主要实现4bpp模式即16级灰度。对于2bpp模式,可通过16级灰度映射实现。整个操作过程如下:当异步复位信号(rst_lcd_n_a)为1时,内核通过总线对LCD控制器中的寄存器进行配置操作,直到配置最后一个使能信号(lcd_en)为止;当使能信号有效时,灰度控制电路开始正常工作;当总线数据缓冲器" title="数据缓冲器">数据缓冲器为非空(ldata_fifo_empty)且显示数据缓冲器为非满(rgb_fifo_full)时,灰度控制电路向总线数据缓冲器发出读请求信号(lcd_fifo_rreq),并在控制器工作时钟(clk_lcd)上升沿到来时读取一个32bit数据,将其锁存在32bit的锁存器" title="锁存器">锁存器中,并且在随后的数个工作时钟内将数据送出;锁存器每个工作时钟送出一个像素的数据(由BPIX的值来定义),当BPIX定义为2bpp时,则锁存器每次送出2bit数据,n即为2,送出32bit的数据需要16个工作时钟;当BPIX定义为4bpp时,锁存器每次送出4bit数据,n即为4,送出32bit的数据需要8个工作时钟;锁存器送出所有32bit的数据后,如果总线数据缓冲器仍为非空且显示数据缓冲器仍为非满时,锁存器继续向总线数据缓冲器读取数据(lcd_fifo_data[31:0]);锁存器送出的数据一方面送给列计数器再送给行、帧计数器进行计数,另一方面送给灰度级映射单元。灰度级映射单元根据BPIX值判断所送来的数据是何种灰度模式。如果是4bpp模式,则不需要进行数据映射,直接将数据送到灰度算法模块;如果是2bpp模式,则进行4级灰度数据向16灰度级映射,产生4bit数据并送给灰度算法模块。灰度算法模块根据列、行、帧计数值和像素数据算出相应的灰度数据。该灰度数据只有一位,需经一个移位寄存器转换成16位送给显示数据缓冲器,并同时向显示数据缓冲器发出写请求信号(rgb_fifo_wreq)。上述所有的操作都是在LCD控制器工作时钟clk_lcd下进行的。

3 显示区域方阵的划分

在设计列计数器、行计数器和帧计数器时,必须保证同步性,否则就会发生显示的错误。在这里,采用的方法是通过显示的数据量进行行计数器操作,再进行列计数器、帧计数器操作。其状态流程如图2所示。具体操作过程如下: 当LCD控制器在非使能状态时,所有的行、列、帧计数器都清0。LCD控制器使能后,当灰度控制模块从显示存储器读取图像数据时,列计数器x[9:0]和c[3:0]同时开始计数,其中c[3:0]进行模15计数。当计数器x[9:0]的值等于(xmax-1)时,x[9:0]和c[3:0]都清0并重新计数,同时行计数器y[8:0]和r[3:0]作加1操作,其中r[3:0]进行模15计数。当x[9:0]的值等于(xmax-1)时,计数器x[9:0] 和r[3:0]清0。当计数器y[8:0]的值为(ymax-1),且x[9:0]为(xmax-1)时,所有的行、列计数器清0,即完成一帧图像数据的计数操作,此时帧计数器f[3:0]加1。重复上述步骤即可进行下一帧的计数操作。由计数器x[9:0]、y[8:0]定义像素在显示区域方阵中的位置(x[9:0],y[8:0]);由计数器c[3:0]、r[3:0]定义像素在显示区域中的几何位置(c[3:0],r[3:0])。由此可以保证灰度控制模块在进行数据处理时,原始像素的几何位置与LCD显示器件上每个像素的几何位置一一对应,同时完成了显示区域方阵的划分。

4 灰度算法模块的说明

灰度算法模块主要是通过公式按预定的脉冲序列分布方式调整各帧0和1的密度,在panel上产生中间灰度级颜色。根据上述介绍,该灰度算法是通过三个公式实现的。为了减少运算量,降低芯片面积,公式(1)、(2)、(3)可以进一步转化为公式(4)、(5)、(6):

k=mod[(c+r+f)/15] (4)

p=mod[(c+k)/15] (5)

w=mod[(p+p-r)/15] (6)

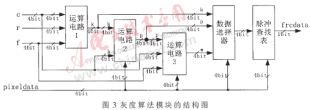

根据不同的图像数据信号选择相应的运算公式,然后再根据参数c、r、f计算出各像素点在任何时刻所处的脉冲序列号,最后由该脉冲序列号和原始图像数据从预定的脉冲序列查找表中找出相应的脉冲(1或0)。根据上述分析,可以画出图3所示的灰度算法模块的结构图。

该模块共由三个运算电路、一个数据选择器和一个脉冲查找表构成。运算电路1、运算电路2和运算电路3分别执行公式(4)、(5)、(6)的操作。灰度算法模块的整个操作过程是:首先判断图像数据pixeldata的值,如果该值是第一组即0000或1111,则三个运算电路都不工作,直接输出灰度数据frcdata为0或1;如果pixeldata是第二组的值,则执行运算电路1,运算电路2、3不工作,同时数据选择器选择k的值并送入脉冲查找表,脉冲查找表此时根据k和pixeldata的值查出灰度数据frcdata是0还是1;如果pixeldata是第三组的值,则执行运算电路1、2,运算电路3不工作,同时数据选择器选择p的值并送入脉冲查找表,脉冲查找表此时根据p和pixeldata的值查出灰度数据frcdata是0还是1;如果pixeldata是第四组的值,则三个运算电路都工作,同时数据选择器选择w的值并送入脉冲查找表,脉冲查找表此时根据w和pixeldata的值查出灰度数据frcdata是0还是1。这里的脉冲查找表是表1所示的15×15的查找表。这种公式算法结构将空间灰度调制法与帧灰度调制法结合在一起,并很好地利用了相邻像素的相互影响,从而大大提高了灰度调制能力。

5 FPGA验证

本设计采用Verilog HDL语言工具编写RTL级代码,并利用SYNOPSYS公司的EDA工具对该模块进行功能仿真和后仿真。最后,在FPGA(Altera公司的EP20K1000E672EFC)上实现。由于没有16级灰度图像数据,本次设计是将4级灰度数据映射到16级灰度的。其测试条件如下:

系统工作频率:50MHz;

屏幕: 240×320;

刷新频率:70Hz

FPGA验证结果如图4所示。

从图中可以看出,图像线条清晰,亮度层次分明,无闪烁、鬼影等干扰视觉的现象。这说明本文采用的基于面积-帧灰度调制的公式算法能够得到稳定的图像显示,且灰度控制模块功能正确。

在进行FPGA验证的同时,利用SYNOPSYS公司的综合工具对灰度控制模块的面积和功耗进行了评估,整个模块综合之后的门数为2042门,最大功耗工作模式下的功耗为0.941mW。同样是实现16级灰度,参考文献[3]中灰度控制电路综合之后的门数为7857门,最大功耗工作模式下的功耗为1.028mW,比本文中的灰度控制电路多用5815门,功耗增加了0.087mW;参考文献[4]中灰度控制电路综合之后的门数为1635门,最大功耗工作模式下的功耗为0.757mW,比本文中灰度控制电路的面积小、功耗低,但在进行16级灰度显示时会出现闪烁现象。因此,采用本文中的公式算法可以有效减小芯片面积和降低功耗,且解决了参考文献[4]中灰度级别低的问题。

参考文献

1 李维 ,郭 强. 液晶显示应用技术[M]. 北京:电子工业出版社, 2000

2 应根裕,胡文波,邱 勇.平板显示技术[M].北京:人民邮电出版社,2002

3 丁黄胜.嵌入式微处理器中LCD控制器的设计与实现[硕士学位论文].南京:东南大学,2003

4 张景嵩. 单色点阵液晶显示屏上的多级灰度显示方法及显示装置.专利:96103075.1996-03-22