高频移相全桥变换器的数字驱动研究

2008-07-29

作者:郑连清, 朱 军, 郭传奇,

摘 要: 基于经典全桥零电压零电流开关(ZVZCS)变换器" title="变换器">变换器拓扑,采用数字信号处理器(DSP)进行控制,提出了一种新型的移相PWM波形产生算法。结合IR公司最新推出的集成驱动芯片IR2304,通过对传统驱动电路" title="驱动电路">驱动电路增加两个无源元件,设计了带有负电压" title="负电压">负电压关断" title="关断">关断的硬件驱动电路,克服了IR系列不能产生关断负电压的缺点。实验验证了新型算法的正确性和驱动系统设计的可行性。

关键词:数字信号处理器; 驱动电路; 移相控制; 负偏压

全桥拓扑结构广泛应用于高电压、大功率变换器。为了提高变换器的功率密度和效率,可采用软开关技术。随着全桥软开关技术的发展和成熟,变换器的工作频率在不增加开关损耗的前提下大大提高。参考文献[1]提出了很多有实用价值的软开关变换器,但它们都集中在对变换器的拓扑改进和控制优化方面进行研究,很少论及变换器的驱动问题。随着大功率开关电源的发展和功率IGBT的大量应用,对驱动电路的性能要求越来越高。门极驱动电路影响IGBT 的通态压降、开关时间、开关损耗、承受短路电流能力及du/dt等参数,并决定变换器的静态与动态特性。因此,设计高性能的驱动电路是实现高频化变换器的关键技术。伴随开关电源的数字化和智能化成为未来发展方向,高频变换器的数字驱动也必将成为变换器研究的重要方面。

采用数字信号处理器(DSP)形成软开关变换器需要的移相PWM波形,参考文献[2]提出了基于EPROM 存储器产生移相PWM波形的实现方法,原理虽然简单,但其PWM响应速度较慢,而且对处理器资源利用率不高(占用较多的片上存储资源和CPU时间);参考文献[3]提出了基于DSP产生移相PWM波形的实现方法,其主要思想是先用DSP输出六路PWM波形,再外加硬件电路合成四个移相PWM波形,其硬件结构复杂。本文提出一种新型的基于DSP的移相PWM波形产生算法,通过检测通用定时器计数方式和比较单元的中断情况,直接修改比较单元的寄存器值,实现移相PWM波形输出,其硬件电路连接简单,不需要外加波形合成电路,只用DSP上的两个比较单元就可实现移相PWM波形,减少了CPU的占用时间,提高了工作效率。结合IR公司最新推出的集成驱动芯片IR2304[4],设计了带有负电压关断的硬件驱动电路,克服了IR系列不能产生关断负偏压的缺点,保证了变换器开关管的可靠关断,消除了密勒效应和其他信号对开关器件的干扰,提高了变换器的可靠性。实验结果验证了本文理论和设计的正确性。

1 驱动电路设计

本文采用TI公司的TMS320LF2407A 芯片[5]形成软开关变换器需要的移相PWM波形,其事件管理器模块EVA和EVB能够对三相反相器实现控制,产生对称和非对称的PWM波形。当外部引脚/PDOUBTX出现低电平时,能快速关闭PWM输出通道。可编程的PWM死区控制可以防止上下桥臂同时输出触发脉冲,非常适合产生数字变换器需要的PWM控制波形。通过软件算法的改进可以很方便地得到移相PWM波形。但是,DSP输出的是3.3V的电压信号,不能直接驱动功率IGBT,因此设计驱动电路非常必要。

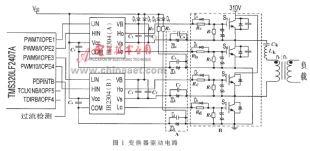

IR2304是美国IR公司生产的新一代驱动集成芯片,该芯片比同类其他驱动芯片具有更高集成度和更优越的驱动性能。但IR2304不能产生关断负偏压,为此需要对此驱动电路进行改进,使其产生负电压。基于以上功能和特点,设计了驱动电路,如图1所示。

DSP输出端口PWM7&PWM8和PWM9&PWM10为比较单元4和5提供两对独立互补的PWM波形输出。互补波形的死区时间可以通过控制寄存器DBTCONB来设置。输出的3.3V电平信号,分别与IR2304的高端输入HIN和低端输入LIN相连。DSP的功率保护引脚/PDPINTB与过流保护检测信号相连,一旦有故障发生,PWM输出为高阻态,立即封锁IR2304输出PWM波形,关断IGBT。虚线框A为关断负电压设计,虚线框B为IGBT驱动优化和保护设计。S1~S4为参考文献[6]提出的全桥ZVZCS变换器结构。IR2304(A)驱动超前臂S1、S4,其中Ho输出高端驱动信号" title="驱动信号">驱动信号,Lo输出低端驱动信号。C1为根据IR2304工作原理设计的自举电容。滞后臂的驱动结构与超前臂的相同,由IR2304(B)驱动。

1.1 负电压设计

IR2304是一种双通道高压高速电压型功率开关器件栅极驱动器,设置了自举浮动电源,不需要外加电源。但IR2304不能产生负偏压,可能由于密勒效应的作用,使开关管误导通。本文针对IR2304的不足,在每个驱动回路上增加两个无源器件,实现负压关断功能。如图1所示,在超前臂S4的驱动电路增加由电容Cb和5V稳压管ZDb组成的负压电路。其工作原理为:20V的 Vcc电源在上电期间,通过R5给Cb充电,Cb上面的电压保持为5V。在LIN端为高电平时,Lo端输出20V高电平,这时加在S4栅极上面的电压为20V-5V=15V,IGBT正常导通。当LIN端输入低电平时,Lo端输出为0V,此时栅极上面的电压为-5V,从而实现了关断时需要的负电压。对于其他功率开关管,负压产生原理相同。

1.2 自举电容及其栅极限流电阻选取

由于IR2304具有自举浮动电源设计,简化了驱动电路的设计,但是驱动芯片工作时的自举电容选取非常重要。本文中的自举电容采用一个大电容和一个小电容并联形成,并联的高频小电容用来吸收高频毛刺干扰。为了保证自举电容电压给上管提供合适的驱动电压,要注意:(1)尽量使自举电容充电回路不经过大阻抗负载,否则应为C提供快速充电回路。(2)当PWM开关频率较高时,由于充电时间变小,应选取小电容。当PWM工作频率较低时, S4的占空比较高,则S4开通时间较长,此时自举电压容易满足,应选取较大电容。

在设计时,取自举电容C:

式中,Qg为IGBT门极提供的栅电荷,Vcc为驱动芯片供电电压。

选取适当的栅极限流电阻RaRd,对IGBT驱动来说相当重要,因为IGBT的开通和关断是通过栅极电阻的充放电实现的,栅极电阻会对IGBT的动态特性产生极大的影响。数值较小的电阻使栅极电容充放电较快,从而减小开通时间和开通损耗,同时较小电阻增强了IGBT器件的耐固性,避免了du/dt带来的误导通。但小电阻只能承受较小的栅极噪声,并且极易导致栅极-发射极之间的电容与驱动电路引线的寄生电感产生振荡问题。另外,较小的栅极驱动电阻还使得IGBT开通时di/dt变大,会导致较高的du/dt,增加反向恢复二极管的浪涌电压。实际选用时应综合两方面影响因素,选取合适的栅极限流电阻。

2 软件设计

2.1 新型移相PWM变换器的控制算法设计

全桥移相PWM变换器,利用超前桥臂和滞后桥臂的相移来调节占空比。基于对经典全桥零电压零电流开关(ZVZCS)变换器拓扑的工作原理分析[6],对所产生的PWM信号的要求如下:(1)上下桥臂两管的驱动信号180°互补。(2)四路驱动信号的占空比均设置为50%,由于死区时间的影响,实际输出占空比应小于50%。(3)驱动信号中相位超前的信号作为超前桥臂信号,相位滞后的信号作为滞后桥臂驱动信号。驱动信号通过DSP事件管理模块EVB产生。EVB有三个全比较单元,每个全比较单元都有两个互补的PWM脉冲输出,因此可以使用其中两个比较单元提供四路驱动信号。

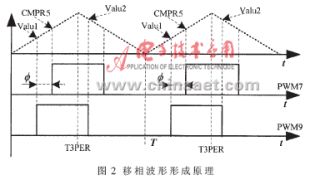

新型移相PWM算法的基本原理是:利用 DSP 事件管理器B中的两个全比较单元4和5输出四路脉冲。由全比较单元5输出超前臂上下管脉冲,全比较单元4输出滞后臂上下管脉冲。两个全比较单元的比较寄存器数值按反馈调节器输出的要求在两次比较中断时不断地修改。当比较单元5比较中断时,如果此时通用定时器3减计数,则赋给CMPR5使计数器计数增的新比较值Valu1;如果此时通用定时器3增计数,则赋给 CMPR5使计数器计数减的新比较值Valu2。通用定时器3的计数器计数周期为脉冲周期,并且按照连续增/减计数方式计数。比较寄存器影子寄存器的装载条件为下溢或周期匹配中断。实际编程时,需要按照实际的PWM周期设置对称波形的计数周期。在DSP中,移相波形产生原理如图2所示。

假设输出脉冲频率为50kHz,DSP 的CPU时钟频率为24MHz。可以计算出CPU 时钟周期为1/24MHz=42ns;由于按变换器开关频率50kHz计算,故计数周期为24MHz/50kHz=480,而通用定时器按照连续增/减方式工作,故DSP通用定时器的计数周期值设为其一半(240),即T3PER=0X00F0;

最小移相角为:Φmin=180/240=0.75°;

最小占空比:Dmin=05/240=0.0021。

可以看出,采用DSP移相控制方式,通过精确定量计算后产生的脉冲波形较模拟芯片精度更高,很适合高精度的数字变换器控制。

2.2 移相PWM算法的编程实现

获得精确移相PWM信号的具体算法过程为:首先设置通用定时器3的控制寄存器T3CON,确定计数器的计数模式和时钟源;然后根据需要的PWM波形周期设置周期寄存器T3PER;接着装载比较单元4和5的比较寄存器CMPR4和CMPR5,确定PWM波形的占空比;最后根据程序运行时的中断标志CMP5INT的检测对CMPR5进行新值装载(Valu1或Valu2)。通过上述相应的设置即可获得指定周期、指定脉宽的移相PWM驱动信号。软件流程如图3所示。

根据上述原理编写的移相PWM中断服务程序部分代码如下,并在硬件系统上进行了运行实现。

INTERRUPT_PWM:

….现场保护….

LDP #DP_EVB

BIT EVBIFRA, 13

BCND BACK, NTC

BIT GPTCONB, 2

BCND DECREASE, NTC

BIT GPTCONB, 2

BCND INCREASE, TC

DECREASE: LDP #DP_EVB

SPLK #Valu1, CMPR5

B BACK

INCREASE: LDP #DP_EVB

SPLK #Valu2, CMPR5

B BACK

BACK: ….现场恢复….

NOP

CLRC INTM

RET

3 实验结果及分析

基于以上理论分析和设计,搭建了一台样机,采用功率开关器件为IGBT,驱动芯片为IR2304,DSP为TI公司的TMS320LF2407A,自举电容取值为0.1μF,栅极电阻为15Ω,变换器开关频率为50kHz,占空比为0.5,移相角为30°(即寄存器T3PER=0X00F0,CMPR4=0X003C)。得到的实验结果波形如图4所示。

从图4可以看出移相波形的移相角为30°(移相时间为1.67μs,周期为20μs)。探头1为滞后臂驱动波形,探头2为超前臂驱动波形,即在DSP移相波形产生中在中断服务程序中写入的Valu1=0X0050,Valu2=0X00A0。通过控制写入的Valu1和Valu2,由下面两式可以精确得到所需的移相PWM波形。

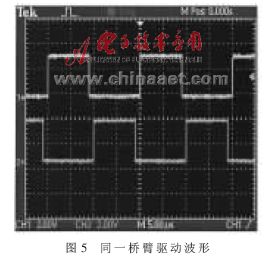

图5为同一桥臂互补驱动波形,由于DSP控制程序中事件管理模块初始化时死区控制寄存器DBTCONB=0X006E8,即互补波形的死区时间为6/240×8×10=1?滋s,足以防止同一桥臂两个IGBT的直通。输出的驱动波形高电平为3.3V,低电平为0V,可以看出不足以驱动功率IGBT,需要设计驱动电路增加驱动能力。

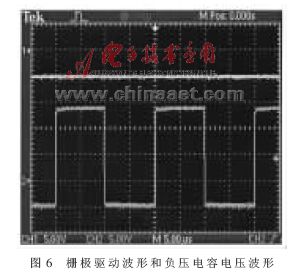

图6中探头1为在IR2304驱动电路中测得的负压电容电压波形,整个工作过程中稳定为-5V。探头2为IGBT栅极驱动波形,高电平约为15V,低电平为-5V。实现了设计要求的关断负偏压,提高了变换器可靠性。

本文研究了高频全桥变换器的驱动问题。基于经典ZVZCS变换器拓扑结构,采用TMS320LF2407A数字处理器芯片,提出了一种新型直接产生移相PWM波形的算法,通过软件很方便地实现了所需移相波形。较传统的算法,其主要优点有:(1)充分利用了DSP内部资源。使用全比较功能,直接在 DSP 内部生成四路移相并带有死区时间的PWM驱动波形。实现简单,可靠性高。(2)不需要增加外围驱动波形合成电路,移相波形的修改直接通过程序变换即可完成,方便灵活。(3)生成的移相波形移相精确,最小移相占空比可达0.0021。

通过增加两个无源元件改进驱动电路,克服了IR2304不能产生关断负电压的不足,使其输出具有-5V的偏压,使IGBT的关断更加可靠,改善了变换器的静态与动态特性。

对DSP移相软件算法原理和IR2304负偏压电路设计做了详细的分析和定量的计算,最后的实验结果证明了原理的正确性和设计的可行性。

参考文献

[1] 郑连清,娄洪立,胡宗军. 移相型全桥零电压零电流直流变换器拓扑结构综述.电气应用,2006,(9):1-4.

[2] 王聪,吴宏杰,魏伟华. 用于DC/DC全桥变换器的全数字式PWM控制器. 电力电子技术,2000,(6):40-42.

[3] 李志,林磊,邹云屏. 移相全桥DC/DC软开关变换器的全数字化实现. 船电技术,2004,(1):19-32.

[4] International Rectifier Corporation.IR2304 half-bridge driver.Date Sheet No.D60200-A, 2004.

[5] 刘和平.TMS320LF240x DSP结构、原理及应用. 北京:北京航空航天大学出版社,2002.

[6] CHO J G, SABATE J, HUA G,et al. Zero voltage and zero current switching full bridge PWM converter for high power applications.IEEE Trans. Power Electron.,1996,11(7):622-628.