长期以来,降低功耗一直是芯片设计中的重要需求。随着更大、更快的集成电路应用于便携式产品中,这个需求变得日益重要。因此,贯穿整个设计流程的功率管理技术也在不断改进,以确保产品的各个部分均得到适当、高效的功率供应,同时保证产品的可靠性。诸如多电压岛,以及时钟频率和阈值电压的动态调整等技术,均有助于在提供高性能的同时,节省便携产品中的电池能量。

更为重要的是,SOC在尺寸和速度方面的增长已经给大量的设计带来了功耗方面的挑战,而这些挑战并不属于传统的受供电限制的范畴。在这些设计中,热耗散和可靠性方面的问题,例如电迁移和电压降已经变得极为关键。深亚微米设计中的功率问题可能会限制设计的功能或性能,并严重影响到芯片的可制造性和良率。较高的功耗会造成结点区温度上升,导致晶体管动作速度变慢,并增加互连电阻。如果不考虑功率问题,会导致器件性能低于预期,进而使得器件良率下降。此外,较高的功耗会要求在温度管理方面采取更多的系统级措施。总而言之,这些功率问题正在造成

SoC和系统成本的增加。在SoC设计流程中进行功耗管理,能够有效控制这些成本。

SoC中的功耗

芯片的总功率等于动态功率加上静态功率。动态功率是指在开关逻辑状态转换过程中所消耗的功率,包括单元内部(内部功率)和驱动芯片节点及外部负载的功率(开关功率)。动态功率 = CV2F其中,C为负载,V为电压摆幅,F为逻辑状态转换的频率。随着半导体器件结构日趋小型化,器件和互连电容降低,芯片获得了更高的性能和更低的功耗。而更大规模的设计以及更高的开关速率将会导致功率增加。静态功率(泄漏功率)是指在晶体管不进行开关动作时消耗的功率。

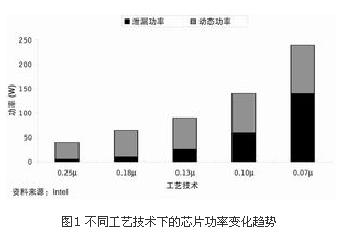

静态功率=VISTAT尽管在晶体管漏极和衬底之间的一些反向偏置二极管中存在着漏电流,但大部分泄漏功率来自晶体管关断时的亚阈值电流。由于亚阈值漏电流随着晶体管阈值电压(Vth)的降低而增大,从而带来了一定的麻烦。随着工艺技术向130nm及以下不断发展,泄漏功率可能会占到芯片总功率的50%(见图1)。泄漏功率的增加,会使得芯片中与可靠性相关的故障(即使是在待机状态下)呈指数增长。

随着CMOS工艺尺寸的减小,降低功率的主要方法转为降低供电电压VDD。由于功率和电压的平方成正比,所以降低电压对于控制芯片的动态功率极为有效。但是,由于开关延迟时间与负载电容和Vth/VDD成正比,因此,仅降低供电电压会导致电路速度降低。为了保证快速开关所需的足够的驱动能力,Vth必须与VDD成正比下降,这又会导致泄漏功率的增加。较好的方式是采用考虑了功率管理的设计流程,在时序要求和各类功耗目标之间取得平衡。

功率解决方案

设计抽象层次越高,对功耗的影响也就越大。例如,在系统级和算法级上,采用并行实现而非串行实现能够降低时钟频率,从而显著降低功耗。但并行方法的低功率可能要以面积增加或性能降低为代价。

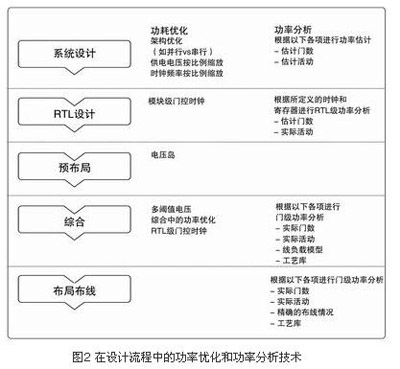

以一个用于串行接收数据样本的芯片为例,来说明并行架构与串行架构的不同效果。将数据样本并行处理,可将芯片逻辑电路的时钟从80MHz降低至10MHz,供电电压也可从1.8V降低至1.25V。并行处理逻辑电路要比相同的串行处理电路的面积大得多,但较低的电压和工作频率可将功耗降低75%。在其它一些设计中,占用面积上付出的代价较小,而功率节省效果却很明显,所以这是值得探索的一种折衷方案。图2中介绍了几种功率优化和分析的技术,这些技术在SoC的整个设计流程中均可得到应用。本文所涉及的功率解决方案如下:(1)模块门控时钟(2)多供电电压;(3)多阈值电压;(4)综合过程中的功率优化,包括RTL级门控时钟。

功率估计和分析

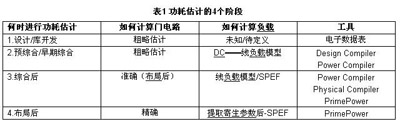

设计过程中,在如表1所示的4个阶段内进行功耗估计是非常有用的。每个阶段所估计的功耗准确度随增补设计和可利用的库信息的增加而提高。

&nb sp; RTL级功率分析

在设计流程早期,功率分析可对设计的功耗进行粗略估计。此时可能尚未选择库,所以库数据有限,这时,电子数据表(spreadsheet)分析可以用于找出最佳的注重功率的库和设计架构。在选定库之后,即可用Design Compiler和Power Compiler来代替电子数据表,或向电子数据表提供数据。

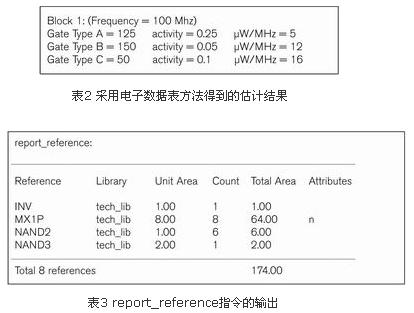

功率分析的电子数据表中包含了大致的门数和每个模块的活动值、mW/MHz数据以及相关的功率估计。这时进行的分析也有助于确认一项设计的功耗是否过大而不现实,从而可避免花费数周时间来实现一个根本无法制造的设计方案。

为了使用电子数据表分析方法,有必要对每一模块的门数(每一种类型的库单元数量)和活动水平进行估计。同时还需知道每种类型的单元在开关时所耗费的能量,库供应商手册中的数据可用于确定正确的功率速度比(mW/MHz)。一个模块内每种类型的单元的内部功耗可由

下式计算:功耗=门数×mW/MHz×活动×频率。将一个模块内所有不同类型的单元的功率加在一起,就可得出这一模块总的内部动态功率的估计值。在综合前,可根据所选择的体系结构和对设计本身的理解来对门数进行估计。例如,从总线宽度、字长、控制层和存储器深度等可得出大致的门数。在选择了库以后,模块的门数就可以利用Design Compiler的report-reference命令在初期综合后进行估计,这项功能将报告设计中每个例化设计的数量。功率计算的一个关键方面是指定活动水平。设计中的门电路都具有不同的活动水平,在对设计进行仿真提取开关动作或不进行仿真的情况下进行估计均可。但在选择了库之后,推荐进行功能仿真来确定开关动作。

开关动作以翻转率(TR)衡量。翻转率是指在单位时间内,一个设计对象(如节点、引脚或端口)从逻辑0至逻辑1以及从逻辑1至逻辑0进行转换的次数。对于一个节点来说,如果它在100ns的时间间隔内有50次从逻辑1至逻辑0的转换,以及50次从逻辑0至逻辑1的转换,则其翻转率为1,表示每ns有1次动作转换。功率与转换率之间的关系可以理解为,在状态改变的时间间隔内,为了完成内部电路的状态转换,就必须提供一定的能量,因此,每次转换都会消耗功率。

重要的是,只有在开关动作代表了芯片的实际工作状态的情况下,在任何抽象层次上的功率估计才有意义。常见的错误是在试图确定活动时,使用一个向量来仿真系统启动序列。此项活动极少能够代表真实的工作状况,因而会导致不准确的功率估计。采用RTL级仿真能够自动生成一个SAIF(Switching Activity Interchange Format)文件,但是活动值只有在此向量现实时才是准确的。目前的工具尚不能自动生成这样的向量,因为它需要对电路的实质有明确的理解。

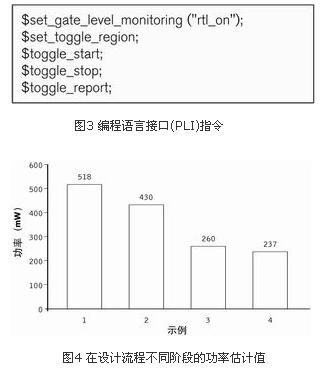

图3所示为可以在VCS内使用的编程语言接口(PLI)系统任务,用于在仿真期间生成SAIF文件。Power Compiler提供了一项power_estimate功能,这项功能使用SAIF文件来定义库和约束条件,以及对设计进行注释,以用于功率估计。Power Compiler针对未注释端口的默认开关动作是,每个上升沿有1/4的概率翻转,此数值在整个模块内应用和传送。

表2和表3所示为采用上述方式的估计结果。计算出内部功率之后,开关功率可以按内部功率的30%进行估计。由于没有精确的负载和开关数据,此数值仅为粗略的估计值。这样的估计主要用于对不同设计方案的功耗进行比较,而非用于预测芯片的实际功耗。但是,正如前文所述,RTL级的近似估计的确能够在早期对芯片设计的可实现性提供参考意见。

泄漏功率可以根据每种单元类型的泄漏数据进行估算。由于高态和低态下的泄漏不同,所以泄漏功率分析必须在信号处于一定逻辑状态的静态概率的基础上进行。静态概率表示为0至1之间的一个数,该数值可以根据信号的功能进行估计。例如,一般情况下,一个低态有效的复位信号的逻辑“1”静态概率(SP1)等于或接近1.0(100%)。对于一个数据总线信号而言,除非某些架构特性建议有其它概率,其SP1通常可以 假设为0.5(50%)。在选定了库之后,静态概率可在仿真期间,通过将信号处于某一特定逻辑状态下的时间和总仿真时间进行比较来计算得到。

门电路级功率分析

在综合完成后,有可能根据实际门数和仿真得到的活动来从Power Compiler中获得相当精确的功率估计值。这时估计的不准确性来自活动以及布局前的线负载值。通过从门级仿真中生成SAIF文件,准确性可以得到改善。在VCS中,与图3中相同的指令可用于生成SAIF文件,只是其中的第一条指令应当改为:

$set_gate_level_monitoring ("on");

这里必须再次强调,只有在仿真向量代表了真实的应用行为时,活动值才是准确的。Physical Compiler工具在物理优化后使用write_parasitics -distributed指令用于改善负载的准确性,这项指令能够产生注释了S

teiner路径和寄生电阻、电容估计值的SPEF文件。

布局完成后,门级仿真能够生成VCD(Value Change Dump)文件,用于PrimePower分析。VCD文件的记录在仿真过程中变为一个信号值,并提供了设计的节点活动、结构数据体系连接性、路径延迟、时序和事件方面的信息。

如果芯片的I/O数量众多、在高速下切换开关并驱动很长的线路,那它将有可能成为造成估计不准确的重要因素。如果设计目标要求得到准确而非最坏情况下的功率估计时,I/O的集总负载模型可能会产生过分悲观的估计结果。要想获得更为准确的结果,可以在关键的I/O单元类型中利用精确的分布阻抗模型进行HSPICE仿真。然后,I/O单元的功率即可采用确定每次上升/下降沿的电荷和能量的数值性方法来进行计算。在得到HSPICE的电流和时间输出后,每个瞬态的内部功率就可以利用梯形积分法(如在Matlab软件中)来进行计算。在PrimePower分析中记录的I/O活动可以用于对I/O功率按比例进行调整,同时总的I/O功率可与核心功率相结合,用于整体功率估计。为了表明在采用本文所述的不同设计阶段和实施循环中的估计方法所获得的功率估计值的差别,图4列举了在DSP设计中的一个高速FIR滤波器模块的实例。这一实例验证了,根据所提供的信息准确度的不同,功率估计值会有所差异。此图也表明了范例模块在设计流程中的4个不同阶段下功率估计值的变化情况:

(1)示例1-采用最坏情况下的开关动作和线负载估计值所得到的功率估计值;

(2)示例2-采用较为准确的线负载估计值和最坏情况下的开关动作所得到的功率估计值;

(3)示例3-采用准确的线负载估计值和实际活动所得到的功率估计值;

(4)示例4-采用精确的线负载(提取后)和基于SPICE准确仿真的实际活动所得到的功率估计值。■