处理器的发展

随着集成度不断提高,以及特征尺寸不断缩小,处理器内核电压也开始降至 1V 以下,同时其电流消耗也随着工作速度的提高而上升。工艺技术的改进必须与负载点电源设计技术的发展要求同步。适用于二十世纪八九十年代的电源管理解决方案未必适用于目前的高性能处理器。为处理器提供核心动力面临着若干技术上的挑战,如:如何放置大型旁路电容、浪涌电流、稳压精度与定序等。

能量的来源——大型旁路电容

处理器的总电流不单由电源自身提供,还由处理器的旁路以及电源的大型电容器提供。如果处理器工作强度发生突然变化导致负载急剧瞬变,那么浪涌电流首先由本地旁路电容提供——通常为较小的陶瓷电容,它们可针对负载变化做出迅速响应。随着处理速度从 500 MHz 增至 1GHz 乃至更高,我们还需要存储更多能量的旁路电容,这是至关重要的。另一能量来源就是电源的大型电容。对于较新型的高性能处理器而言,旁路电容应等于乃至大于电源的大型电容。为了避免造成稳定性方面的问题,我们必须注意确保电源在增加旁路电容的情况下保持稳定。即便电源评估板在基准情况下工作良好无误,但连接至负载时也可能出错。为确保对电源的反馈环路进行补偿,以适应更大的旁路电容。大型旁路电容必须彼此靠近,才能减小寄生效应。

避免浪涌电流

带有大型旁路电容的电源在启动时可能发生问题,因为电源启动时可能难以为大型旁路电容充足电并满足处理器的负载要求。因此,电源可能会在过电流情况下断电,电压也可能在启动时暂时下降(变为单调),这就可能导致处理器锁死。为了减小浪涌电流,我们可延长内核电压电源的启动时间,从而让旁路电容慢慢充电。众多 DC/DC 调节器均具有可调节的慢启动引脚,以延长电压上升时间。如果调节器不带慢启动引脚,那么我们可以采用外部 MOSFET 与 RC 充电方案来实现。超额电源设计是另一种解决浪涌电流的简单方法,前提是设计人员能够承受更高额定电流带来的体积增大、价格升高的不利因素。如果处理器要求的话,我们也建议采用带有电流限制的 DC/DC 调节器来保持单调的电压斜线上升。

精度调节

多年前的处理器要求电压容限达 5% 之多,但随着工艺节点不断缩小,内核电压也降至 1V 以下,因此容限减小,甚至可能要求线路(工作输入电压范围)、负载(工作输出电流范围)和工作温度上的误差容限不超过 3%。为确保精度调节能够满足处理器的要求,一般产品说明书的电气特性部分保证设备在一定温度和线路条件下的性能误差在参考电压 1% 的范围内。负载精度在3A情况下误差最大为 0.09%。TPS54310 在各种线路、负载以及温度条件下都能够轻松实现误差在 3% 以内。表1 给出了TPS54310 的调节精度示例。

AC 精度调整

如果处理器在从低工作到高工作状态变化中遇到动态负载范围突变,它会迅速消耗掉更多的电流,这就会导致电压下降。电源必须对电压变化立即做出反应以保持调节的准确度(图 1)。电压峰值 (voltage spike) 应不超过处理器的电压容限规范,因此您应准确了解处理器产品说明书中所列的最大绝对内核电压要求是多少。为了提高电源在瞬态情况下的调节性能,我们可降低电感器的值,从而加速稳压器的响应时间,并增加电容来提供更强的能量存储能力,以适应电压下降以及电压尖峰 (spike) 的情况。较好的做法是采用电源电压监控器来保护处理器,如果电压在系统掉电过程中下降过低,那么就能提供良好的断电重置功能。

定序

越来越多的处理器制造商开始针对核心与 I/O 上电定序提供建议的时序指南。一旦我们了解了时序要求,就可根据负载点电源设计者的要求来选择适当的技术。对于双电源而言,上电和断电有几种不同的方法,分别为:顺序、同时排序和预偏置启动。

如果内核与 I/O 上电之间要求有几毫秒的短暂间隔,那么可实施逐次排序 (sequential sequencing),具体顺序随意。其方法之一很简单,就是将一个稳压器的POWERGOOD 引脚连接至另一个稳压器的 ENABLE 引脚即可。另一种方法则是采用热插拔类型的定序集成电路来控制每个电压电平的打开和关闭。这能够实现灵活性,但也会占用板级空间,并增加成本。

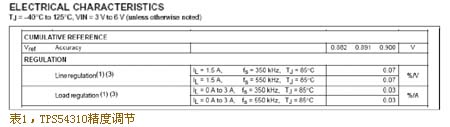

如果我们需要最小化上电与断电期间的内核与 I/O 电压差动的话,那么就可采用同时排序。在实施同时排序时,内核与 I/O 电压彼此跟踪,直至达到所理想的较低电压电平为止。这时,较低的电压在其稳压点上不再上升,而较高电压继续上升。德州仪器 (TI) 推出了带有 TRACKIN 引脚的 TPS54x80 开关稳压器和带有自动跟踪功能的 PTH 系列 DC/DC 模块,它们都可用于实施同时排序。图2显示了上电过程中的内核与 I/O 电压跟踪情况。

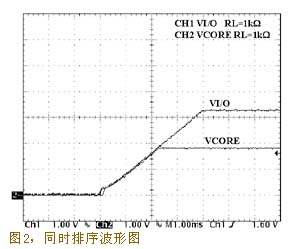

如果在内核处于“打开” 很久前就施加 I/O 电压,而且内核与 I/O 电压之间必须存在最小增量,那么我们可方便地实施预偏置方法。在这种情况下,处理器制造商建议在上电前用二极管对内核电压进行预偏置。二极管上的电压下降在内核与 I/O 电压之间保持最小增量。采用同步补偿 DC/DC 转换器时,应确保低压侧MOSFET 在启动过程中保持关闭,否则已经施加给内核的失调电压就会在 DC/DC 转换器启动时汇至接地,这可能会损坏二极管。内核电压随二极管电压下降而随 I/O 电压相应变动,这表明处理器的内核电压在打开前已经有了偏移值。随后,内核在失调电压的基础上斜线上升,直至达到所需的电压电平为止。图3给出了预偏置启动波形图的一个示例。TPS54x73 开关稳压器与 PTH 系列 DC/DC 模块可用于实施预偏置启动。

为 PLL 供电

许多较新型的处理器除了内核与 I/O 电压之外还要求单独的 PLL(锁相环)电源。如果执行代码时PLL的电压处于最小和最大容限之外,而且很不稳定,那么就可能会导致数据损坏,或处理器锁死。我们可采用简单的预防措施,如使用电源电压监控器 (SVS) 等,来保护数据的完整性。内核与 I/O 电压稳定后,PLL电压的容限必须在一定的时钟周期之内,如在执行任何代码前容限必须保持在最大1,000 个时钟周期内。某些处理器包括内置的SVS功能,可让PLL电压趋于稳定。如果您的处理器不具备上述的内部处理功能,那么可采用电压容限要求较严格的电源电压监控器来确认内核与 I/O 稳定性。请确保监控器的“RESET”时间大于 PLL 电压稳定下来所需的时钟周期数。电源纹波抑制 (PSRR) 较强的低压降调节器(如 TPS79xxx 系列)有助于降低不必要的噪声尖峰进入 PLL。

总结

目前,先进的高性能处理器需要高性能负载点电源。更大的旁路电容、排序、浪涌电流、精度调节以及 PLL 供电电压监控都是目前负载点电源所必须解决的问题。5年以前适用的电源解决方案可能已不再适用于较新型的处理器。请记住,DC/DC稳压器是针对特定市场和终端设备而专门设计的,有着特定的成本和性能目标。