辅助GPS接收机设计的系统级平台

2008-09-08

作者:寇艳红 张其善

摘 要: 提出GPS接收机集成设计与仿真平台的研制思想,进行GPS系统的建模、仿真和接收机设计验证的技术手段、开发模式" title="开发模式">开发模式及仿真设计流程,建立以数字中频" title="数字中频">数字中频信号为参考点的信号模型,并给出整体设计方案。

关键词: GPS 系统建模与仿真 可编程片上系统

随着卫星导航定位技术的空前发展和全球定位系统GPS(Global Positioning System)在军事、民用众多领域日益广泛的应用,越来越多的厂商投入到GPS用户端设备的研发和生产中。其中GPS接收机和专用芯片的研制融合了卫星导航、无线通信、嵌入式系统、微电子技术等多个专业领域的知识,新技术、新方法、新产品不断出现,在研究开发的早期要对新的处理技术和不同的设计进行分析、比较和验证,需要一种易用的、精确的GPS信号与接收机模型和系统级" title="系统级">系统级仿真工具[1][2]。在当前技术条件下这种模型和工具可以进一步发展为将经过验证的新设计吸收并集成到新的接收机、概念机以至原型机中的系统级平台。

1 辅助GPS接收机设计的系统级平台的提出

随着技术的发展,GPS接收机的结构已经由单通道序贯模式、时分多路复用模式发展到并行多通道模式,绝大多数接收机采用了数字信号处理" title="数字信号处理">数字信号处理模块。将数字信号处理电路与应用处理器做成单芯片,即内嵌" title="内嵌">内嵌MPU/MCU的GPS SOC(System on Chip)芯片的产品已陆续面市。新的数字信号处理算法、捕获与跟踪方法、参数估计方法、高动态和高精度定位算法、组合导航滤波算法等不断应用于GPS随机软件中。同时,GPS系统将增加新的扩频M码,并为民用用户增加在L2上的C/A码和新的L5频率。传统的GPS接收机和芯片由于不具有可升级性、不能同时兼容新的空中接口方案将会逐渐被淘汰。

在现有技术条件下,GPS接收机对各种动态环境下的多通道卫星信号的实时数字化处理仍需借助硬件实现。选用FPGA器件作为GPS数字信号处理的硬件平台,不仅可以提供纯软件信号处理尚不能达到的实时性以及ASIC相关器所不具备的灵活性和可扩展性,而且可以将GPS接收机的相关器、CPU及其接口、更多的功能单元集合在一块内嵌DSP或其他嵌入式处理器内核的FPGA器件上,即实现GPS信号和应用处理的可编程片上系统SOPC(System On a Programmable Chip)。要适应新的GPS波形和应用只需改动接收机中的软件和固件,使接收机用户不需要购买新的GPS硬件即可完成面向新系统并不断改变的应用要求、性能要求(如高动态性能的提高、新的载波跟踪技术的应用等)的升级。

要用FPGA实现SOPC,必须对FPGA设计进行全面的性能分析,不能仅限于时序的验证。在电子设计过程中系统级仿真占整个设计周期的比率已逐步提高到30%以上[3]。由于高层应用背景、系统目标定义、算法及设计规范的千差万别,系统级仿真工具的开发任务越来越多地转移到了原有EDA工具的用户——即电子产品和系统开发者身上。GPS系统级建模仿真工具与新的GPS接收机设计同样可以由设计者集成在一个开发平台之上并实现其相互验证和转化。这一平台不仅可以提供蕴含GPS知识工程与专家系统资源的GPS系统级仿真和设计验证工具,还可以直接形成概念GPS接收机的设计,形成GPS信号处理器的行为级模型和HDL设计,直接用于先进的GPS接收机系统与芯片的开发。

2 开发模式和设计仿真的流程

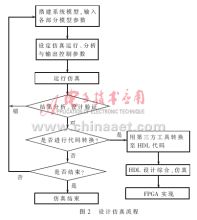

在辅助GPS接收机设计的系统级平台研制中采用一种新的开发模式和设计仿真方法,如图1、图2所示。首先在Mathworks公司的Simulink环境中通过信号互连的Blocks(部件)组成系统模型,由Matlab定制信号驱动仿真和分析结果,通过由FPGA厂商提供的第三方工具(例如Altera公司面向其内嵌嵌入式微处理器的器件Excalibur系列的SOPC Builder、面向其内嵌DSP block的器件如Stratix系列的DSP Builder、Xilinx公司面向其内嵌DSP的FPGA器件的System Generator等工具)可以产生硬件TestBench(测试基准),比较Simulink和后续的HDL仿真的结果;经验证的设计被移植到硬件时,无对应硬件实现的Blocks如TestBench驱动和分析模块将被自动舍弃。在Simulink中的仿真速度比HDL仿真大大加快,使实现复杂系统的仿真成为可能,仿真得到的结果与硬件实现的结果是精确匹配的。通过Simulink和HDL的协同仿真,在开发早期阶段即能看到预期的硬件结果,从而使设计过程大为简化。这种开发模式在成本、易用性、多速率和连续信号支持、控制逻辑和复杂系统构建和仿真等诸多方面均有优势。

3 GPS接收机模型及模拟产生GPS信号的逻辑点的选择

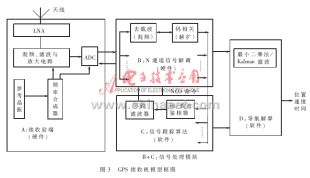

建模与仿真首先对GPS接收机天线接收到的卫星信号模拟,然后着重研究GPS接收机的系统级模型、仿真分析和设计验证,接收机部分主要针对图3给出GPS接收机模型框图中的A、B、C三个模块。

将模拟产生GPS信号的逻辑点选在接收机由A/D变换器产生的数字化中频处,即图3所示A部分输出与B部分输入处,开始数字化处理之前。理由有四:

(1)尽管Simulink可以对时间连续的动态系统进行仿真,但Matlab和Simulink本身是工作在计算机离散化的数字处理基础上的,对连续信号来说事实上是一种伪模拟环境。要在此环境中实现对高频模拟信号精确仿真,依赖于时间密集的高速采样,非常消耗计算资源,一般要得到一个可用的仿真结果需要等待长时间的运算;

(2)大多数现代的GPS接收机对下变频后的模拟中频信号进行A/D变换,以便采用先进的数字信号处理技术进行处理如数字跟踪、数字相关、数字滤波等;

(3)许多误差因素和接收机效应可以在这一点精确建模,通过推导得到其解析表达式;

(4)不含反馈信息的信号可以很好地与Matlab的代码顺序处理机制相适应,从而使代码流程清晰,使用简单,只需输入几个控制仿真操作的预定义参数即可。

4 数字中频信号模型的建立

图3所示A部分输出与B部分输入处的数字中频信号是模拟产生GPS信号的逻辑点,也是数字信号处理电路的输入。其数学模型的正确性将直接影响整个系统的性能,是建模的首要任务。

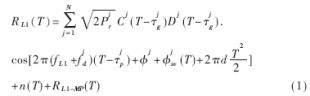

在GPS系统T时刻到达GPS接收机天线的L1载波C/A码RF信号可以表示为:

式中N为T时刻的可观测卫星总数,j为可观测卫星的编号,Pjr为接收信号功率,Cj()和Dj()分别为第j颗卫星的C/A码和导航电文数据,τjg为群延迟,τjg为相延迟,fL1为L1载波频率,fjd为载波多普勒频移,φj为L1载波相位差的固定项,φjv(T)为随机相位误差项,![]() 为频漂或老化效应造成的相位偏差。n(T)为背景噪声项,这里将L1 P码信号视为随机噪声并入n(T)中,RL1-MP为多径误差项。

为频漂或老化效应造成的相位偏差。n(T)为背景噪声项,这里将L1 P码信号视为随机噪声并入n(T)中,RL1-MP为多径误差项。

GPS射频前端电路输出的中频信号可以表示为:

式中fIF为中频信号的频率,Aj为其电平幅度;nIF(T)为中频噪声项,包含n(T)经各级滤波器之后落在最终的中频频带内的噪声、混频和滤波电路产生的谐波、本振反馈和镜象噪声等的影响。

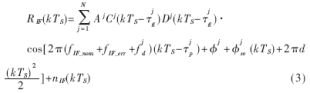

若考虑接收机参考频率源的误差,则(2)式中的fIF由数字中频信号的标称频率fIF_nom和其误差项fIF_err组成,即fIF=fIF_nom+fIF_err。理论上振荡器钟差影响采样频率,在采样时间上带来抖动。在仿真中若采用非统一的采样时间,将会显著降低仿真速度。通过均匀采样,并插入频率误差项到信号表示式中来模拟其影响。这样可将(2)式中的接收时间取为固定采样频率fS下的采样时间kTS,k=0,1,2,…。这样得到数字中频信号表示式为:

5 设计实现

整个GPS系统级平台的研制着眼于实际硬件系统的仿真,先进的信号处理和跟踪算法、设计方法的吸收与集成,不求复杂性而求其实用性和灵活性。开发内容分为以下三部分:

(1)GPS信号软件模拟器(数字中频信号产生模块)

对GPS卫星信号经过无线传播信道、GPS接收机天线、射频下变频、滤波和采样量化之后形成数字化中频(或零中频)信号的整个过程进行建模和仿真,得到数字化中频(或零中频)信号输出数据文件。这一部分采用Matlab代码编程实现。

这一仿真是在系统数学模型的基础上实现的。AGC电路模型可以分别采用Matlab代码和Simulink Block两种方式实现。前者仿真可以更快、更精确,但在接收机噪声不为常数时计算给定时间间隔的最佳门限并实现反馈控制较为困难;而后者可以实现重配置的AGC模型,更逼真地模拟AGC有限响应时间的波动,用于分析干扰环境的影响。

(2)GPS接收机数字信号处理模块

实现GPS接收机数字信号处理部分的模型,对典型GPS接收机中的去载波、码相关和跟踪环路(即图3所示解调和跟踪部分)进行建模和仿真。这部分在Simulink中设计实现。

为了对软件的模型精度进行验证,选择Zarlink公司的GPS芯片集GP2010/GP2015和GP2021进行建模,模仿信号在已知硬件上的效应和现象以便与真实测量数据相对比。同时所建模型也可针对其他接收机设计的模型重新配置,使设计具备足够的灵活性以适应不同硬件仿真的需求。GP2021芯片由时基产生电路、地址译码器、总线接口、状态寄存器和12通道并行相关器组成,每一通道的跟踪模块相互独立。每个相关器集成了码同步环和载波同步环的关键部件,要形成闭合的捕获跟踪环路还需要后边的CPU软件完成比较和控制[4]。

(3)验证和评估模块

提取实际接收机观测量和解调数据输出并与前两部分仿真输出结果作比较,为前两部分的设计提供功能和性能的验证与评估。这一模块在Matlab环境中设计实现。

参考文献

1 Alison Brown, Neil Gerein,Keith Taylor. Modeling and Simulation of GPS Using Software Signal Generation

and Digital signal Reconstruction. Proceedings of the ION National Technical Meeting, Anaheim, CA, January 2000

2 Phillip M. Corbell. Design and Validation of an Accurate GPS Signal and Receiver Truth Model for Comparing Advanced Receiver Processing Techniques. MS thesis, AFIT, OH, March 2000

3 周祖成,王志华. 中国集成电路大全——专用集成电路和集成系统自动化设计方法. 北京:国防工业出版社,1997

4 Zarlink Semiconductor. GPS 2021-GPS 12 Channel Correlator. WWW Site. www.mitel.com,2002.12