负载特性对驱动的要求

摘要: 本次主要想探讨阻性/感性/容性/电流型负载对驱动的要求,与大家分享。

Abstract:

Key words :

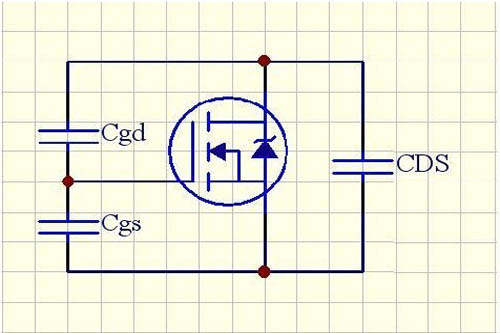

本次主要想探讨阻性/感性/容性/电流型负载对驱动的要求,与大家分享,请网友看看有何不足,先看一个图吧,FET的等效模型是:

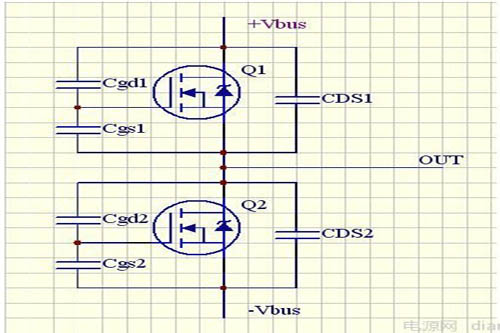

用它做成的半桥;就成了这样的一个电路:

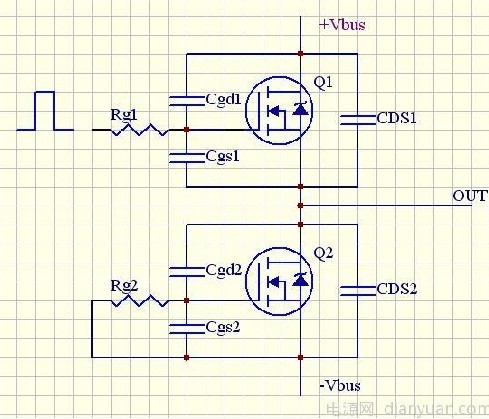

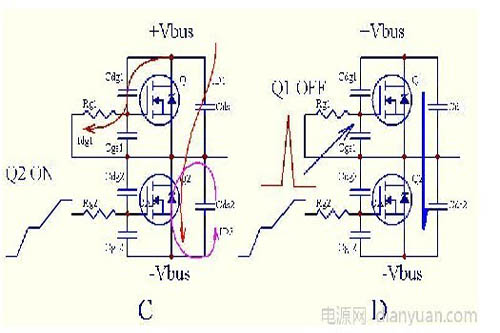

空载开关时;电路变成这两个工作模式:

上图是高边开关;低扁关断状态。下图是低边开关;高边关断状态。两个状态组成一完整开关周期。这个现象会导致半、全桥空载时发热。它不仅发生在开路状态;而且还会发生在容性负载和硬开关电路里。适当的控制“开”的速度;防制上下之通是必要的。

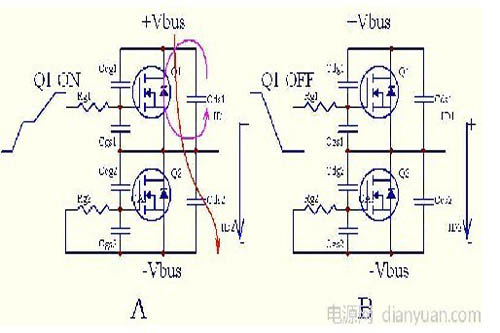

高端FET开关状态下;导通再关闭后,由于CDS1、CDS2的电容储能,Q1关断;输出仍为+Vbus。此时;Q1栅电压为0V,但是;Q1并没因此而承受电压。即Q1是零电压关断;关断过程;栅电压没有平台!没有弥勒效应区!经过一段死区时间后;低端FET导通,此时此刻;高端早已关断的FET的D-S终于承受了电压!虽然是空载;但在这过程中发生了一系列的电压电流变化,看图解!

高边FET导通后;向Cds2充电/Cds1放电,输出达到正电源电压。FET关断时;由于电容无放电回路(Q2断),电容电压保持不变,Q1零压管断(无弥勒效应)。Q1关后;仍由于电容做用而不承受电压。

用正驱动脉冲开启Q2,当栅电压达到门坎时;Q2开始通。Cds2短路放电;Cds1充电。显然;Q2是硬开通。Q1此时开始实质性承受电压。由于Cdg1的充电;导致在Q1驱动栅电阻上产生电压。当感应电压达到门坎时;Q1/Q2瞬间发生上下直通。

半个周期描述结束,在此思考下半个周期的工作过程。

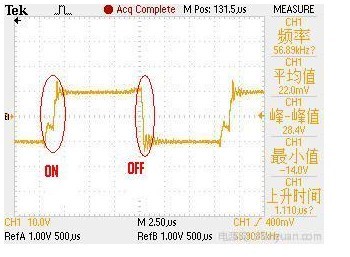

低端的管子是硬开通软关断;高端皆然。这里引用网友helen闸的实测波形,供大家讨论。注意:“ON”是;有明显的弥勒效应平台,“OFF”时;没有。

此内容为AET网站原创,未经授权禁止转载。