PPLID控制回路及其在FIRA控制中的应用

2008-09-11

作者:胡翌博1, 徐新民1, 邓士普2

摘 要: 吸取PID算法的基本思想,利用PLL的高精度和高灵敏度,从时域调参的角度提出了一种新的前端控制回路——PPLID控制回路,并介绍了其在FIRA机器人小车控制系统" title="控制系统">控制系统中的应用。

关键词: 锁相" title="锁相">锁相积分环 PID PLL PPLID 全功率" title="全功率">全功率提前补偿

1 对PID的新需求

PID算法具有结构简单、物理意义清晰、便于实现的优点,因而成为当前工程应用中最普遍和最经典的控制算法。但是参数整定" title="参数整定">参数整定一直以来都困扰着工程技术人员。

一方面,由于PID算法常用于前端控制回路,因而在一个较大的系统中往往有几十乃至几百个PID回路,这使得参数调整十分繁琐。若各个回路间存在耦合关系,则工作量更是难以预计。

另一方面, PID算法的应用场合十分广泛,而不同场合的控制参数却又不尽相同,因此针对某个被控对象设计的PID电路很难适应另一个被控对象的要求。这使得PID控制系统长期停留在通用算法的层次,难以提升为价格低廉的通用IC。随着EDA工具的发展,SOC的市场需求日益增长,算法集成化的趋势日益明显,在工业控制领域的表现之一就是对通用PID集成电路的需求越来越强烈。

上述两方面使得PID的广泛应用和参数整定过于繁琐的矛盾日益突出。要解决这个矛盾,实现PID算法集成化,必须找到一个简便灵活的参数整定方法。

同时,随着工业控制对精度和抗干扰的要求越来越高,高频微扰的问题日益突出。经典PID算法采用积分前置的方法来减小高频微扰的问题。但由于积分效应,必然削弱微分的预测补偿能力,从而影响系统的精度和灵敏度。采用新的方法克服高频微扰,也是一个亟待解决的问题。

2 PLL与PID结合对性能的改善

PLL在频率合成、通信以及标准信号发生器中被广泛应用,具有一整套成熟的理论,是相当经典的电路,其高灵敏度和高精度已被理论和实践证明。可将PID和PLL有机地结合起来,利用PLL的优异性能改进传统PID电路。

2.1 PLL与PID结合构成PPLID

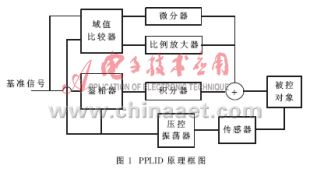

PLL本身可以看成一个锁相积分环。其中的鉴相器" title="鉴相器">鉴相器承担了差值计算和相位跟踪的任务(计算标准信号与反馈信号的相位差);积分器则不仅完成了积分功能,还肩负着保持当前状态的任务;而压控振荡器(VCO)则负责将被控对象信息反馈回鉴相器[2]。可见,这个环路已经具备了差值计算和积分的功能,只要再配以比例和微分调节,就构成了一个新颖的控制回路。由于其中含有锁相积分回路,因此称其为PPLID(Proportional, Phase-Locked-Integral and Differential Controller,即比例、锁相积分、微分控制器),其原理如图1所示。

其中的核心部件是锁相积分环,实际上就是一个PLL,代替PID中的积分器和减法器。若差值大于一定域值,则启动微分和比例调节;若差值小于域值,则只有锁相积分器处于工作状态,由它完成精细调节。基准信号就是控制量,这里它表现为频率波形。

PPLID吸收了经典PID的基本思想,因此可应用于经典PID回路所能涉及的所有领域,其优越性表现在以下四个方面:

①利用鉴相器作差值运算,大大提高了PPLID的灵敏度和精度。

鉴相器可以采取边沿对齐的方式来实现相位跟踪,即标准脉冲信号和反馈脉冲信号都输入鉴相器。只要边沿不对齐,则锁相积分环就会设法调整被控对象,直到二者的边沿完全对齐。因此,锁相环的静态精度和灵敏度非常高。

②PPLID中积分器的平均积分时间很短。

鉴相器计算出来的相位差最终是通过积分器转变为电压直接输出到被控对象上的。也就是说,积分器能够根据相位差决定在当前累积电压的基础上将电压调高或调低多少。由于鉴相器的高灵敏度使得相位稍有偏离便开始调整,因此积分器每次将电压调高或调低得很小,从而在很短的时间内就能完成调整工作。即锁相积分器的平均积分时间是很短的。

③PPLID利用微分和比例调节可以实现全功率提前补偿。

控制系统多处于微扰环境中,但有时会出现冲击干扰,差值会瞬间变得很大,仅依靠锁相积分环就不能足够快地收敛到目标值。这时可以启用微分和比例调节,对被控对象进行全功率提前补偿。这里的全功率指的是采用最高电压或最大电流对被控对象进行补偿,因此这种提前补偿的持续时间不会很长,只要偏差小于某个阈值,便立即停止,从而将精细调整的工作交给锁相积分环来完成。

④PPLID可用于高精度控制。

由于嵌入了PLL,因此PPLID继承了PLL回路的高精度特性,完全能胜任要求高精度控制的任务,成本也十分低廉。

2.2 PPLID对传统PID回路性能的改善

2.2.1 对高频微扰适应能力的改善

如前所述,PPLID具有灵敏度高和平均积分时间短的特点,稍有偏差便进行小幅调整,因此对高频微扰具有天然的自适应能力。

同时,由于微分器只在冲击干扰时才会启用,在高频微扰情况下是停止工作的,因此不存在高频微扰对微分器产生影响的问题。

2.2.2 对PID参数整定的简化

PPLID对PID参数整定的第一个简化是免去了微分和比例调节系数的调整。

在PPLID中,只有当差值大于阈值时才会启动微分和比例调节,进行全功率提前补偿。当差值小于某个值时,则立即停止微分和比例调节,从而将精细调节的任务交由PLL承担。可见,PLLID中的比例和微分调节并不负责精细调节,只负责将大幅度的偏差缩小到一定范围内,因此其系数对精度是无关紧要的。这样就免去了微分和比例系数的调整。

参数整定的第二个简化是对积分系数的要求大大宽松了。这种宽松性表现为:只要锁相积分器的延时小于被控对象的反应延时,环路就能够纠偏,而且能够及时精确地纠偏。说它能够纠偏是因为采取边沿对齐方式的PLL,其捕捉范围并不依赖于积分器的延时常数[3],这意味着在小幅振荡的情况下,锁相积分环的收敛性与积分常数的关联很小,只要保证环路对输出控制量(即积分器的输出)的调整速度快于被控对象的变化,就能够稳定在目标控制量。显然决定环路调整快慢的是最长延时单元,也就是积分器,只要其积分延时小于被控对象的反映延时,环路就能纠偏。说它能及时精确地纠偏是因为鉴相器的高精度和高灵敏度使得锁相积分环的平均积分时间很短,这意味着在偏差很小的情况下,环路能立即进行调整。

在控制系统中,被控对象多为机械运动或温度、压力和流量等物理变化。其反应延时一般总大于积分器的延时,因此要调整积分延时使其小于被控对象的反应延时是十分简便的。

由上可见,PLL与PID相结合,参数整定实际上就归结为延时参数的调整。这种调整无需在Z域进行分析,只要在时域直接进行即可(对于积分器,即调整电容和电阻值),这样就大大简化了参数整定。

参数整定的简化,不仅提高了PID回路的调试效率,而且为设计价格低廉的集成PPLID电路提供了可能。整个电路唯一需要根据工作环境进行调整的就是积分器的延时参数,只要将积分器留给用户调整,就能使得芯片应用于多种场合。

3 PPLID在FIRA中的应用

在FIRA足球机器人小车的前端控制器中应用了PPLID回路,取得了较好的效果。其实现如图2所示(这里只提供了小车左轮的电路,右轮与此对称)。由于传感器返回的信号是频率信号,可以直接输入到鉴相器的反馈端,因此无需使用压控振荡器。

3.1 AVR单片机

本系统采用ATMEL公司AVR系列单片机中的AT90S8515作为前端控制器,它除了产生标准信号、管理与上位机的无线通信、实现动态控制算法外,还担负PPLID中的阈值比较、启用和关闭微分调节等任务。

3.2 锁相积分回路

锁相积分回路就是一个PLL,其鉴相功能直接由CD4046的比较器Ⅱ实现,最高工作频率可达1.4MHz。PLL内部集成了两个相位比较器Ⅰ和Ⅱ,这里使用的是相位比较器II。它是一个由信号的上升沿控制的数字存储网络,对输入信号占空比的要求不高,允许输入非对称波形,具有很宽的捕捉频率范围,而且不会锁定在输入信号的谐波上。当进入锁定状态时,能保证两个输入信号之间的相移为0(关于CD4046的详细介绍见参考文献[3])。积分器电路采用如图3所示的超前滞后网络。其传递函数为:

G(s)=(1+τ2·s)/(1+τ1·s)

其中,τ1=(R1+R2)·C1,τ2=R2·C1

通过选择合适的R1,R2和C1的值,就可以在一定范围内设定时间常数。由于存在电机惯性,因而采用超前滞后滤波器且超前时间常数大于滞后时间常数,系统将获得很好的稳定性。

3.3 支援驱动器

支援驱动器采纳了微分调节的基本思想。微分调节实际上就是根据差值的变化来预计被控对象的变化,在本例中就是根据差值的大小,来预测当前电机转速的偏离是否能够快速收敛。如果单靠锁相环不能快速收敛,则支援驱动器启动,快速提高或降低电机控制电压,进行全功率提前补偿;当差值小于阈值时,便由锁相积分环来完成精细调节。

3.4 测 速

电机转速由光电码盘测出,输出的脉冲信号直接作为CD4046的一个输入信号,与标准信号相比较。同时该信号也要提供给AVR,以便比较差值是否超过阈值。

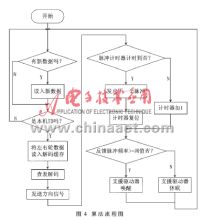

控制系统的算法可参照图4所示的流程图。

PPLID控制回路中采用的基本信号参量是频率或相位,根据调频或调相通信的原理,这种信号抗干扰能力强,适合远距离传输,而且便于实现数字无线通信。相信PPLID在分布式控制系统中将大有作为。

参考文献

1 D.F.Geiger.Phase Locked Loops for DC Motor——Speed Control(M).John Wiley & Sons, 1981

2 周雪琴,安 锦.计算机控制系统.西安:西北工业大学出版社,1998.2

3 戴逸民.频率合成与锁相技术.合肥:中国科学技术大学出版社,1995.2

4 沈 雷.CMOS集成电路原理及应用.北京:光明日报出版社,1986.8

5 耿德根,宋建国,马 潮,叶勇建.AVR高速嵌入式单片机原理与应用.北京:北京航空航天大学出版社,2001.2

6 陈隆昌,阎治安,刘新正.控制电机(第三版).西安:西安电子科技大学出版社,2000.5