基于VXI总线的时钟源模块的研究与设计

2008-09-22

作者:谢志刚 范梅生 魏震生

摘 要: 阐述了基于VXI总线的时钟源" title="时钟源">时钟源模块的组成及基本原理。在该时钟源模块中,用FPGA器件实现VXI总线寄存器基接口电路" title="接口电路">接口电路,用ECL器件完成功能电路,采用移位寄存器实现可编程延迟时间的调节。该时钟源模块具有经济实用等特点。

关键词: VXI总线 FPGA器件 时钟信号" title="时钟信号">时钟信号 ECL

在高速数字电路系统的设计中,时钟占有非常重要的地位,系统时钟性能的好坏,直接影响到整个电路系统的性能。在研制VXI总线数字输入/输出模块的过程中,需要用到六路激励时钟信号和六路响应时钟信号,激励时钟信号和响应时钟信号存在延时关系。对于不同的测试电路,激励时钟信号和响应时钟信号的延时时间长度可编程调节。该时钟源输出时钟频率范围为40MHz~1Hz;频率的准确度为0.01%;时钟频率稳定度为1×10-5;时钟带负载能力不小于8块数字输入/输出模块;输出信号电平为ECL电平,同时兼具TTL/CMOS电平的信号输出功能。基于VXI总线的时钟源模块,采用AlTERA公司的FLEX系列的FPGA实现寄存器基接口电路和部分功能电路;用MOTOROLA公司的MECL集成电路,实现时钟源模块的功能电路;用LabWindows/CVI软件设计虚拟仪器软面板,界面友好、操作方便。该时钟源模块可以作为自行研制的VXI总线数字输入/输出模块的时钟源,可以替代同类产品HPE1450A。在雷达故障诊断系统上长期运行的实践表明,该电路的工作是可靠的。

1 基于VXI总线的时钟源模块系统组成与概述

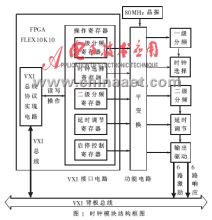

时钟模块为单槽、C尺寸、寄存器基器件,整体结构如图1所示。

由图1可以看出,时钟模块由接口电路和功能电路两部分组成。接口部分实现VXI初始化自检、地址译码、配置寄存器和操作寄存器的读写、数据传输应答等寄存器基器件接口功能。接口电路接收VXI总线的读写命令,完成数据传输,并通过对操作寄存器的读写,产生控制信号操作功能电路。用来控制功能电路的操作寄存器分为一级分频" title="分频">分频寄存器、二级分频寄存器、延时调节寄存器、启停寄存器和时钟选择寄存器。接口电路全部在ALTERA公司的FLEX10K系列的可编程集成电路内实现。操作寄存器输出的控制信号,通过电平变换电路,完成COMS/TTL电平到ECL电平的转换,供功能电路使用。功能电路由80MHz有源晶振、一级分频、二级分频、时钟选择、延时调节和输出驱动六部分电路组成,除了晶振外,全部采用MOTOROLA公司的MECL集成电路实现。80MHz有源晶振输出的时钟信号经过电平变换后,产生80MHz的ECL时钟信号,传送到一级分频电路" title="分频电路">分频电路。一级分频电路对80MHz的ECL时钟信号完成第一次分频,分频后的信号输出频率为80MHz/M,占空比为1/M,M表示一级分频数,其范围为2≤M≤65536。二级分频电路对信号完成第二次分频,80MHz的ECL时钟信号和经一级分频电路分频后产生的时钟信号,同时提供给时钟选择电路,时钟选择电路选择输出的信号作为二级分频的时钟信号。80MHz有源晶振输出的时钟信号用两种方式完成分频,既可通过一级分频后再进行二级分频,也可直接加到二级分频电路上产生分频信号输出。

两种方式能产生不同频率的输出信号。第一种方式的输出信号频率为80MHz/M×N,且2≤M≤65536,2≤N≤4096;第二种方式输出信号的频率为80MHz/N,且2≤N≤4096;M和N分别为一级分频数和二级分频数,两种方式输出信号的占空比均为1/N。延时调节电路对第二级分频后的信号完成移位操作,它能对输入信号产生12.5ns的延迟,并输出八路延时后的信号,将八路延时后的信号通过一个多路选择器,选择具有不同延迟时间的信号作为响应时钟信号,从而实现信号的延时调节。输出驱动电路把没有延时的信号作为激励信号输出,把延时调节后的信号作为响应信号输出。输出的同频率的六路激励信号和六路响应信号,经VXI背板本地总线,传送到数字输入输出模块中,作为时钟使用。由于MOTOROL的MECL集成电路,其输出端全部采用射级跟随电路输出,具有较低的输出阻抗和较高的驱动能力,可用作六路激励信号和六路响应信号的驱动。

2 接口电路工作原理

接口电路的功能可由一片可编程逻辑器件(PPGA)完成,采用ALTERA公司的FLEX10K系列的EPF10K10QC208-4芯片实现。FLEX10K系列的FPGA有着较低的功耗,在5V电压下工作时,其输出高电平最小为2.4V,输出低电平最大为0.45V;管脚处于高阻态时,漏电流为-40~40μA;商业级芯片的操作环境温度为0~85°C;其最大功耗Pmax可由公式Pmax=(Tj-Ta)/θja算出,Ta为芯片工作时的环境温度,Tj为芯片工作时的温度。取θja=8°C/W、Ta=40°C、Tj=85°C,可得Pmax=5.625W,满足VXI总线对接口芯片的要求。

接口电路结构图如图2所示。它具有如下特点:①具有VXI总线地址译码能力,能译码16位VXI总线地址,并能根据需要扩展到24位或32位;具有16位数据的传送能力并能根据功能进行相应的扩展。②内部寄存器分别为配置寄存器、STATUS/ID寄存器、仪器类型寄存器等,可根据不同模块功能电路,设计不同的功能寄存器。③能对VXI总线的数据传输仲裁和应答。④能监视功能电路的中断请求,可通过软件或外部跳线设置中断级别,向VXI总线发中断请求信号,完成中断菊花链的传递,并将逻辑地址放到数据线上。

其中,各操作寄存器的定义如表1~4所示。

3 功能电路工作原理

时钟模块的功能电路由80MHz有源晶振、一级分频、二级分频、时钟选择、延时调节、输出驱动六部分电路组成。这里仅重点介绍一级分频电路和时序调节电路工作原理,其它部分不再赘述。一级分频电路的原理图如图3所示,它由四个计数器MC10H016(U11、U12、U13、U14)和两个或门MC10H109(U15、U16)组成,能实现2~65536范围内的任意分频。FPGA内的寄存器实现分频预置数的设置,预置数经过MC10H124实现电平变换后,加到四片MC10H016的置数端,如图3中的PF0~PF15。当U11计满时,即QF0~QF3为1111时,计数满输出低电平有效信号,即TC1为低电平,TC1加载到U12的允许计数端 ,作为计数器U12的允许计数信号,使U12计数器计数加1;当U12计数满时,TC2输出低电平有效,使计数器U13开始计数;同理当U13计满时,U14开始计数时。只有当U11、U12、U13、U14同时计满时,U11、TC2、TC3、TC4才同时为低电平有效,TC1、TC2、TC3、TC4四路信号相或形成低电平有效的PEL信号,PEL信号即作分频后的时钟输出,也作四片计数器的并行加载信号。当并行加载信号PEL为低电平有效时,表示四片计数器同时计满,预置数PF0~PF15被加载到四片MC10H016上,作为计数的起始值,重新开始计数,完成了对时钟信号CLK的分频,分频后的时钟由PEL输出。

,作为计数器U12的允许计数信号,使U12计数器计数加1;当U12计数满时,TC2输出低电平有效,使计数器U13开始计数;同理当U13计满时,U14开始计数时。只有当U11、U12、U13、U14同时计满时,U11、TC2、TC3、TC4才同时为低电平有效,TC1、TC2、TC3、TC4四路信号相或形成低电平有效的PEL信号,PEL信号即作分频后的时钟输出,也作四片计数器的并行加载信号。当并行加载信号PEL为低电平有效时,表示四片计数器同时计满,预置数PF0~PF15被加载到四片MC10H016上,作为计数的起始值,重新开始计数,完成了对时钟信号CLK的分频,分频后的时钟由PEL输出。

延时调节电路如图4所示。它由两片移位寄存器MC10141(U28、U29)和1片八选一多路选择器MC10H164(U30)组成,完成对经过二级分频后的信号DIVCLK的延时处理。延时的调节范围为D×12.5ns,0≤D≤7,12.5ns由80MHz的时钟信号确定。图4中的S1、S2确定移位的方向。当S1为高电平、S2为低电平时(S2端悬空时,片子的内部逻辑使其保持为低电平),二级分频后的信号DIVCLK作用在U28的DL端,表示信号DIVCLK在80MHz的时钟信号作用下,依次进行移位操作,输出端STCLK1相对于STCLK0端有12.5ns的延时,STCLK2相对于STCLK1端有12.5ns的延时。依此类推,STCLK7相对于STCLK6端有12.5ns的延时。其时序如图5所示。延时后的信号经过MC10H164,可以选择输出具有不同延时长度的信号作为响应时钟信号。如选择X7端作为输出,则X7端相对于X0端具有7×12.5ns的延时。用该电路实现延迟,相比各种延迟线器件(如AD9500等)具有经济、实用、可靠的特点,可以广泛地应用于需要延迟设计的电路中。

4 时钟源电路板的设计

功能电路部分主要难点在于如何消除电路噪声。应按高速数字电路的设计理论,尽量减少电路板中的串扰、反射、电磁干扰、电路噪声等。否则,逻辑正确的电路也无法正常工作。除了合理的电路布局和电路滤波以外,正确地设置终端匹配电路是解决问题的关键。ECL器件的噪声容限较小,约为800mV,因此过大的噪声将使器件不能正常工作。由于ECL器件功耗大,合理的器件布局,将使器件的散热比较均匀,防止局部温度过高,也有利于电路板的正常工作。

参考文献

1 钱卫明,阴泽杰. 一种通用可编程的高速ECL时钟成形和分频模块. 核电子学与探测技术,2001(1)

2 陈虎成,安 琪,王砚方.基于VXI总线的时钟测量模块.核电子学与探测技术,2001(1)

3 陈光禹. VXI总线测试平台技术. 成都:电子科技大学出版社,1996

4 IEEE Standard for VMEbus Extensions for Instrumentation:VXIbus. IEEE,1996:1155~1992

5 崔少辉,孟 晨,杨锁昌. VXI总线自动测试系统测试接口设计.电子技术应用,2002;28(7)