基于Chirp函数的NiosⅡ嵌入式实现

摘要: 文章标题:基于Chirp函数的NiosⅡ嵌入式实现。中国IT实验室嵌入式开发频道提供最全面的嵌入式开发培训及行业的信息、技术以及相关资料的下载.

Abstract:

Key words :

摘 要:首先分析Chirp函数" title="Chirp函数">Chirp函数在频域上的一般特性,提出利用FPGA的嵌入式软核NiosⅡ处理器在嵌入式操作系统μC/OS-Ⅱ上实现Chirp的方法,即通过NiosⅡ处理器根据Chirp函数在频域上频率的跳变情况实时改变输出DDS(直接数字合成序列)模块的频率步进控制字的办法,控制DDS模块的频率输出,实现Chirp函数所要达到的扫频输出性的目的。通过在NiosⅡIDE编程环境中的Console窗口观察,该设计能很好地实现Chirp函数功能。

关键词:μC/OS-ⅡSoPC" title="SoPC">SoPC;DDs;FPGA;Chirp函数

0 引 言

SoC(System on(2hip)是20世纪90年代提出的概念,它是将多个功能模块集成在一块硅片上,提高芯片的集成度并减少外设芯片的数量和相互之间在PCB上的连接,同时系统性能和功能都有很大的提高。随着FPGA芯片工艺的不断发展,设计人员在FPGA中嵌入软核处理器成为可能,Altera和Xilinx公司相继推出了SoPC(System on a Programmable Chip)的解决方案,它是指在FPGA内部嵌入包括(;PtJ在内得各种IP组成一个完整系统,在单片FPGA中实现一个完整地系统功能。与SoC相比,SoPC具有更高的灵活性,FPGA的可编程特性使之可以根据需要任意定制SoC系统;与ASIC相比,SoPC具有设计周期短,设计成本低的优势,同时开发难度也大大降低。由于电磁波在传输过程中,经过色散介质如不均匀的波导,高空电离层时会发生色散现象,Chirp函数在射电天文信号的消色散处理中发挥着重要的作用,研究在FPGA中实现Chirp函数是基于FPGA的射电宇宙信号处理的重要组成部分。

l 系统总体设计

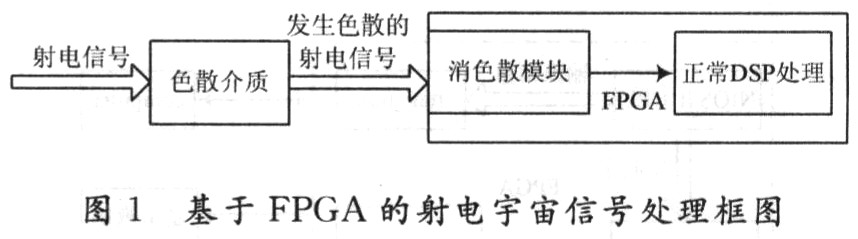

图1为基于FPGA的射电宇宙信号处理框图。

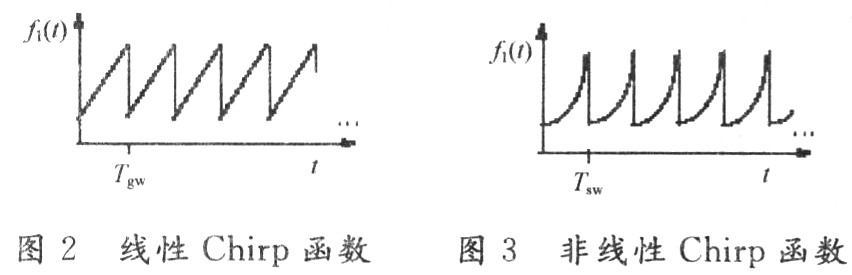

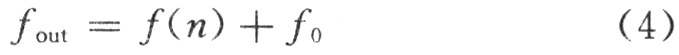

该设计是基于SoPC技术设计的Chirp函数信号发生器,该系统把微处理器模块和DDS模块集成到单片FPGA芯片内部,通过在嵌入式操作系统μC/OS-Ⅱ编写的程序,实时控制微处理器对DDS的控制字输出,DDS模块根据频率控制字的不同,输出不同的数字化正弦波。使之符合Chirp函数的时变频率特征。Chirp函数根据输出频率的递变规律一般分为两种:线性Chirp函数和非线性Chirp函数,以下是两种Chirp函数在频域上的表现图如图2,图3所示。

从图2,图3可以看出Chirp函数的频率输出与时间的f-t关系可以总结为:

(1)对于线性Chirp函数

在连续域时间域内有关系式:

式中:k为常数;f0为初始输出频率;t为连续时间。

在离散时间域有关系式:

式中:k为常数;f0为初始输出频率;n为采样点。

(2)对于非线性Chirp函数

在连续域时间域内有关系式:

式中:f为非线性函数;f0为初始输出频率;t为连续时间。

在离散时间域有关系式:

式中:f为非线性函数;f0为初始输出频率;n为采样点。

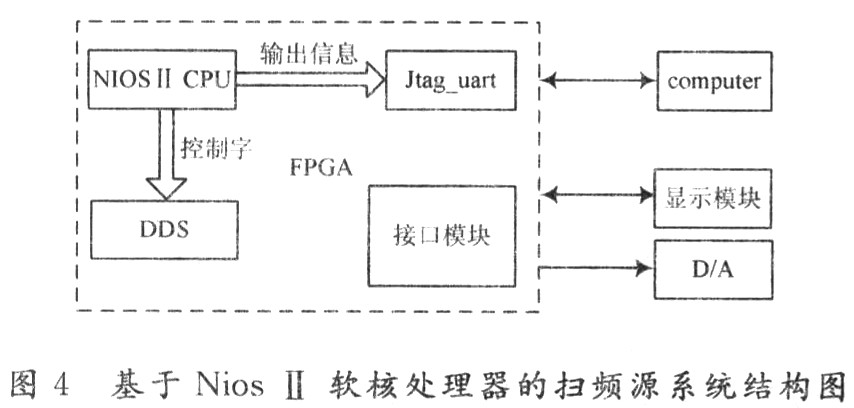

因此该Chirp信号源的功能是:在NiosⅡ中建立的微控制器;使用嵌入式操作系统μC/OS-Ⅱ建立对DDS频率控制字输出实时改变的任务;根据线性和非线性Chirp函数的特点控制字的输出根据需要线性或者非线性输出,并且在此设计中将该任务的优先级设置为最高。利用VHDL语言编写DDS模块,首先根据Matlab计算出需要的正弦数据,然后将这些数据存储于ROM中供DDS模块调用,并且通过微控制器中的Jtag_uart传输模块在编程监视窗口实时观测当前输入频率的大小,具体结构如图4所示。

2 DDS模块的设计

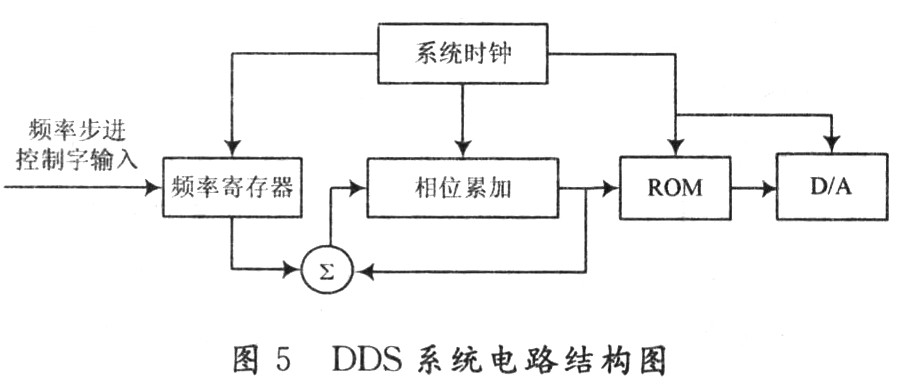

数字式频率合成器(DDS)模块的工作原理是:将O~2π的正弦函数值分为N份,将各点的幅度值存入ROM中,再用一个相位累加器每次累加相位值ωT,得到当前的相位值,通过查找ROM得到当前的幅度值。其系统框如图5所示。

DDS的几个主要参数是:系统时钟频率,频率控制字长,频率分辨率,ROM单元数,ROM字长。该设计的DDS是32位的,时钟频率为50 MHz,频率控制字长为32位,ROM单元数为2的11次方,ROM字长为16位。而且有如下关系:

频率分辨率=系统时钟频率/232;

频率控制字(FTW)=f×232/T;

其中:f为要合成的频率;T为系统时钟。

DDS的工作过程为:每次时钟的上升沿到来时,相位累加器(32位)中的值累加上频率寄存器(32位)中的值,再利用累加器的高11位作为地址进行ROM查表,输出相应的幅值数字信号。

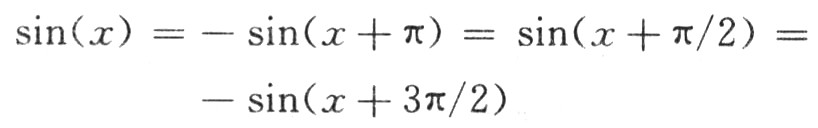

如果是扫频工作,只需要根据一定的规律实时修改频率控制字,就可以达到扫频输出的目的。但是该系统的性能受到以下两个方面的制约:ROM单元数和ROM数值的有限字长。由于ROM大小的限制,ROM的单元地址位数一般都远小于相位累加器的位数,这样只能取相位累加器的高位作为ROM的地址进行查询,这就相当于引入了一个相位误差。而且ROM的有限字长,不能精确表示幅度值,相当于引入了一个量化误差。因此应根据系统的性能要求选择合理的ROM。为了解决ROM的受限问题,该设计采用ROM压缩技术。因为正弦函数存在对称和反转特性,即:

对于O~2兀的幅度值,可以只存储O~π/2的部分。这样原本需要的2的11次方个单元的ROM现在只需要2的9次方个单元的ROM就可以实现。在MatIab中产生16位512点的O~π/2正弦波数据的命令如下:

将Y数据依次存入Altera公司提供的Megawiz-ard宏单元实现的ROM中即可。

3 嵌入式微处理器的实现

嵌入式微处理器的设计包括3个部分:利用SoPCBuilder定制的软核CPU,在QuartusⅡ环境下设计的电路和NiosⅡ编程。

本设计的软核CPU采用NiosⅡ/S标准型内核,带有16 KB的Cache;集成了外部的FLASH和SDRAM控制器用于保存程序数据;Jtag_Hart电脑开发板传输接口用于建立良好的用户交互接口使用户能在console界面上观察程序运行情况;两个位宽分别为8位和3位的输出口作为输出DDS模块的控制字;定时器用于产生CPU系统时钟;LCD控制接口用于在LCD显示一些需要的信息。

NiosⅡ的编程主要是基于嵌入式操作系统μC/OS-Ⅱ,μC/OS-Ⅱ是一个完整的、可移植、固化和剪裁的占先式实时多任务核(Kernel)。从1992年发布至今,μC/OS-Ⅱ已经有了上百个的商业应用案例,在40多种处理器上成功移植。其中Altera提供了对μCO/OS-Ⅱ的完整支持,非常容易使用。

μC/OS-Ⅱ提供以下系统服务:任务管理(TaskManagement);事件标志(Event Flag);消息传递(Message Passing);内存管理(Memory Management);信号量(Semaphores);时间管理(Time Management)。在应用程序中,用户可以方便地使用这些系统调用实现目标功能。

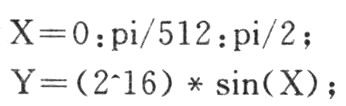

在该设计中建立一个主函数和两个任务函数,主函数的功能:调用系统任务初始化函数OSTaskCreateExt()初始化两个任务函数:调用系统开始函数OSStart()启动系统开始工作。

任务1:实时的改变DDS控制字的输出,并且保持一段时间,在遍历完所有的需要频率以后,延迟调用系统延迟函数OSTimeDlyHMSM(),延迟63 s将该使用权交付给任务2。

任务2:为了保证该系统以后能有功能扩展,建立一个任务,其仅仅是通过函Jtag_uart接口使用函数printf(),向电脑发送一个任务2已经开始工作的提示信息,如果以后需要扩展功能则只需修改任务2即可。程序的具体流程图如图6所示。

在任务1中实时改变变量i的值步进为1,通过定义的Chirp函数关于时间和输出频率控制字之间的关系函数function(),计算得到此时的频率控制字f,并且将f的值通过API函数IOWR_ALTERA_AVALON_PIO_DATA()从I/O端口输出以控制DDS,然后延迟2 s使DDS保持该输出频率一段时间,并且通过Jtag_uart端口在Console调试界面向用户提示当前的信号源的输出频率,程序如下:

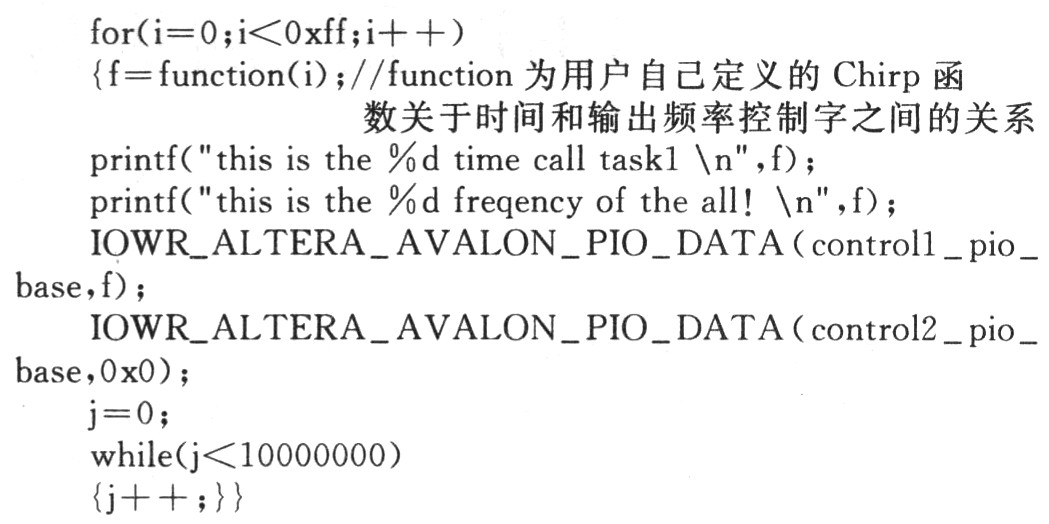

图7为QuartusⅡ中生成的嵌入式软核示意图。

4 结 语

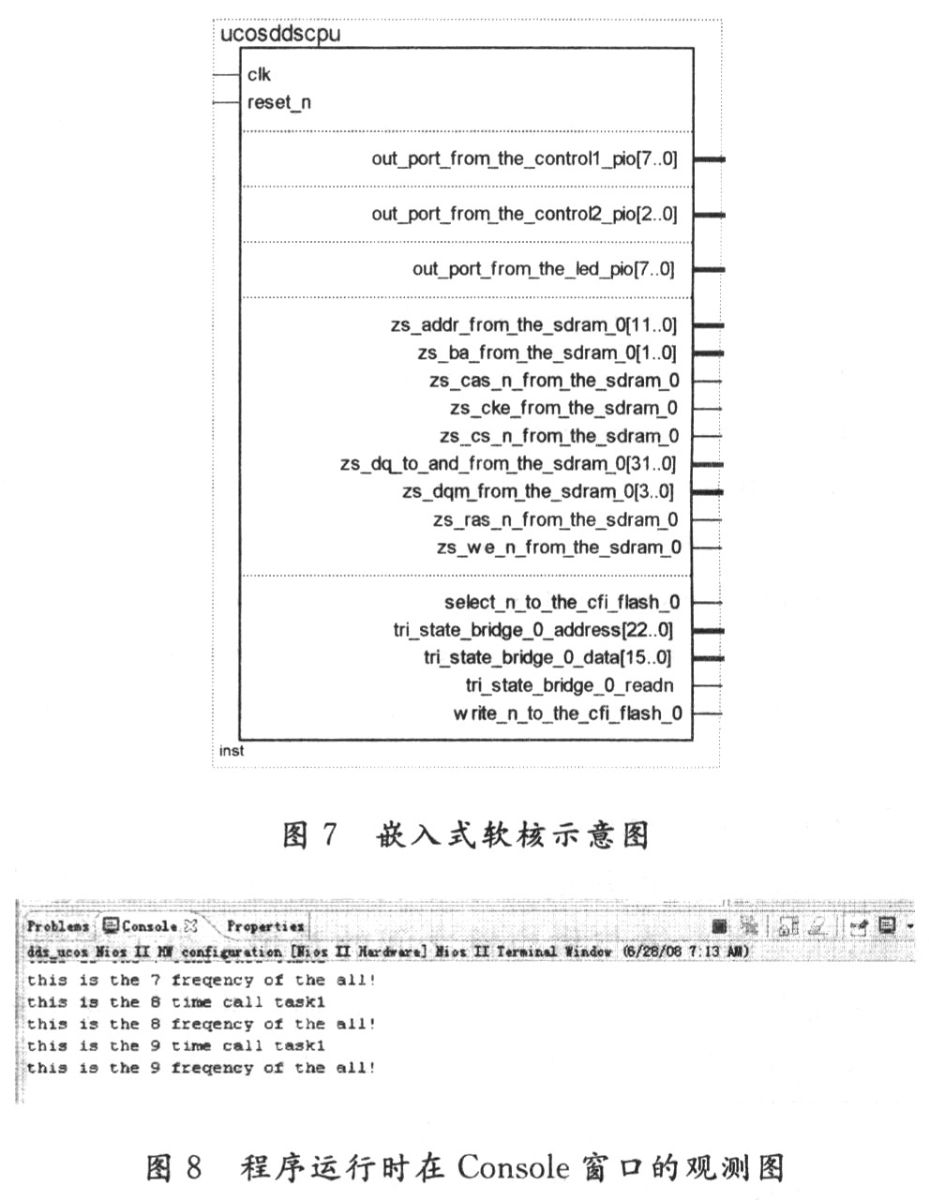

该设计在21controll公司提供的V4.O FPGA/SoPC开发学习套件上面通过仿真验证,该套件的核心芯片为CycloneⅡ系列:EP2C20F484C8,其具有18 752个逻辑单元(LE)和52个M4K RAM块,能够很好地设计存储需要的数据,完全符合设计要求。通过调试程序在NiosⅡIDE编程环境中的Console窗口观察如图8所示。证明该程序能够很好的完成Chirp函数的功能。

此内容为AET网站原创,未经授权禁止转载。