集成一直是无线通信进步的关键,它使设备实现了多功能、小型化。尽管手机处于这些趋势的前沿,但降低成本、加快上市速度也是促使蜂窝基础设施实现更高集成度" title="高集成度">高集成度的驱动力。随着无线集成设计人员力求在更小封装内集成更多功能,在单一器件内实现模拟、数字和高频功能等更高水平的集成依旧是IC的主流趋势。手机和基础设施设计人员试图在单个系统内集成多个无线标准的诉求使问题变得更加复杂。为平衡这些不同的需求,创新性设计技术借力放大器、收发器和其它器件的先进技术资源和专业知识,以期创造出不牺牲性能且集成度更高的系统。

Analog Devices(ADI)射频事业部高级营销经理Dale Wilson指出,“尺寸作为设计的一个重要的考量标准,在手持和便携式应用中是尤为突出;而在较大的系统中,对尺寸大小也有要求,客户希望在一定体积内,实现更多更强的功能。在多数情况下,客户希望单个设备在拥有多功能的同时,成本能有所下降。此外,他们还希望能够减少组装和测试成本、简化实际设计工作。如果调谐、滤波、偏置等功能都能在芯片上实现,则可以大量减少用户端的工作量,同样也可以加快客户产品的面市时间。分立射频元件的性能通常比高集成度器件要好。但在许多应用中,只要目标价格得以实现,那么性能‘足够好’就可以接受。因模拟和高性能射频器件更多地采用CMOS工艺,也就有更多机会集成数字控制功能。”

为应对这种高集成度的要求,ADI公司传统上采用先进的双极型工艺实现其众多高性能射频产品。然后,客户会在其系统内采用数字控制功能。Wilson指出,ADI现正采用最新的BiCMOS工艺,它具有优越的模拟性能以及在芯片中集成数字控制功能的能力。CMOS工艺也被用来实现高度集成的射频器件,并且采用数字化处理来克服射频性能局限。

去年秋天,ADI首次推出了支持高密度射频卡的射频混频器和调制器,而且它能提升长期演进(LTE)和第四代(4G" title="4G">4G)基站(图1)的容量和速度。ADRF670x系列混频器和ADRF660x系列调制器可在单一器件内整合多个独立功能模块。在4款ADRF660x系列的产品封装内集成了一个有源射频混频器、单端50欧输入的射频输入平衡-非平衡转换器(balun)、以及一个集成有压控振荡器(VCO)的锁相环(PLL)频率合成器。该有源混频器提供6dB的电压转换增益。差分IF输出工作于500MHz。ADRF6601接收混频器工作在300到2500MHz,内部LO范围是750到1160MHz。在12dBm输入功率时,它达到1dB的压缩并可实现30dBm的输入三阶截点。该混频器的单边带(SSB)噪声是12dB。

图1:射频调制器和下变频器包含一个集成PLL,它是一个多模N倍频合成器,支持LTE 100KHz通道光栅。

每款ADRF670x调制器的都在射频IC内集成了模拟同相/正交(I/Q)调制器、RF输出开关、带压控振荡器的锁相环。该调制器输入带宽为500MHz。ADRF6701 I/Q调制器的PLL/合成器使用一个N分频(fractional-N)PLL,它将LO信号倍频后馈送至I/Q调制器。PLL的参考输入接受从12MHz到160MHz的信号。调制器的输出频率是400至1300MHz。其内部L0频率范围是750到1160MHz。该器件在1dB压缩点和29dBm输出三阶截点条件下,可提供14dBm的输出功率,并提供158dBm/Hz的噪声本底。

对PA的集成要求

随着3G无线网络的完善并逐渐向4G系统过渡,分布式架构和有源天线系统的应用推动着对更小、更高效收发器和PA的需求。例如,美信集成产品(Maxim)公司的MAX9947就承诺可简化满足天线接口标准组织(AISG)的基站和塔安装设备(图2)的实施。这款尺寸为3x3mm,采用 TQFN形式封装的单芯片收发器包含了发射器、接收器和有源滤波器。

图2:收发器集成了带Autodirection功能的输出,可用来处理塔安装设备的总线仲裁而无需MCU。

其中,发射器包括一个OOK调制器、一个符合AISG频谱辐射规范的带通滤波器和一个输出放大器。接收器包括一个中心频率在2.176MHz、带宽为200kHz的带通滤波器。它还包括一个用于重构数字信号的比较器和OOK解调器。在50Ω输入阻抗条件下,MAX9947具有-15到 +5dBm的输入动态范围。其可由电阻调控的输出功率(7至12dBm)补偿了外部电路和线路的损耗。该收发器支持所有的AISG数据速率:9.6、38.4和115.2kb/s。

集成一直是无线通信进步的关键,它使设备实现了多功能、小型化。尽管手机处于这些趋势的前沿,但降低成本、加快上市速度也是促使蜂窝基础设施实现更高集成度的驱动力。随着无线集成设计人员力求在更小封装内集成更多功能,在单一器件内实现模拟、数字和高频功能等更高水平的集成依旧是IC的主流趋势。手机和基础设施设计人员试图在单个系统内集成多个无线标准的诉求使问题变得更加复杂。为平衡这些不同的需求,创新性设计技术借力放大器、收发器和其它器件的先进技术资源和专业知识,以期创造出不牺牲性能且集成度更高的系统。

Analog Devices(ADI)射频事业部高级营销经理Dale Wilson指出,“尺寸作为设计的一个重要的考量标准,在手持和便携式应用中是尤为突出;而在较大的系统中,对尺寸大小也有要求,客户希望在一定体积内,实现更多更强的功能。在多数情况下,客户希望单个设备在拥有多功能的同时,成本能有所下降。此外,他们还希望能够减少组装和测试成本、简化实际设计工作。如果调谐、滤波、偏置等功能都能在芯片上实现,则可以大量减少用户端的工作量,同样也可以加快客户产品的面市时间。分立射频元件的性能通常比高集成度器件要好。但在许多应用中,只要目标价格得以实现,那么性能‘足够好’就可以接受。因模拟和高性能射频器件更多地采用CMOS工艺,也就有更多机会集成数字控制功能。”

为应对这种高集成度的要求,ADI公司传统上采用先进的双极型工艺实现其众多高性能射频产品。然后,客户会在其系统内采用数字控制功能。Wilson指出,ADI现正采用最新的BiCMOS工艺,它具有优越的模拟性能以及在芯片中集成数字控制功能的能力。CMOS工艺也被用来实现高度集成的射频器件,并且采用数字化处理来克服射频性能局限。

去年秋天,ADI首次推出了支持高密度射频卡的射频混频器和调制器,而且它能提升长期演进(LTE)和第四代(4G)基站(图1)的容量和速度。ADRF670x系列混频器和ADRF660x系列调制器可在单一器件内整合多个独立功能模块。在4款ADRF660x系列的产品封装内集成了一个有源射频混频器、单端50欧输入的射频输入平衡-非平衡转换器(balun)、以及一个集成有压控振荡器(VCO)的锁相环(PLL)频率合成器。该有源混频器提供6dB的电压转换增益。差分IF输出工作于500MHz。ADRF6601接收混频器工作在300到2500MHz,内部LO范围是750到1160MHz。在12dBm输入功率时,它达到1dB的压缩并可实现30dBm的输入三阶截点。该混频器的单边带(SSB)噪声是12dB。

图1:射频调制器和下变频器包含一个集成PLL,它是一个多模N倍频合成器,支持LTE 100KHz通道光栅。

每款ADRF670x调制器的都在射频IC内集成了模拟同相/正交(I/Q)调制器、RF输出开关、带压控振荡器的锁相环。该调制器输入带宽为500MHz。ADRF6701 I/Q调制器的PLL/合成器使用一个N分频(fractional-N)PLL,它将LO信号倍频后馈送至I/Q调制器。PLL的参考输入接受从12MHz到160MHz的信号。调制器的输出频率是400至1300MHz。其内部L0频率范围是750到1160MHz。该器件在1dB压缩点和29dBm输出三阶截点条件下,可提供14dBm的输出功率,并提供158dBm/Hz的噪声本底。

对PA的集成要求

随着3G无线网络的完善并逐渐向4G系统过渡,分布式架构和有源天线系统的应用推动着对更小、更高效收发器和PA的需求。例如,美信集成产品(Maxim)公司的MAX9947就承诺可简化满足天线接口标准组织(AISG)的基站和塔安装设备(图2)的实施。这款尺寸为3x3mm,采用 TQFN形式封装的单芯片收发器包含了发射器、接收器和有源滤波器。

图2:收发器集成了带Autodirection功能的输出,可用来处理塔安装设备的总线仲裁而无需MCU。

其中,发射器包括一个OOK调制器、一个符合AISG频谱辐射规范的带通滤波器和一个输出放大器。接收器包括一个中心频率在2.176MHz、带宽为200kHz的带通滤波器。它还包括一个用于重构数字信号的比较器和OOK解调器。在50Ω输入阻抗条件下,MAX9947具有-15到 +5dBm的输入动态范围。其可由电阻调控的输出功率(7至12dBm)补偿了外部电路和线路的损耗。该收发器支持所有的AISG数据速率:9.6、38.4和115.2kb/s。

在PA方面,设计师面临很高的峰-均值比以及严苛的频谱生长规范的约束。Scintera Networks公司希望能以其SC1887自适应射频功率放大器线性器(RFPAL)系统级芯片(SoC)来满足这种要求,SC1887在射频域可执行复杂的信号处理。SC1887由标准CMOS工艺制造,采用了该公司的千兆赫兹信号处理技术(GSP)。这种可编程模拟信号处理器(ASP)平台,力图降低模拟方案的功耗及实现更小尺寸,而这原本是数字信号处理(DSP)的优势。SC1887射频输入和射频输出方案支持独立于基带和收发器子系统的模块化PA设计。SC1887的功耗小于600mW,非常适合低功率发射器。这款SoC覆盖 698到1000或1800到2800MHz频段。它支持的输入信号带宽可达60MHz、峰均值比为10dB。该芯片可实现将相邻信道泄漏功率比(ACLR)改善至26dB。

对更高效率的追求,也是Nujira和RF Micro Devices(RFMD)这两家公司开发PA的动力。这两家公司称,无线基础设施供应商能够利用它们的PA开发出可满足世界各种传输标准的单一的多模、宽带射频前端。其PA设计主要针对4G基站,它集成了RFMD的RFG1M09180 180W氮化镓(GaN)宽带功率晶体管与Nujira的Coolteq.h包络跟踪功率调制器。仅使用一个RFG1M器件和一个Coolteq.h模块,这款RFMD Nujira的RF前端就可工作(发射)在728到960MHz频段。它具有45dBm的平均输出功率,效率在50%以上。采用RFMD 目前开发的GaN器件,这两家公司期望只使用三个宽带PA就能覆盖700至2600MHz的蜂窝频率。

通过采用碳纳米管作为PA晶体管的散热材料,Fujitsu Laboratories(富士通实验室)公司已成功研制出工作在高频、100W级、倒装芯片封装的放大器,它也是针对4G系统移动基站设计的。为获得高频、大功率输出和放大性能,该公司开发出“双面散热”技术,晶体管芯片的两面都可散热。该公司介绍,这项技术还可以使晶体管芯片的尺寸缩小至现有晶体管芯片大小的2/3以内。

使用倒装芯片结构,碳纳米管焊球(bump)经过放大器顶部电极和基板之间。此外,在放大器的背面加装一个散热器,这样,从放大器的两面都可将热量带走。为在高频获得高放大倍率,互连至少需10μm长。富士通利用铝-铁(Al-Fe)膜将碳纳米管延长至20μm,它与板垂直。与传统方法比,这项新技术有望将散热效率提高1.5倍。

这项工作凸显了许多移动通信设计工程师对有效热管理的关注。东芝(美国)电子元件公司主管微波、射频和小信号器件的开发经理Homayoun Ghani表示,更高效的设计仅需一个更小的散热器,这使得在移动系统应用中可采用更小更轻的器件。他指出,“接下来面临的挑战主要来自这些小器件产生的热量,以及如何正确地设计一个有能力处理这些热量的系统。”Ghani指出,一些系统集成商采用液冷技术。

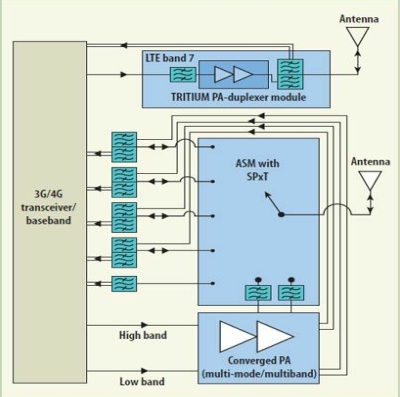

在蜂窝手机集成化设计过程中,会遇到他们自身的障碍。TriQuint公司负责移动器件的市场营销高级主管Shane Smith表示,“对于模拟集成,半导体公司正在开发支持多模、多频段工作的PA。目前,带EDGE和GMSK调制的五频段WCDMA需要客户购买6个PA。 2010-2011年,客户将只需购买一个PA模块就可实现相同功能。”

以3G/4G融合手机架构为目标,TriQuint Semiconductor提供TriQuint一体化移动前端架构(TRIUMF,图3)。该模块提供了由GSM、EDGE、WCDMA和HSPA组成的射频功能。与标准多频段模块方案比,以这种方式,有望将体积减小50%。通过将4个独立PA模块整合在一起,TRIUMF降低了手机组装成本。由于整合了天线开关、模式/频段(开关)、开关和双工器的集成PA模块会减小前端电路板面积,因而可使射频系统小型化。

图3:通过使用集成模块替代多个分立模块,手机制造商可以节省大量空间用于功能设计,如Wi-Fi、GPS、蓝牙、照相机以及收音机等。

虽然CMOS在具成本效益的整合方面有许多显著优点,但在手机应用中,CMOS功率放大器一直无法匹敌或超过砷化镓(GaAs)PA的性能。Javelin Semiconductor的营销副总裁Patrick Morgan解释说,“Axiom Microdevices开发出基于分布式有源变换器(DAT)的2G PA架构,DAT是一种模拟技术。ACCO Semiconductor开发出一种用于PA的称为MASMOS的新晶体管技术。总之,各公司试图解决CMOS PA的挑战的方法主要有以下三种:数字信号处理;新型的模拟架构衍生;对标准CMOS工艺流程进行重大变革。”

针对W-CDMA和HSPA无线通信推出的JAV5001 PA,是采用标准CMOS工艺实现的。JAV5001整合了基带和收发器。在3×3mm封装内,它集成了功率调节、PA偏置、输入和输出匹配以及功率控制电路。JAV5001采用单电源供电。在W-CDMA调制时,其线性输出功率可达28.0dBm。其增益范围从5dB(低功率模式)到27dB(高功率模式)。达到2.5kV的人体模式(HBM) 防静电(ESD)等级。其相邻信道泄漏功率比(ACLR)的典型值是-40dBc(最大值是-38dBc),偏置是±5MHz。在大功率模式,JAV5001的功率附加效率(PAE)是40%;在中 功率模式,JAV5001的PAE是28%。在 2400到2484MHz,其最大噪声是 -150dBm/Hz;在RX频段,噪声是-147dBm/Hz;偏置是190MHz。

随着数字电路能处理或支持的高频功能越来越多,最大的障碍可能在于保持模拟性能。正如TowerJazz的市场营销及业务拓展总监Ramesh Ramchandani指出的:“力促将数字和模拟功能真正集成于一个芯片内的IC设计人员发现,与单独模拟芯片比,要想从数字/模拟集成芯片中获得预期性能是越来越难了。许多工程师在发挥创造力以寻找能弥补模拟性能不理想的电路方案。但是,其中的一个缺点是这里面必须包含一个额外的电路,而且为得到同等性能,可能需要额外增加电容、电阻、电感等无源元件。”这一历时数十年的困境仍“毫不妥协”:集成非常有必要,但不能以牺牲丝毫性能为代价。