0 引 言

带隙基准是所有基准电压中最受欢迎的一种,由于其具有与电源电压、工艺、温度变化几乎无关的突出优点,所以被广泛地应用于高精度的比较器、A/D或D/A转换器、LDO稳压器以及其他许多模拟集成电路中。带隙基准的主要作用是在集成电路中提供稳定的参考电压或参考电流,这就要求基准对电源电压的变化和温度的变化不敏感。

本文结合工程实际的要求设计了一款具有低噪声、高精度且可快速启动的CMOS带隙基准源。采用UMC公司的0.6μm 2P2M标准CMOS工艺模型库进行仿真,HSPICE的仿真结果表明该基准在温度特性、电源抑制比、功耗和启动时间方面有着良好的性能。

1 带隙基准的基本原理

带隙基准的基本原理是根据硅材料的带隙电压和温度无关的特性,利用△VBE的正温度系数与双极型晶体管VBE的负温度系数相互抵消,实现低温漂、高精度的基准电压[1]。双极型晶体管提供发射极偏压VBE;由两个晶体管之间的△BE产生VT,通过电阻网络将VT放大a倍;最后将两个电压相加,即Vref=VBE+aVT,适当选择放大倍数a,使两个电压的温度漂移相互抵消,从而可以得到在某一温度下为零温度系数的电压基准[2]。

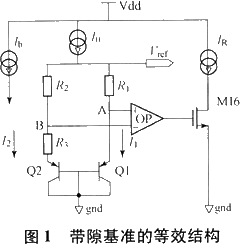

结合图1基准的等效结构图来详细推导此原理。

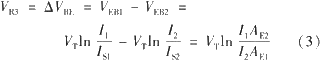

可知一般二极管上电流和电压的关系为[3]:

式中:VT=kT/q为热电压;k为玻尔兹曼常数;q为电荷量。

图1中,R1、R2、R3,以及Q1、Q2构成带隙电压产生器,运算放大器OP和M16为反馈电路,保证A和B点电位相等。

由运算放大器的性质可知:

式中:AE2、AE1分别是Q2和Q1管的发射区面积,它们的比值为N:1。

由于VA=VR,就有,I2R2=I1R1,代入式(3)得:

![]()

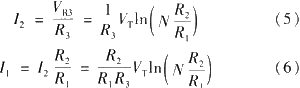

于是就有以下关系:

可得出:

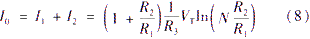

从式(7)中可得到基准电压只与PN结的正向压降、电阻的比值以及Q2和Q1管的发射区面积的比值有关,因此在实际的工艺制作中将会有很高的精度。基准建立后,基准电压与输入电压无关。第1项VEB具有负温度系数,在室温时约为-2 mV/℃;第2项VT具有正温度系数,在室温时约为+0.087 mV/℃。通过设定合适的工作点,便可以使两项之和在某一温度下达到零温度系数,从而得到具有较好温度特性的电压基准。

图1中Ib是基准提供给其他模块的电流,与I0成比例,而I0为:

2 基准实际电路的实现与分析

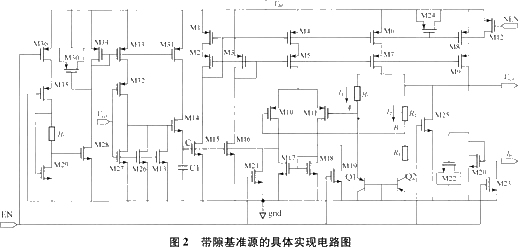

本次设计的带隙基准的实际电路如图2所示。运算放大器OP的构成如下:差分输入级M10、M11,有源负载M17、M18,Cascode电流偏置M4、M5,M15和M16为第2级放大。

R1,、R2、R3和Q1,Q2及运算放大器构成带隙基准核心电路。Cascode电流镜[4]M3、M2、M1、M6、M7、M8、M9以及M4和M5构成整个基准模块的偏置电流源,具有高输出阻抗的特点,稳定性好。M20为cas-code电流源的负载。M12、M19、M21、M23和M25是使能管,对输入的使能信号进行逻辑反操作,从而决定电路工作与否。C1是第一级与第二级放大器之间的补偿电容,保证了稳定性;同时它还是电路软启动电容。

2.1 基准的使能原理

EN为高电平时,使能关断有效。只要EN高电平时,NEN为低电平,则使能管工作,整个电路中的偏置电流源被关断,有源负载截止而呈现非常高的阻抗。为了防止晶体管Q1,Q2的BE结有能量储存,M25保证Vref完全为0,M23保证,Ib电流完全为0,电路完全关断。EN为高电平时,使能管截止,电路正常工作。

2.2 基准的启动原理

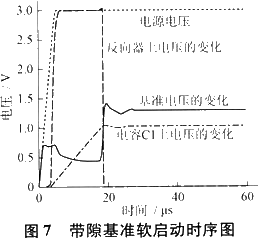

该电路中利用电容C1进行软启动[5]。系统刚上电,基准启动模块通过信号线对电容C1充电,直到C1上的电压使M15和M16导通,基准模块的电流偏置建立起来;从而使运放工作,基准开始启动,当基准电压达到一定值(一般为O.9 V左右),启动模块被关闭,没有电流从启动模块输出,此时电容C1作为频率补偿电容;所以经过一段时间(25μs左右),这个闭合回路将达到稳定,基准建立起来,最终值为1.293 V。

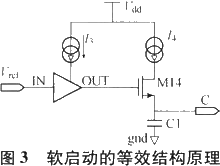

2.3 基准软启动的实现

基准的软启动的等效结构如图3所示。其中电流源I3、,I4为电路提供较稳定的偏置电流,带隙电压Vre通过非门得到Nref控制M14的工作状态。芯片刚上电时,基准源电路没有启动,Vref为低电平,经过"非"后Nref输出高电平,M14饱和导通,I4给基准模块的电容C1充电,当电容上的电压达到0.9 V左右后,基准模块开始工作,Vref电压升高,达到1 V左右时Ⅳ耐变为低电平,使M14截止,停止对电容C1充电,软启动完成。

实际的电路图如图2中左半部分所示。EN是使能控制信号,控制该部分电路偏置电流的产生。M29、M28和R5组成峰值电流镜,并与M35、M36构成了带使能控制的自偏置电路;M32、M27、M26、M13组成了一个非门,M31提供启动电流,I4,M14作为一个开关,决定,I4是否对电容C1充电。

2.4 基准中器件参数的选取

要适当地选取元器件参数,调节出合适的工作点,实现25℃时零温度系数的1.293 V带隙基准,而且要求低静态电流。

由式(7)知,当工艺确定后,微电流工作状态下,VEB及其温度系数可以确定[6];N一般选取4、6、8、10,但是从版图布局来考虑,N=8最理想,如果要减小版图面积,也可考虑N=4。

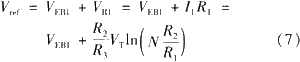

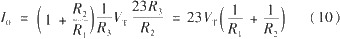

下面推导电阻R1、R2、R3的取法。为了满足零温度系数,对等式(7)两边求导,考虑了VER和VT的温度系数,近似得:

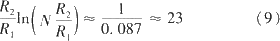

代入式(8)得:

因此,如果要使,I0较小,而且(R1+R2)较小(这样版图面积小),则需要折衷考虑(两者矛盾),比如选取R2=R1,则,I0较小而(R1+R2)较大,一般来说,选取R2=2R1左右较合适。如果N=8,则根据式(9)可得:

![]()

从而有:

设计时,需要根据静态电流的要求确定电阻值。

3 版图设计时的考虑因素

版图设计在模拟集成电路的设计中非常重要,它往往决定着电路的性能,所以在本次设计中充分考虑了器件的匹配性及版图的布局和布线等问题。

首先,在绘制面积比为N:1的Q1和Q2 PNP晶体管时,采用3×3阵列,Q1位于阵列的中央,其他8个等面积并联的PNP晶体管环绕Q1形成Q2,这样可以增强匹配,减小失调[7]。

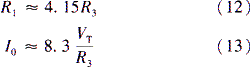

其次,无论对于正或负温度系数的量,在前面推导出的与温度无关的电压都是依赖于双极型器件的指数特性,所以必须在CMOS工艺中找到具有这种特性的结构。在N阱工艺中,PNP晶体管可以按图4所示结构构成。N阱中的P+区(与PMOS的源漏区相同)作为发射区,N阱本身作为基区,P型衬底作为PNP管的集电区,并且必然接到最负的电源。

最后,在集成电路的制造中,电阻值的误差很大,电阻间的比值误差对电路的温度补偿特性具有很大的影响[8]。所以,为减小电阻的比值误差,对电阻进行了对称的排列。同时,为了防止周边环境的影响,在电阻的周围加上dummy,这样就提高了电阻的匹配度。

4 基准源的仿真

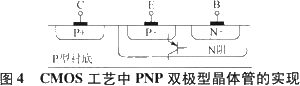

本设计采用UMC公司的0.6μm 2P2M标准CMOS工艺模型库进行仿真,在此模型库中,NMOS阈值电压为+0.883 V,PMOS阈值电压为-0.873 V。在电源电压为3 V时,输出的基准电压在-40℃~120℃的温度范围内的变化约为4.41 mV。图5中给出了电源电压Vdd分别在1.5 V、3 V和4 V时基准的温度特性的仿真结果。

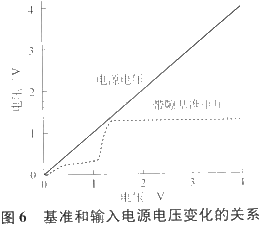

图6给出了基准在0 V~4 V的电源电压范围内基准随电源电压变化的仿真结果,从图中可以看出在1.5 V~4 V的电源电压范围内基准输出为1.293 V,随输入电源电压变化的最大偏移为0.27 mV。

图7为基准启动过程的仿真曲线。可以看出,基准从电源上电到稳定输出的启动时间约为25μs。

最后,还对基准的电源抑制比、功耗和噪声特性进行了仿真,仿真结果表明基准具有较高的电源抑制比,小于500 nV/Hz1/2的噪声,并且在电源电压为3 V时,基准总电流约14.25μA时,功耗约42.74μW。

5 结束语

本义在分析典型的带隙基准的原理的基础之上设计了一种结构新颖、工程实用的带有软启动功能的带隙基准源。在输出参考电压为1.293 V、温度为25℃时对其进行丫一阶温度补偿,采用UMC公司0.6μm2P2M标准CMOS工艺模型库进行仿真,HSPICE模拟表明该电路在精度、稳定性、功耗、电源抑制比和噪声方面均达到了没计要求,软启动的时问也在没计的要求范围之内,可广泛应用于多种模拟集成系统中。