引言

超声波流量计是随着IC技术迅速发展而开始得到实际应用的一种非接触式仪表。它是一种利用声学原理工作的新型流量测量仪表。与传统流量计(如孔板、涡轮流量计等)相比,它具有测量准确度几乎不受介质温度、压力影响等优点,尤其是在大管径流量测量方面,其优越性更加明显,因此得到了越来越广泛的应用。

近年来,随着Altera公司32位软核CPU NiosII的推出,基于FPGA的SOPC(System On a Programmable Chip)技术发展越来越快。SOPC是可编程系统,具有灵活的设计方式,并且可裁剪,可扩充,可升级,同时具备软硬件在线系统可编程的功能。SOPC兼具PLD和FPGA的优点,它的特点包括:至少包含一个嵌入式处理器内核;具有小容量片内高速RAM资源;有足够的片上可编程逻辑资源;有处理器调试接口和FPGA编程接口;可能包含部分可编程模拟电路;单芯片,低功耗,微封装。正是基于这些优点,基于NiosII的SOPC得到了越来越广泛的应用。

本文就是基于超声波以及SOPC这两项技术来设计便携式的超声波流量计,充分发挥这两项技术的优点,实现对液体、气体的高精度测量。

1 工作原理及系统组成

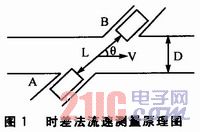

本系统利用时差法进行流速测量:安装于被测容器顶部的收发一体的超声波换能器(A或B)通过空气向被测物体发射一束超声波,该声波经被测物体反射后,回波被换能器(B或A)接收并被转换为电信号。原理图如图1所示。

这样,在已知安装角度θ和管径D的条件下,测量A到B的传播时间tAB以及从B到A的传播时间tBA,通过计算可得

![]()

这种算法只需测出tAB与tBA就可以得到流速V,而通过对流速进行积分运算就可以进一步算得流量,这就是时差法测量流速的基本原理。

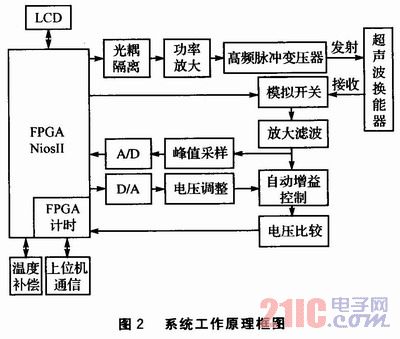

整个便携式超声波流量计系统组成如图2所示。系统由脉冲发射电路、回波接收电路、信号处理电路和CPU控制电路组成。脉冲发射电路是输出一定超声波频率的脉冲激励信号经功率放大和升压后驱动超声波换能器发射超声波;回波接收电路即是接收回波信号;信号处理电路用于对回波信号进行放大、带通滤波、自动增益控制、电压比较等处理;CPU控制电路控制发射信号、控制模拟开关、捕获计时、数据处理及与外部设备通信。

2 模拟电路部分设计

2.1 超声波前端驱动电路

如图2所示,超声波换能器驱动电路产生一个具有特定频率、脉冲宽度和输出功率的电脉冲去激励超声波换能器,进而产生超声波向外发射。对于超声波换能器,超声波换能器驱动电路提供的功率越大,超声波换能器将电能转换为声能的效果越好,所以超声波换能器驱动电压应该越大越好,但需要注意驱动电压压值不能超过换能器压降极限。本系统应用晶体管组成推挽式电路结合场效应管电路来实现功率放大。

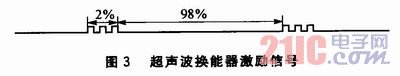

系统超声波换能器驱动信号是由微处理器产生的,微处理器产生一个200 kHz的矩形脉冲信号,经光耦隔离后进入功率放大电路。根据换能器的特点,该矩形脉冲信号占空比为2%。超声波换能器激励信号如图3所示。

2.2 超声波信号处理电路

超声发射换能器发射的超声波信号,经过管壁和流体,衰减比较大,因此超声波接收换能器接收的信号比较微弱,通常只为几十mV数量级,这时放大器的噪声对测量精度的影响也比较大。同时,由于超声波流量计中使用的超声波频率较高,所以要求运算放大的增益带宽积足够高,因此该级电路采用低噪声高速运算放大器。本系统中选用MAX410作为放大器。

在超声波流量计工作的过程中,由于振动、流动及工业现场的管道噪声和变频设备的电噪声等电子干扰,会引起周期性的噪声信号出现,并导致在相关图上出现周期性波峰。当其叠加到流动噪声的相关曲线上,会使真实的渡越时间对应的波峰不明显,甚至被其他的波峰掩盖,无法得到正确的测量结果。通过低噪声高速运算放大器对信号进行放大后还需要对信号进行滤波。本系统中的滤波电路为带通滤波。系统中换能器发射接收的超声波中心频率为200 kHz,所以需要设计一个中心频率为200 kHz的带通滤波器,它可以使200 kHz的超声波信号顺利地通过,而阻止或衰减非200 kHz的超声波信号及其他干扰信号。

另外,超声波信号在管道中传输时,由于各个声道长度不同,传感器特性存在差异,气体介质不同以及测量时气体流速的变化,导致每次测量时传感器接收信号的幅度也不同。为了后端进行高精度的计时,需要自动增益控制对接收信号的大小进行调节,使接收信号有一个稳定的幅度,从而满足系统测量高精度的要求。

3 数字电路设计部分

3.1 概述

本系统数字电路设计部分的核心是FPGA。在本系统中FPGA主要实现两部分功能:一是实现高精度计时,为准确测量流速提供保证;二是通过构建软核CPUNioslI来实现对整个系统的控制。本系统选用Altera公司Cyclone II系列的EP2C8Q208C8N芯片。

关于计时这里不再赘述,主要就是通过MEGA WIZARD调用PLL模块实现倍频到200 MHz然后供给计数器模块来计数,计数结果通过移位寄存器来上传给CPU,再通过CPU处理后传给上位机。

NiosII是32位RISC嵌入式处理器,它是Altera公司的第二代FPGA嵌入式处理器,其性能超过200DMIPS,在Altera FPGA中实现仅需35美分。特别是,NioslI系列支持使用专用指令。专用指令是用户增加的硬件模块,它增加了算术逻辑单元(ALU)。用户能为系统中使用的每个NiosII处理器创建多达256个专用指令,这使得设计者能够细致地调整系统硬件以满足性能目标。NiosII系列支持60多个外设选项,开发者能够选择合适的外设,获得最合适的处理器、外设和接口组合,而不必支付根本不使用的硅片功能。基于其嵌入式的特点以及其成本,NiosII特别适用于便携式仪表方面的应用。

3.2 SOPC的硬件构建

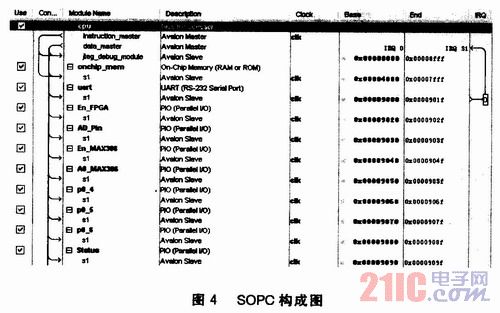

通过Quartus中的SOPC Builder来构建SOPC系统。首先要添加一个CPU。为了节省片上资源,选用经济型的CPU,外部晶振是50 MHz。程序运行内存直接选用0n-Chip Memory,因为EP2C8Q208C8N片上的RAM空间大概有20 KB左右,通过优化,片上内存完全能够满足程序的需要,这样就不必添加外接的SDRAM芯片,减少了PCB板的面积,大大降低了成本。代码优化方法是通过NioslI IDE里面的System Library Proper-ties来设置:依次选中Program Never Exit,Small C Library,Reduced Device Drivers,Lightweight Device Drivers API,取消选中

Support C++并设定Optimize Size为-0s级,这样就可以有效的缩减程序代码。

另外,为了向上位机传递测试数据,需要添加UART。这里添加的UART只是一个协议,与上位机实现通信,还需要在外围添加电平转换芯片MAX232以实现与上位机的正常通信。

为保证系统正常运行,添加内部定时器实现看门狗功能,另外需要添加的就是一些PIO接口。能够产生中断的PIO口注意要分给一定的中断号。CPU的Reset Vectot。地址和Exception Vector地址都设为On-Chip Memory,并让系统自动分配基地址以及中断。点击Generate生成整个SOPC,图4即为整个SOPC的构成图。

3.3 用Niosll IDE编写整个系统的控制程序

NiosII IDE(Integrated Development Environment,集成开发环境)提供了完整的C/C++软件开发套件,包括编辑器、项目管理器和构建工具、调试器和兼容CFI(Common Flash Interface)的Flash编程器。调试器连接多种目标系统,包括FPGA硬件(通过JTAG电缆)、NioslI指令集仿真器和Modelsim-Altera软件,因而能够提供最灵活的调试方案。

为了方便用户编程,NiosII为用户提供了设备驱动程序,也就是硬件驱动层数据库HAL。软件编写人员只要利用HAL提供的各种函数就能编写应用程序,从而方便地与底层硬件进行通信,而无需关心底层硬件的实现细节。HAL系统库可在IDE创建一个新工程时,由系统自动生成。

NioslI IDE完全支持C/C++,本系统采用的编程语言是标准C。添加必要的头文件,编写各个中断服务程序以及子程序,就可以实现整个超声波流量计的控制。

仿真NiosII设计包括3种方式:“NiosII IDE Debugger+Signal Tap II+物理板”的软硬件联调方式,“NiosII IDE Debugger+指令集仿真器ISS”的软件调试方式(ISS可对部分组件建模),使用Modelsim-Altera进行的RTL级的功能仿真方式(可以调试处理器及其外设之间的交互情况)。Debug的方式可以通过IDE里面的RunDebug As进行选择。NiosII IDE也可以进行设置断点,单步调试,观察变量,内存以及表达式的值等操作,在此不一一赘述。Debug之后还需要建立工程,若整个系统无错,可以生成一个ELF文件,只有完整建立起来的系统才可以下载到FPGA的板上运行。具体实现方式是通过NiosII IDE里面的Project-Build Project来建立工程,结果会提示程序代码总共占用了多少代码,剩余多少的RAM空间,以及错误和警告提示。根据错误警告提示修改代码,直至无错完整地建立工程,这样NiosIIIDE里面的工作就全部完成了。通过FPGA下载线将程序下载到FPGA板上,整个系统就可以完整地运行。

4 实验结果及分析

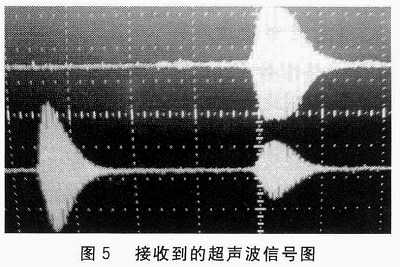

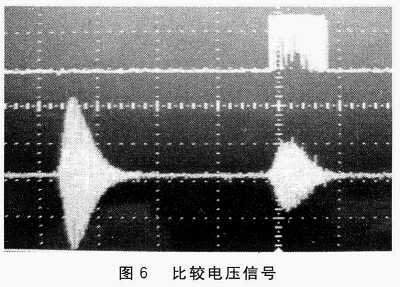

将程序正确下载到FPGA板上,硬件正确连接,接上超声波探头,进行实验。实验结果表明,本系统可以准确地实现对整个系统的控制,经过信号处理的超声波信号清晰稳定,实验结果能够满足系统的精度要求,效果良好。图5即为实验现场接收到的超声波信号。图6为比较电压的信号图。

图5中下方是经过滤波之后的超声波的发射和接收信号。可以看到信号清晰稳定。上方的信号是经过自动增益控制之后的超声波回波信号,通过自动增益控制之后的接收信号可以稳定在一定的幅度之内,保证了系统对高精度计时的要求。

图6中下方也是滤波之后的超声波发射和接收信号。上方的信号为电压比较器所产生的计时停止信号。当通过自动增益控制之后的接收信号达到电压比较器的参考电压时,电压比较器便会产生一个计时停止信号,并发送给FPGA,这样计时停止,便准确地测量了超声波的传播

时间。

实验结果表明,本系统可以准确地实现对整个系统的控制,经过信号处理的超声波信号清晰稳定,实验结果能够满足系统的精度要求,效果良好。