O 引言

在各种基于PCM30/32路一次群系统、能够接入公共电话通信网的专用汇接调度设备中,目前广泛采用的设计方式为利用MCU控制多种专用集成电路(ASIC)协同工作,完成对语音调度数据的接收、叠加、分组交换等操作,此类设备在可实现功能和用户规模等方面都受到所采用ASIC本身功能特性的限制,因此,虽然针对某一特定应用的汇接机、调度机品种很多,但仍很难满足所有的应用需求,对于一些特殊功能需求往往要进行单独设计,在很大程度上增加了用户的使用维护成本。

近年来随着通讯技术和集成电路技术的发展,可编程逻辑器件及SoC设计在各种应用设计中大量被应用,在通信系统中,可编程逻辑器件的应用范围同样越来越广。利用可编程逻辑器件相对于使用独立器件进行语音调度数据编解码、交换叠加等处理操作,在提高系统性能与集成度以及降低成本方面均有极大优势。同时,利用可编程逻辑器件能够针对应用需求进行系统设计,突破传统设计方式受器件限制较大的弊端。

对实现语音调度功能的可编程逻辑芯片来说,时钟信号的同步可以有两种模式:主模式和从模式。如果是在已有的交换平台或通讯系统上增加设计其他语音调度功能,则已有外部时钟系统难以被改变也不宜改变,这时语音调度电路应采用从模式来同步。而对于全新设计的语音调度设备来说,就可以采用主模式的时钟同步模式,由可编程器件产生时钟及同步信号供芯片本身和外围电路器件使用,使得外围电路设计更为简洁。

在时钟同步采用从模式设计方式时,芯片需要从接收到的串行数据流中提取时钟信号以便正确可靠地进行串行数据流接收,这是汇接调度设备接入已有通信网络进行语音调度数据处理的首要条件。

针对这个问题,文中介绍了一种从串行PCM数据流中提取同步时钟的方法。

1 PCM一次群数据流同步时钟提取方法

1.1 同步时钟提取基本设计

我国和欧洲在电话语音通信使用PCM30/32路一次群传输系统中,通常串行数据速率为8 000帧×32时隙×8 =2.048 Mb/s,实际应用的各类语音调度系统中数据传输大都以该速率进行。在PCM串行数据流中,各码元之间的相对位置是固定不变的,为了在数据流中区分出一个个的数据码元,接收端必须具备对应数据流的同步时钟信号,从而进一步正确接收PCM串行数据。

接收端数据流同步时钟信号提取功能模块基本工作原理是以一个3位计数器count1对16.384 MHz(PCM串行数据流速率8倍)全局时钟信号进行8分频,计数器最高位作为同步采样时钟信号输出,由全局时钟上升沿驱动。在计数值跳变至0和4时,分别输出同步时钟的下降沿和上升沿。

作为常用时钟源的石英晶体振荡器具有比较好的长期频率稳定性,但作为全局时钟输入在产生同步时钟过程中,由于晶振实际频率与标称频率相对偏差所产生的误差随时间推移而累积,造成本地同步时钟相位漂移(相对于串行数据流中包含的时钟信息),所以需要不断调整输出同步时钟相位才能够保证接收过程不出现失步,这一点通过在分频计数过程中调整计数器count1的计数值来实现。

进行相位调整时,在全局时钟驱动下检测到一个PCM信号上升沿到来后,即在一个码元的开始时刻,改变分频计数器count1中计数值为0,继续计数到4时同步时钟上升沿出现,其位置在PCM数据流一个码元范围的正中间,从而保证时钟信号相对于输入数据流具有合适的建立时间和保持时间。

实测某型16.384 MHz晶振偏差约每周期4 ns,为保证采样时的信号具有较好的建立时间与保持时间,确定每20~30个周期做一次输出同步时钟相位调整。设计中使用5位计数器count2定时,该计数器计数值超过20进行相位调整。

1.2 时钟信号提取过程异常情况解决

上述从已知数据速率的PCM数据流中提取采样时钟并进行相位校正的基本方法在使用中存在以下两个问题:

(1)计时计数器值超过20后,系统在全局时钟驱动下进行PCM信号上升沿检测过程中,计时计数器count2依然工作,当该5位计数器值达到31而依然没有检测到PCM信号上升沿到来时,下一个时钟到来时计数器值将复位为0导致错过本次校正。

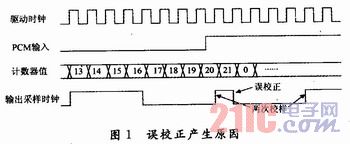

(2)在同步时钟相位出现很大偏差时,若PCM输入信号在某全局时钟上升沿过后很短时间到来,同时分频计数器输出同步时钟上升沿随后出现,接收系统将对该码元进行一次采样,此时,若紧随其后的全局时钟上升沿检测到该PCM信号上升沿且计数器count2值为21,就会误校正输出同步时钟相位,出现如图1所示情况,同步时钟上升沿在本码元内出现两次,一个PCM输入高电平码元被采样两次,产生接收错误。

上述两种情况中,出现第一种会造成采样错误影响信号的后续处理,第二种情况则会造成采样时钟相位校正错误,导致信号采样失败。

针对这两种情况,需要对基本方法进行进一步完善,设计中分别给出如下方法来解决:

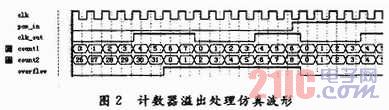

(1)针对计时计数器溢出情况,在提取模块中设置一个溢出位overflow,在count2溢出时置位为1,此时,全局时钟检测到下一个PCM输入信号上升沿时忽略计数器计数值立即进行相位校正,以推迟校正代替漏校正,达到改进系统工作性能的目的。添加该处理过程后,系统对相应情况校正结果如图2所示。图中count2计数器溢出后overflow置高电平,在遇到下一个PCM输入信号上升沿时立即校正输出时钟相位,未考虑count2中计数值为8小于20的因素。

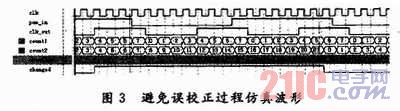

(2)针对采样输出时钟的误校正情况,在功能模块中设置一个标志位changed,当某PCM高电平码元内已经发生采样时钟的上升沿跳变changed位置1,这时,在该码元未结束前不再进行校正,changed标志位置位后在计时计数器计数值大于20时清除。如图3所示。

经过上述的异常情况的处理程序,同步时钟提取功能模块将能够正确地从输入的PCM数据流中得到准确的具有合适相位的采样时钟输出供接收数据使用。

2 同步时钟提取过程编程实现及仿真结果

同步时钟提取模块的声明代码如下:

输入端口为pcm_in,clk和reset,分别为PCM输入信号,全局时钟输入和复位信号,输出端口仅一个,clk_out采样时钟。

模块中两个计数器count1和count2,分别为前述分频计数器和计时计数器。

三个标志位:run,changed和overflow,后两个在第二部分中详细介绍过功能,run标志位为模块工作状态标志位,run位置1模块运行;changed标记本码元采样状态,已经采样过则该位置1;overflow标记计时计数器溢出状态,已溢出则该位置1。

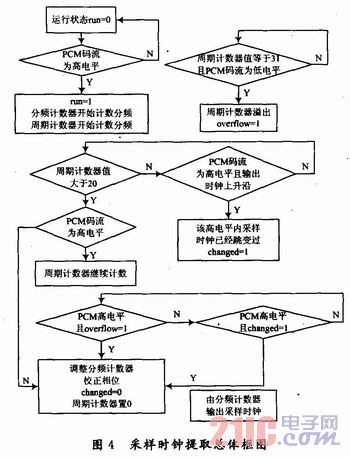

模块使用同步时序设计方式实现,所有工作在输入全局时钟信号clk上升沿的驱动下进行,包括复位功能同样为同步工作。在clk驱动下,复位信号低电位时系统复位,各寄存器进行初始化工作置初值,复位信号结束后,run标志位置1模块开始工作。系统模块框图如图4所示。

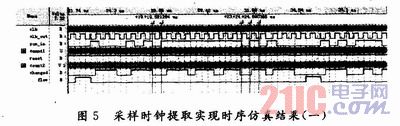

以Altera的EPM7128SLC84型CPLD作为目标器件,在集成开发环境QuartusⅡ中对上述VerilogHDL语言描述的时钟信息提取模块编译综合布局布线后进行时序仿真,得到仿真波形如图5所示。

为了方便对异常处理功能进行验证,仿真时使用输入时钟约为PCM码流速率的7.5倍,由图5中可以看出,设计对于输出采样时钟校正有很明显效果。

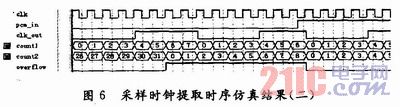

图6中则是使用完全8倍时钟输入的仿真结果,结果完全符合设计目标。

3 结论

本文中给出的串行数据流采样时钟提取方法及其实现,不仅局限于文中所特定语音通信PCM30/32路系统,对类似的已知速率串行数据流异步接收系统均适用。该方法能够有效地提取出数据流中包含的发送端时钟信息,并消除接收端本地时钟与之相位偏差、时钟频率偏差等因素导致的工作稳定性不高以至接收数据错误等不良结果,具有较好的适应性。