千兆位背板总线测试方法

2008-12-11

作者:严 挺 方志来 安 琪 王砚方

摘 要: 简要介绍了千兆位" title="千兆位">千兆位背板总线的一些关键问题;详细讨论了几种行之有效的千兆位背板总线测试方法,包括波形观测、误码率测试、眼图" title="眼图">眼图和时域反射计等;给出了一个实际的千兆位背板总线系统的测试结果。

关键词: 千兆位背板总线 误码率 眼图 时域反射计

背板是互连技术在印刷电路板上的实现,一般是无源的。背板上有用来插卡的槽,槽与槽之间有各种形式的总线。在背板的插槽中插入各种卡,即构成计算机和各种处理机,所以说背板是嵌入式系统的硬件平台。由于传统的共享总线在某一特定时刻只允许同时被一对端口使用,因而各端口分配到的平均带宽较少,所以应用受到了很大的限制。随着对总线带宽要求的不断提高,人们将注意力更多地转向空分总线。空分总线允许多端口同时通信,端口越多总计带宽越高,具有很好的可扩展性,而可扩展性正是通信系统所必需的。由于通信系统中普遍采用串行传输方式,所以通信系统中采用的空分总线也多采用串行方式。点到点的串行传输方式可以获得很高的传输率,且越来越多地被用于处理器、存储器和I/O设备间的互连之中。高速(指千兆位以上)的背板总线已经成为高速互连技术中的一个重要方面[1]。不仅通信领域,计算、控制等领域对背板技术也提出了越来越高的要求。

千兆位背板总线的高速电路系统对系统的测试提出了挑战。由千兆位系统的特征时间1ns和真空光速3.00E+8m/s的乘积,得到的波长的量级约为0.3m,这与一般背板的长度在同一量级;如果考虑到信号的上升沿约为0.2ns,则估计出的波长在0.06m量级上,这和一般的PCB板走线在同一量级。这样,数字信号的传输线效应和模拟效应就不可忽略了。传输线效应和模拟效应的影响,使得高速数字电路设计对阻抗特性、时间参数和信号质量提出了严苛的要求,这样,对它们的测量,就成为一个重要的课题[2]。

1 千兆位背板总线系统简介

随着串行数据传输率的不断提高,数字信号和模拟信号间的界线模糊了。为了提供传输所必须达到的低误码率,必须保证良好的信号完整性;而为了达到信号完整性的要求,必须仔细考虑元件的选择、电路板的设计。因此,应该对传输线效应、电磁兼容性、噪声、串扰和时钟分布等诸多问题有清晰的认识并将这些知识运用到实际设计中去[3]。

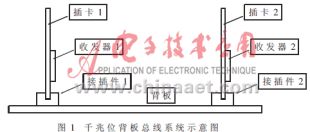

其中,在设计中必须对三个方面予以特别的重视:收发器" title="收发器">收发器、接插件" title="接插件">接插件和背板PCB设计,它们在整个千兆位背板总线系统中,有着举足轻重的地位。而对千兆位系统的测试,则与这三个方面密切相关。千兆位背板总线系统示意图如图1所示。

收发器:收发器(transceiver)是系统中的核心器件。差分信号LVPECL是一种比较通用、性能较好的信号形式。一般希望收发器能提供多通道双工数据传输,以能够达到较高的总计带宽。通常采用相对低速的参考时钟,在片内进行频率合成。传统上使用8B/10B的编码方式,要求收发器能够在很短时间内实现位同步、字同步和或通道同步。还要考虑时钟的驱动和分配问题、时钟的偏差(skew)和抖动(jitter)特性。对芯片电路的一些细节问题,如阻抗匹配、交流耦合、功耗、与上游/下游电路的接口等也应该加以充分与仔细的考虑。

接插件:接插件是背板与插卡的连接部分。由于通孔(via)和短线(stub)引入阻抗不连续性,并产生串扰、共模噪声、衰减和额外的抖动,因此影响信号完整性和误码率。所以接插件的评估和选择对于确保高速背板系统的性能至关重要。可以通过时域反射计测量接插件各点的特性阻抗,来选取各点特性阻抗变化较小且平滑的接插件。通常采用在信号引脚周围排步地引脚的“伪同轴结构” 来减少串扰、共模噪声。还应考虑接插件的机械性能。

背板PCB:背板是一种装有插座、通常安装在机箱背面的完成插卡间信号传输的电路板。由Nyquist公式可知,1.25Gbps数据速率的总线至少应有625MHz的带宽。在如此高的带宽要求下,千兆位背板PCB设计与低速背板设计有着显著的区别。为减小地反弹和共模干扰并满足电磁兼容性要求,背板应采用差分信号,差分信号耦合方式有边沿耦合(edge coupled)和宽面耦合(broad coupled)两种。

依据以上原则,我们成功地设计了一个千兆位背板总线传输系统,总计带宽达到1.25G×4=5Gbps,考虑采用各种测试方法对这三个方面的性能加以全面细致的测试。

2 千兆位背板总线系统测试方法

总线系统测试包括以下几个方面:波形观测、误码率测试、TDR阻抗测试和眼图测试。

2.1 波形观测

波形观测的内容包括信号的上升/下降沿、幅度、抖动、过冲等等。采用的主要仪器为数字存储示波器(DSO)。

通过测量信号在收端和发端的幅度值,可以计算出被测信号在传输系统中的损耗百分比。该损耗与系统的带宽有着直接的关系,而且收发器也要求信号摆幅超过噪声容限,否则会出现误码。收发器对信号的抖动和上升/下降沿宽度也提出要求。

由于串行信号速率很高,因此对示波器的要求也相当高。主要表现在采样率和带宽(包括示波器本身的带宽和探头带宽)两个方面,其中带宽是最为关键的。示波器带宽应为被测系统最高频率成分的3到5倍。系统的上升时间" title="上升时间">上升时间在频率成分中起着主导作用,而不是时钟频率。信号带宽可用0.35除以上升时间(10%到90%)来估计,这个关系是基于主极点近似的,所以对应特性不同的系统该参数可以高至0.4或0.5。如果上升时间按照20%到80%计算,则因子0.35应当换成0.22。示波器带宽为信号带宽5倍时,产生0.2%误差,但是如果与信号带宽相等,则会产生41%的误差[2]。而千兆位系统的上升时间在200ps量级,这对示波器的带宽提出了严苛的要求。依据一阶主极点近似及卷积特性,在考虑进示波器及探头的带宽影响以后,测出的上升时间[4]为:

其中T1为信号的上升时间,T2和T3为示波器和探头的上升时间。

从上式中,我们看出示波器的探头也会影响测出的信号质量。因为探头会带入阻性和容性成分,而探头的接地线还会引入感性负载,这样也会带进一个时间常数。所以在测量中,应该采用尽量短的探头和接地线,并使接地点与测试点尽量接近,以免形成比较大的回流。

在千兆位背板总线测试中,主要观测收发器引脚或者其直接引出线上的信号质量和接插件引脚上的信号质量,通过观测可对收发器的性能与接插件、总线的传输性能有一个大致的了解。

2.2 误码率测试

误码率即出现错误比特的概率,是数字信号传输系统应该测试的一个基本性能。位误码率(Bit Error Ratio)定义为:

误码率测试一般要求采用标准的伪随机二进制码序列(PRBS — Pseudo-Random Binary Sequence),这种码型重复周期很长,在较短序列内可以近似地看成是随机并与实际通信业务类似的码型,因而比之重复码型更为可信。误码率测试系统的框图如图2所示,其中的两个伪随机码发生器产生的伪随机序列要求一致。

误码率测试可以采用通用的误码特性分析仪。如果没有通用分析仪,也可以针对某一特定的系统用硬件电路实现误码率测试。比如针对千兆位背板总线系统可以组成如图3所示的系统。

该测试系统采用相对低速的数字信号处理器(DSP)向SRAM存储器写入随机码型,再通过高速的可编程逻辑器件从SRAM内读出码型发往发送器的输入端口,在千兆位背板总线系统上传输,在接收器的输出端口用高速的可编程逻辑器件写入SRAM,其后再从SRAM读入DSP,进行误码分析。现已证明这种方法是行之有效的。

2.3 TDR测试

TDR即时域反射计(Time Domain Reflectometer),时域反射计采用一个信号发生器在传输线的一端加一个上升沿很快的阶跃波,然后在传输线上某点用示波器测量入射波和反射波的波形。时域反射计技术能够显示被测传输线上各点的特性阻抗及线上各点阻抗不连续处的位置和特性(阻性、容性还是感性)。TDR可以用来测试传输线上的开路、短路以及相邻传输线间的串扰。在光传输系统的维护中,可以用光时域反射计来检测光纤的断裂等故障,也是基于这一原理。在测试背板时,可以安装SMA插头与TDR示波器相连接以便于测试。测试差分信号的特性阻抗及共模和差模反射采用差分时域反射计(DTDR—Differential TDR),可以采用双阶跃波发生器来激励,也可以采用单阶跃波来激励。对于千兆位背板总线来说,可以通过TDR来测背板总线的特性阻抗和接插件的阻抗不连续特性,有很重要的参考意义。图4是一个终端开路TDR图样,其中横坐标是时间,纵坐标是幅度,也可以是反射系数ρ[5]。

2.4 眼图测试

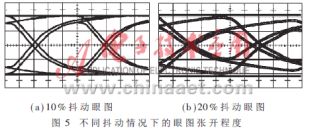

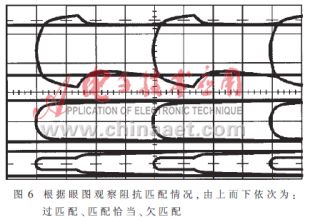

眼图(Eye Pattern)是在示波器或专用的眼图测试仪上把多段伪随机码波形重叠形成的图形,用来测试信号质量。对于各种标准速率,都有相应的模板。所谓模板,是眼图测量中的一个区域,合乎标准的眼图要求不能有波形进入这个区域。从眼图上可以看出信号的上升沿、下降沿的快慢和抖动的大小。信号上升/下降得越快、抖动越小,眼张开得越大,如图5所示。眼图的张度(opening)与误码率之间有着直接的联系,张度越大,则误码率越小。还可以通过观察眼图得出终端匹配电阻的匹配程度,如图6所示[6]。

3 一个实际系统的测试结果

通过以上几种方法,我们对设计的千兆位背板总线系统进行了测试。

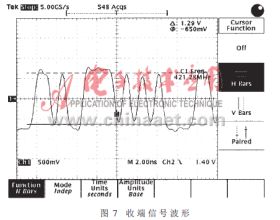

3.1 波形观测

图7给出了收端信号的波形。在测试中,由于条件所限,我们使用的示波器本身带宽为1GHz,采用的差分探头带宽也为1GHz,这样得出的综合带宽约为700MHz,示波器引入的上升时间(20%到80%)约为300ns,而正常情况下接收器和发送器信号的上升时间也应在这个量级,所以测出的上升时间误差较大。示波器的带宽限制也会影响到测出信号的幅度。测试中我们尝试采用各种长度的探头、接地线和不同的接地点,观察到长探头、接地线和离被测点较远的接地点都会引起测出信号的波形性能变坏。所以在测试中采用最短的探头和接地线、离被测点最近的接地点。比较收端和发端的波形,可以得出信号通过接插件和背板的幅度衰减,本系统的幅度衰减在10%之内,能够保证收端无误接收,是令人满意的。也可以通过比较收端和发端的上升时间估算出系统的带宽,采用如下公式:

其中Triserec为收端上升时间,Trisetrans为发端上升时间。由于公式中两者平方后相减,抵消了示波器和探头有限带宽的影响。按此公式算出本系统带宽约为1GHz,基本上保证了1.25Gbps信号传输的可行性。

3.2 误码率测试

我们设计了一个误码率测试系统,系统框图如图3所示,并采用DSP编程实现了一种简单有效的伪随机信号序列,伪随机信号长度为32K。系统在测试中运行良好。测出系统传送6、000、000包无误码(每包为32K数据,数据为1Byte),计算出系统误码率在10-12以下,这是相当令人满意的。

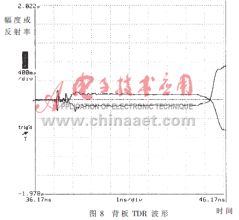

3.3 TDR测试

由于本系统的高速信号线采用的是差分信号形式,所以采用差分TDR,双阶跃波激励。图8是测得的TDR波形。图中,横轴坐标为时间,纵轴坐标为信号幅度,也可以是反射率ρ。可以看出背板信号线特征阻抗较为连续(前端的不连续处分别为测试头与接插件引入,后端是终端开路波形)。连续的背板特征阻抗对传输是有利的,因为可以减少信号在背板上传输时的反射。从TDR可以测出背板特征阻抗的数值。本背板的特征阻抗约为82Ω。

3.4 眼图测试

图9是本系统在接收端的眼图。该眼图由伪随机信号迭加约2000次形成,其中没有一次进入标准的千兆位以太网眼图模板,该模板眼图张度为50%;而我们的收发器只要保证接收到的信号能达到24%的眼图张度就能完成BER低于10-8的信号传输,由此可见,本系统信号完整性性能远超过收发器的要求。从眼图中可见,信号线匹配电阻略为偏大。这也与实际的电阻与信号线特性阻抗的匹配情况吻合。

千兆位背板总线系统由于其信号速率高,导致了不可忽略的传输线效应和模拟效应,具有低速总线系统所不具备的一些特点,所以设计中要对一些关键之处加以特别的考虑,也对测试方法提出了新的挑战。新的测试方法针对信号的质量和系统传输的性能,主要包括波形观测、误码率测试、TDR和眼图测试,经实验证明这些方法对于千兆位背板总线系统的测试是行之有效的。通过测试得出结论:所设计出的千兆位背板总线系统性能优良,能够达到预定的性能指标。

参考文献

1 John Novellino.High-Speed Circuits Require Special Test Techniques. Electronic Design、 1995;43(15):71~80

2 Craig Prunty、Tom Palkert.Serial Backplanes Transport Designers To The Analog Zone.Electronic Design、1999; 47(19): 79~86

3 Howard W. Johnson、 Martin Graham、High-Speed Digital Design:A Handbook of Black Magic、Prentice Hall PTR 1993

4 Time Domain Reflectometry Theory.Hewlett Packard Company. Application Note 1304-2、1998

5 Kenneth M. True.Long Transmission Lines and Data Signal Quality. National Semiconductor Corporation Appli-cation Note 808、1992