摘要:分析了现有的视频采集方案的研究现状,对如何采用CCD摄像头采集多通道、高分辨率、高质量的图像以及基于FPGA" title="FPGA">FPGA的嵌入式图像采集" title="图像采集">图像采集系统的实现方法做了研究。与传统图像采集系统相比,该系统主要利用四片视频解码芯片SAA7113H" title="SAA7113H">SAA7113H和两片FPGA完成对四路图像的同时采集、存储和显示,能根据FPGA里UART模块接收到的指令切换一路图像在LCD或是VGA上全屏显示。实现了对两个FPGA的级联配置,针对视频解码芯片ADV7181B,实现了I2C总线配置、ITU656解码以及数据格式的转换。并根据多次实验,时最终显示图像的抖动现象作了分析和提出解决方法。结果证明,该系统具有低成本、高可靠、灵活性好等特点。

关键词:SAA7113H;FPGA;ITU565" title="ITU565">ITU565;图像采集

工业现场因为环境复杂,实时性要求高,常常需要对一处或多处重要位置同时进行监控,且能够在需要时切换其中一幅画面全屏显示。这就要求设计一种实时视频监控系统,既能够满足工业现场应用的特殊环境,具有体积小、功耗低、可定制的特点,又能够对多点进行同时采集和同屏显示以及对其中的一路进行切换。

国内现有的视频监控方案一般是采用CCD摄像头+视频解码芯片(如SAA7113H/ADV7181B)+FPGA/CPLD+DSP的模式实现,其中视频解码芯片用来对CCD摄像头采集的模拟信号进行AD转换,FPGA/CPLD对数据采集进行控制,DSP最终对数据进行处理。这种方法开发周期长,成本高,且可更改性差。

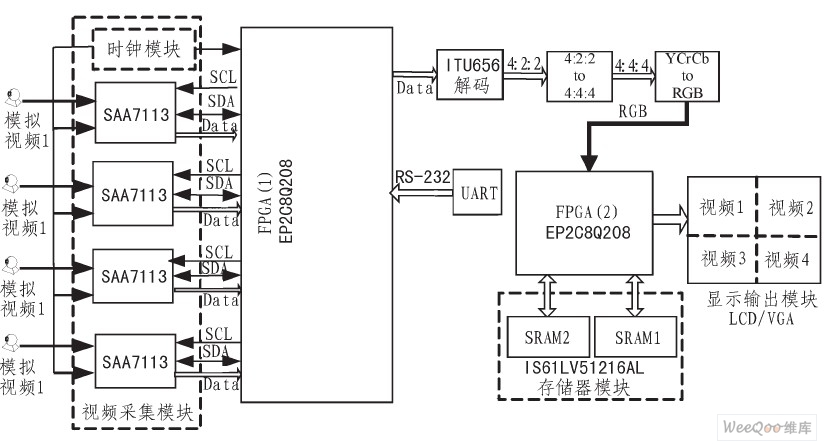

本文介绍的系统主要由两片Altera公司的CycloneⅡ系列的EP2C8Q20818" title="EP2C8Q20818">EP2C8Q20818和飞利浦公司的视频解码芯片SAA7113H以及外存储器件SRAM等组成。两片FPGA分别完成前端图像的采集和后端数据的处理,视频解码芯片完成模拟信号向数据信号的转换,存储器件在FPGA的控制下起到数据缓存作用。

1 系统描述

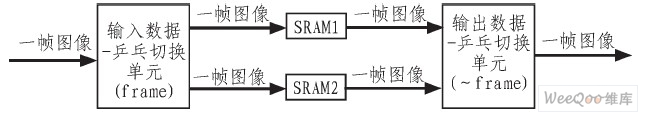

系统主要分为采集模块、解码模块、数据格式转换模块、存储模块、UART模块和LCD/VGA显示模块,如下图1所示。四片视频解码芯片在FPGA1的控制下通过I2C总线完成配置和初始化过程,输出8位与CCIR656兼容的YCrCb 4:2:2格式的视频数据,同时还包括行同步HS、场同步VS和奇偶场RTS0等信号。由于显示终端支持的是标准的RGB格式的数据,所以要对视频解码芯片输出的YCrCb 4:2:2格式数据进行转换。经转换所得的RGB数据在FPGA2的控制下,配合相应的时序信号,截取要显示的有效的640x480个像素,乒乓存入两个SRAM中,并最终在:LCD /VGA显示模块的控制下将数据显示在屏幕上。UART通讯模块集成在FPGA里,通过PC机的串口发送相应的控制命令,FPGA接收后切换相应通道的画面。

2 系统软件结构

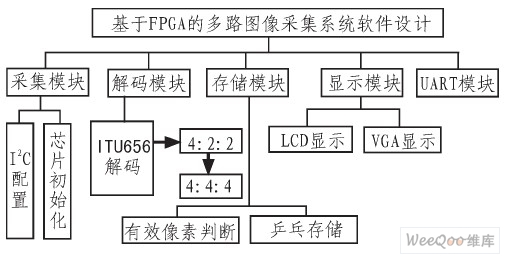

系统软件主要由采集模块、解码模块、存储模块、显示模块和UART模块组成,软件结构如图2所示。

3 ITU656解码

ITU656解码模块根据ITU656标准将4:2:2的数据流解码成ITU656标准视频流。ITU656并行接口除了传输4:2:2的YCbCr视频流外,还有行、场同步所用的控制信号。PAL制式的图像一帧有625行,每秒扫描25帧;每行数据由1128字节的数据块组成。其中,PAL制式23~311行是偶数场视频数据,312~552行是奇数场视频数据,其余为垂直控制信号。

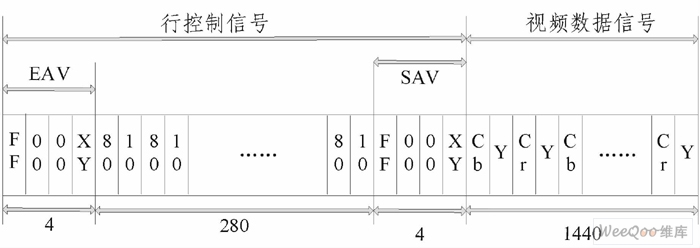

图3为ITU656每行的数据结构。每行数据包含水平控制信号和YCbCr视频数据信号。视频数据字是以27兆字/秒的速率传送的,其顺序是:Cb,Y,Cr,Y,Cb,Y,Cr,…其中,Cb,Y.Cr这3个字指的是同址的亮度和色差信号取样,后面的Y字对应于下一个亮度取样。每行开始的288字节为行控制信号,开始的4字节为EAV信号(有效视频结束),紧接着280个固定填充数据,最后是4字节的SAV信号(有效视频起始)。

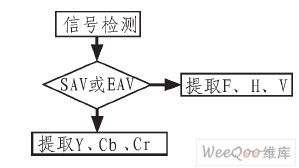

SAV和EAV信号有3字节的前导:FF、FF、00;最后1字节XY表示该行位于整个数据帧的位置及如何区分SAV、EAV。在每个时钟的上升沿读取从解码芯片传来的8位数据。当检测到一行数据的开始标志FF0000XY时,检测到SAV信号或EAV信号,提取H、F、V信号。然后发出开始命令,同时开启行列计数器,开始对接下来的图像数据进行解码,根据每个8位数据自身带的信息,判断该数据为Y,Cr还是Cb,从而得到Y,Cr,Cb各分量的值。解码流程如图4所示。

4 帧存储控制器与LCD/VGA显示控制器的设计

4.1 数据格式的转换

根据前面第2节的介绍,从ITU656解码模块出来的数据为8位4:2:2的YUV空间图像数据,而LCD/VGA显示器只能接收RGB数据。因为Y-CrCb4:2:2格式不能直接转换为RGB,所以需要先转换为YCrCb4:4:4格式。

我们知道解码芯片得到的视频数据是顺序为Cb,Y,Cr,Y,Cb,Y,Cr,……的序列,存储的时候将一个Y与一个C(Cb或Cr)结合起来组成一个16位的数据。而当数据被读出来时就要将这些视频数据转换为每个像素占24位(Y、Cb、Cr各占8位)的4:4:4的数据流。4:2:2到4:4:4的转换采用最简单的插值算法,在采样的时候,每隔一个像素才采一次色度值(Cb和Cr)。在转化时,直接将前一个有色度信息的像素点

的Cr以及Cb的值直接赋给后一个像素的Cr和Cb,这样就能得到4:4:4的像素数据,每个像素占用24位位宽。

4.2 帧存储控制器

作为系统的重要组成部分,帧存储控制器主要用来进行有效数据的缓存。视频数据在FPGA1的控制下乒乓写入两片SRAM。乒乓技术应用的关键在于乒乓切换信号frame的产生,本系统中根据视频解码芯片的奇偶场信号RTS0来产生帧切换frame信号,也就是一个RTS0周期切换一次。一个RTS0周期由一个奇场和一个偶场组成,是一副完整的画面。当frame为1是,FPGA通过计数器的计数截取最终显示所需要的有效的像素点信息按照SRAM的控制时序写入SRAM1,同样当frame为0时,将对应的像素信息写入SRAM2,如图5所示。

系统加电的同时,4片视频解码芯片同时工作,为了保证数据采集的准确性和显示的同步性,系统内生成一个八倍于像素时钟的写时钟信号write_clk,这样,在一个像素时钟周期,写时钟信号已经过了八个周期,而每两个周期分别完成一路图像数据的写过程。

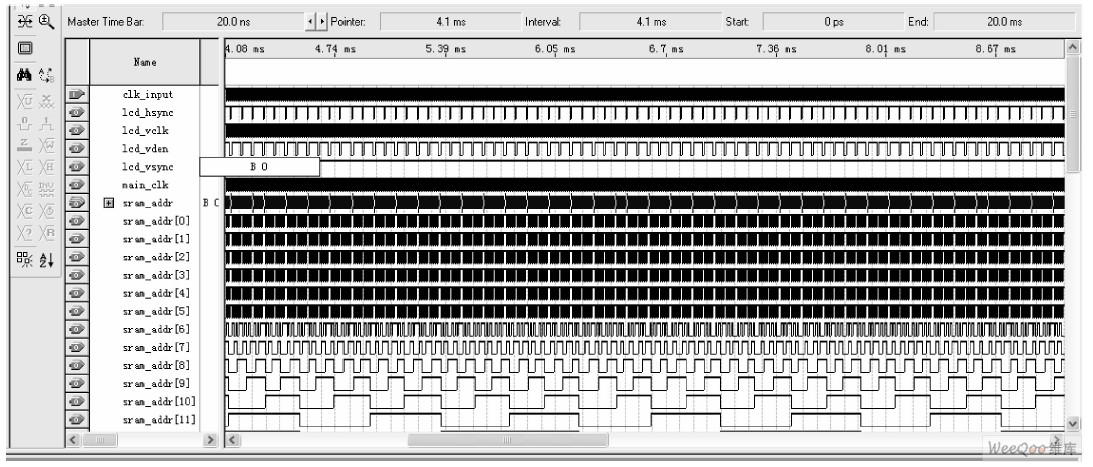

由于SRAM是一维存储空间,一个地址对应一个数据。所以在写入数据时将SRAM的地址空间划分为4段,每一段用来存储一路图像数据。

用程序实现比较简单,设置一个地址寄存器sram_addr_reg,将它赋给SRAM的地址控制信号sram_addr。然后在对每一路图像写入时,将对应的SRAM的起始地址加上一个固定的基数。如:

这样就保证了SRAM中对应地址的数据和屏幕上显示位置的一一对应关系,在读程序中,只需要按照顺序读SRAM即可,如图6所示。

4.3 LCD/VGA显示控制器

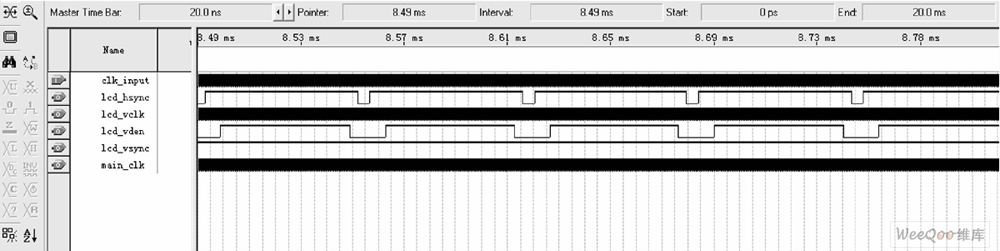

本模块主要是用FPGA来产生LCD/VGA显示时所需要的时钟信号CLK(像素时钟信号)、VSYNC(帧同步信号)、HSYNC(行同步信号)和使能信号(VDEN),并在相应控制时序的作用下,依次将显示缓存即SRAM中的数据依次读出,输出到LCD上的过程。

LCD显示所需的主要时序信号的关系如图7所示。

在系统中,LCD屏幕分辨率为640x480,像素时钟CLK为25MHz,由于FPGA的主时钟输入选用了20 MHz的有源时钟,那么就要求利用Cyclone芯片的内部逻辑资源来实现时钟倍频,以产生所需要的CLK(25 MHz)、用Verilog语言编写参数化的时序生成模块,产生HSYNC(32 kHz)及VHY-NC(60 Hz)时钟信号,如图8所示。

VGA显示原理与LCD相似,除了在硬件上正确连接ADV7125芯片电路外根据需要的分辨率来生成相应时钟信号即可。

5 图像抖动的分析与解决

在系统完成后软硬件联调时,出现画面抖动现象,其中以RTSO为基准而产生乒乓切换的那一路图像稳定,其他三路都出现不同程度的抖动现象。对此我们做了深入的分析和实验,分析整个系统的结构可知,系统在多个时钟控制下共同工作,也就是所说的典型的异步系统。我们知道,数据在异步系统传输时对时钟要求非常严格,稍微的一点时钟偏差都会带来对有效像素截取的偏差,最终影响图像的显示质量。

解决的办法有两个,一是加入缓冲机制,利用FIFO对数据存储的特性来实现数据在异步时钟之间的无缝传输;二是同步时钟,利用状态机等方法使得异步系统的时钟能够尽可能同步。采用第二种方法对系统进行改进,首先系统中所有的分频、倍频尽量使用Quartus 6.0自带的PLL产生,并且使用专用时钟引脚进行时钟输出;其次把写时钟write_clk降为54M,也就是每隔一个像素采集一次。最终,四路图像都能稳定显示。

6 结束语

本文实现了一种结合Altera公司生产的CycloneII系列FPGA与视频解码芯片ADV7181B的嵌入式图像采集系统。系统具有低功耗、低成本、高可靠和灵活性好等特点。基于FPGA的多路图像采集系统采用两片FPGA作为主控芯片,完成四路视频画面的同时显示和切换,实现两个FPGA的级联配置,采用Verilog语言编写的控制逻辑解决了画面抖动问题。系统软件集成度高,硬件结构清晰简单,即可满足一般监控场合对多处位置进行实时监控的需求,又能为功能更复杂的图像处理、压缩、传输系统提供前端图像数据采集。