继电保护或者测控装置都需要同步采集多路的电压或者电流信号,现在一般的实现方式都是用多路逐次逼近型ADC(譬如AD7656或者ADS8-556)实现多路同步数据的采集,这种方案采样速度高、控制简单,但是每一通道都需要基于运算放大器的抗混叠滤波器,所以实现起来成本高、占用PCB面积大。本文提出一种使用CS5451A模数转换芯片实现多路同步数据采集的实现方案,这种实现方式电路简单、成本低。在本方案中,处理器选用的是飞思卡尔MPC8313处理器,主频333 MHz。CS5451A如果用CPU直接控制,由于CS5451A芯片输出数据速率低,处理器与ADC速度严重失配会大大占用CPU的开销,本文提出一种利用XILINX可编程逻辑芯片FPGA实现异步FIFO和串并转换模块来实现采样数据的接收的方法,串并转换模块只需要接收一帧数据,存到异步FIFO后,向CPU发出一个中断信号,在中断服务子程序中CPU读走FIFO中的数据,这样可以大幅度提高CPU的利用率,系统结构简单,易于实现。

1 CS5451A概述以及电路的设计

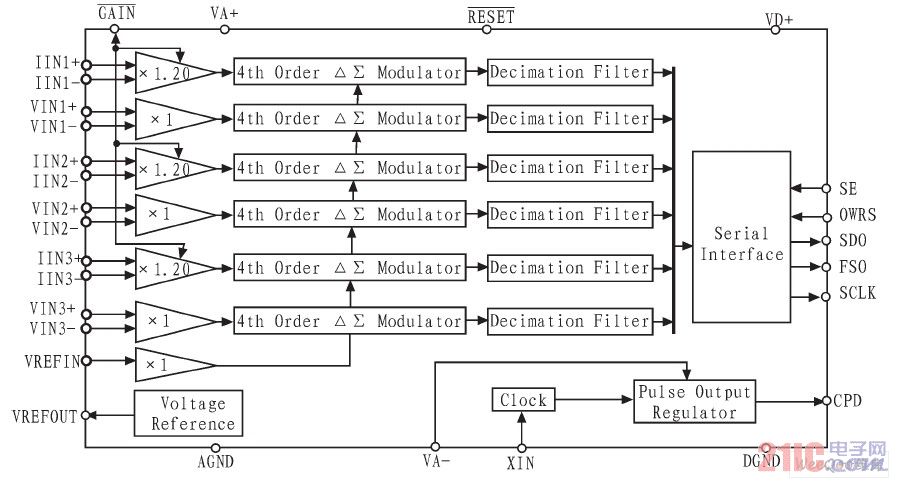

CS5451A是Cirrus Logie公司设计的一款高度集成的模数转换芯片。在一个硅片上集成了6个△-∑A/D转换器,6个数字滤波器和一个与微控制器或DSP相联接的串行接口。CS5451A包括3个电压测量通道、3个电流测量通道,它们的主要区别是3个电流测量通道的运算放大器的增益是可以更改的,可以设置成1倍或者20倍,而电压通道的增益固定为1倍。由于△-∑A/D转换器采用过采样技术以及数字滤波器,所以简化了ADC前级的抗混叠滤波器的设计。在本设计中抗混叠滤波器只设计了1阶低通滤波器。CS5451A结构框图如图1所示。

图1 CS5451A结构框图

在本设计中CS5451A的配置如下:

1)ADC电流通道增益设置为1倍增益,这样,6个通道增益都为1,电流通道和电压配置一样,每一通道不再有区别,容易做成通用的模拟输入设计。

2)最大输入范围为+20 V,互感器输出的电压信号通过电阻分压网络产生一个最大为±800 mV的电压信号,通过一介低通滤波器进入ADC芯片,CS5451A电路设计如图2所示。

图2 CS5451A电路设计

3)使用内部1.2 V参考电源。

4)时钟输入为4.096 MHz。

5)数据输出速率4.0 k还是2.0 k由CPU控制。

2 异步FIFO的设计

本设计中所用的FPGA芯片是XILINX公司的XC3S100E,XC3S100E是XILINX SPARTAN3E系列一款最低容量的FPGA芯片,此系列FPGA利用90 nm工艺实现低成本高容量的需求,XC3S100E具有以下资源:

1)有2160个逻辑单元;

2)具有RAM资源87 kB(其中BLOCK RAM 72 kB,分布式RAM 15 kB);

3)具有两个DCM;

4)具有4个乘法器;

5)可以实现FIFO等多个IP核。

在XILINX ISE10.1集成开发工具下,很容易利用XININX免费IP核实现一个异步FIFO。异步FIFO是在两个相互独立的时钟域下,数据在一个时钟域写入FIFO,而在另外一个时钟域下又从该FIFO中将数据读出。CS5451A控制系统框图如图3所示,异步FIFO和串并转换模块作为CPU和CS5451A之间的桥梁,由串并转换模块将ADC输出的串行数据转换成19位的并行数据(其中16位为数据,3位为采样通道号0~5)写入异步FIFO,这样FIFO就成为CPU前端的一个缓冲器。每接收完成1帧数据便向CPU发出一个中断信号,通知CPU读取FIFO中的数据。

图3 CS5451A控制系统框图

异步FIFO IP核的参数指标直接影响FIFO的读出速度,首先,FIFO的读出速度快能够减少CPU的开销,这样CPU可以有更多的时间干实时性更高的任务。其次,FIFO的存储深度要适宜,深度过大造成资源的浪费,深度过小会造成控制复杂,这样将占用更多的资源。本设计中的异步FIFO是利用ISE10.1中的参数化的IP核在XC3S100E芯片的实现。由于1个CS5451A芯片共有6通道ADC,ADC的分辨率为16位,考虑到数据的可靠性,每一个ADC通道的数据包括通道号(占3位),考虑到有的时候可能CPU不能及时的读走数据,所以在参数化的FIFO设计中选择FIFO深度为64,宽度为19位。

3 基于FPGA串并转换模块的设计

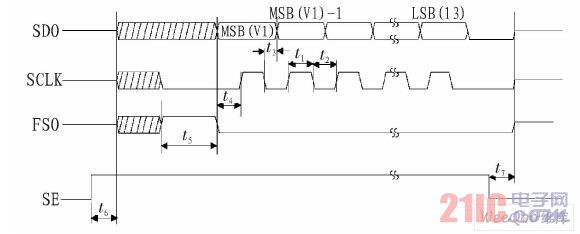

CS5451A通过一个Master模式的串行接口输出采样数据,输出数据通过SDO输出,SCLK为输出串行时钟,CS5451A串行输出时序图如图4所示,FSO是帧同步信号,表示一帧数据的开始,如果SE信号为高电平,这3个信号就有效,如果为低电平,3个信号都为高阻状态,在本设计中,CPU初始化后把SE设置成高电平。正常情况下,FSO信号为低电平,当有一帧数据要输出的时候,FSO信号变为高电平,高电平宽度为1个SCLK周期。当没有数据输出的时候,SCLK为低电平,FSO从高电平变为低电平后,SCLK时钟信号有效,数据在上升沿输出,SCLK共持续16x6个周期,数据串行输出时,MSB最先输出。

图4 CS5451A串行输出时序图

由于SCLK频率很低,在用CPU的SPI控制器接收数据的时候,CPU接收一位的时间为4tXINe=1μs,如图5所示,一帧数据为96位,接收一帧数据大约为96μs的时间,如果用CPU通过异步FIFO读取数据,因为现在的控制器总线速度很快,假设读一个字节数据需要100 ns,读走一帧数据大约需要100 ns×12=1.2μs(由于MPC8313总线宽度为16位,不能一次读取19位数据,所以在读取FIFO中数据的时候,把通道号锁存到一个暂存寄存器中,读取采样数据后再读取通道号,所以读取一帧数据需要12次)。只有原来的大约1/80的时间,提高了CPU的利用效率。

图5 CS5451A一帧数据输出图

图5 CS5451A一帧数据输出图

4 中断服务子程序的设计

CPU读采样数据是在中断服务子程序中设计的,在中断程序中读走采样值数据,并判断通道号是否对应。软件流程如图6所示。

图6 软件流程图

5 结论

本文利用CS5451A设计一个通用的多路数据采集系统,利用XILINX SPARTAN3E系列FPGA芯片实现异步FIFO和采样数据串并转换模块的设计,CPU不用直接用SPI控制器接收CS5451A芯片输出的串行格式的数据,只需要把ADC输出的串行数据通过串并转换模块存入FIFO缓冲区,并产生一个中断信号,在CPU的中断子程序中读出采样数据。该方案已经在低压继电保护装置中得到了应用,通过试验本系统的数据采集精度可以达到0.2级。调试中发现,在进行PCB设计时,要注意以下几点:

1)模拟部分电路(差分输入以及参考电源部分)和数字部分(XIN、FSO、SDO、SCLK信号)应完全分开在不同的区域里。

2)良好的去耦对抑制CS5451A产生的噪声很重要,去耦电容一般为0.1 μF,且放到电源输入引脚尽可能近的地方,以达到良好的去耦效果。

3)如果系统要求工作在-40~+85℃的温度范围内,要求采样精度达到0.2级,必须使用外部高精度的参考电源。