摘要:结合实际项目的开发经验,详细讲解了基于Xilinx Microblaze软核开发的整个流程,包括硬件平台搭建、软件平台开发、嵌入式操作系统的加载以及用非易失性存储设备对FPGA进行上电配置等内容。利用FPGA软核进行嵌入式系统开发,将得到越来越多的关注和应用。

关键词:嵌入式系统;软核;片上可编程系统;可编程逻辑门阵列

引言

近十年来,FPGA行业获得了突飞猛进的发展,其在系统开发工作中的地位已从简单的胶合逻辑上升到了数字系统的核心处理器件。可编程片上系统SOPC(Systern On Programmable Chip)将CPU核与外设核以及系统软件集成到单一芯片中,帮助用户快速“量身定制”所需要的产品,创造性地为用户提供了基于FPGA的嵌入式设计方案。

Xilinx公司作为FPGA嵌入式软核解决方案商,在其所有系列的FPGA中提供了Microblaze 32位软核处理器,并推出了用于嵌入式系统编程的EDK(Embedded Development Kit)集成开发解决方案。本文结合实际项目的开发经验,详细讲解了基于Microblaze软核开发的整个流程,包括硬件平台开发、软件平台开发、嵌入式操作系统的加载以及用非易失性存储设备对FPGA进行上电配置等内容。

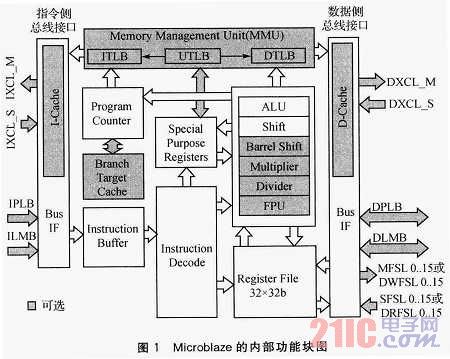

1 Microblaze的体系结构

Microblaze处理器采用RISC架构和哈佛结构,在时钟频率为150 MHz的情况下可以达到125 DMIPS的性能,该处理器(版本7.30)具有以下一些特征:

①32个32位通用寄存器和最多18个专用寄存器;

②32位指令系统,支持3个操作数和2种寻址方式;

③分离的32位指令和数据总线;

④通过本地存储器总线LMB直接访问片内的块存储器BRAM;

⑤具有高速的指令和数据缓存Cache,5级流水线结构;

⑥自带硬件调试模块MIDM;

⑦带有8个主/从快速单工链路接口。

图1给出了Microblaze的内部功能块图。

从图1可以看出,Microblaze软核与其他专用集成芯片的硬CPU核在结构上没有大的差别,但它却可以通过PLB总线(Processor Local Bus )与EDK软件包将自带的各种软外设进行按需连接,并且支持用户自定义IP通过PLB总线(Microblaze从7.30版本开始取消了原有的OPB总线)和FSL(Fast Simple Link)总线与Microblaze软核连接,从而最大限度地发挥FPGA设计的灵活性。

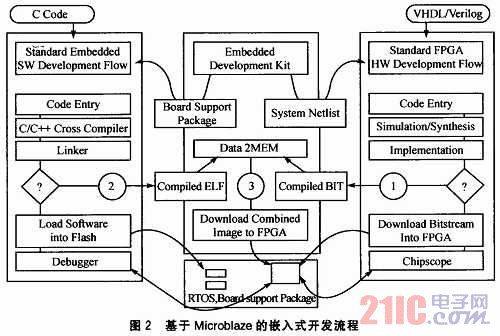

2 基于Microblaze的嵌入式开发流程

如图2所示,基于Microblaze的嵌入式开发流程主要包括3个步骤:首先要搭建起底层的物理平台,包括构建Microblaze处理器,将所需的外设通过片内总线挂到Microblaze处理器上,并根据需要开发用户自定义的IP核;第二步在构建起的硬件平台上编写软件应用程序,包括应用程序代码、库文件以及板级支持包BSP等;最后将硬件的比特流配置文件和软件的可执行重定位文件进行合并形成最终的文件,或者直接下载到FPGA内部运行,或者下载到FPGA片外的非易失性存储器Flash中,在系统配置完成后由Bootloader。程序将Flash中的应用程序拷贝到片外的DDRRAM中运行。

2.1 硬件平台的开发

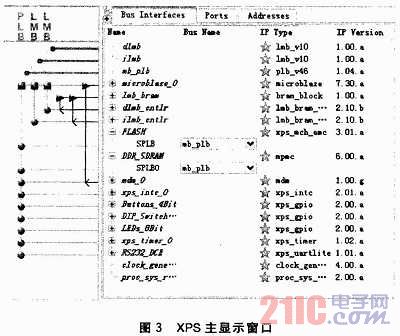

EDK的组件XPS(Xilinx Platform Studio)为Microblaze提供了一个集成开发环境,硬件平台的开发主要包括两方面内容:

①用基本系统向导BSB(Base System Builder)搭建Microblaze平台,包括FPGA器件型号的选择、Microblaze处理器属性的设置、所需外设的添加和属性设置、测试程序的生成等步骤。图3给出了BSB完成后的XPS显示窗口内容。从图3可以看到,系统添加了多种外设,如RS232串口、与外部Flash和。DDR RAM进行交互的控制逻辑、中断控制器和定时器等,这些外设通过指定的片内总线连接到Microblaze控制核上。除此之外,还可以在Ports页面对各个模块的信号进行相互连接,在Addresses页面对模块的地址进行分配等。这部分工作相当于将原本不可分割的ASIC专用集成芯片进行了拆卸,让用户深入到芯片内部,根据自身的需求去选取芯片需要具备的功能模块,并完成这些模块与控制核的连接和地址分配,形成用户最终定制的底层逻辑。这种拆卸和组合在一定程度上增加了系统开发的难度,但也换来了系统设计的灵活性、通用性和可扩展性。

②定制用户自己的IP核。由于嵌入式系统开发的特殊性,有时可能很难找到一款ASIC控制器,具备系统要求的所有外设接口。在这种情况下,要么用软件实现所缺的外设功能,从而牺牲了系统性能;要么单独购置一片该接口芯片,从而增大了电路板面积和成本。而基于FPGA软核的设计则不存在这种问题。在XPS中定制用户IP核与一般用VHDL编写逻辑电路不同的是,这种定制IP可以挂接在PLB总线上,从而实现与Microblaze的通信。XPS提供自定义IP核的生成向导,图4给出了用户自定义IP核的逻辑结构。从图可以看出,生成向导创建了两个模块,一个是与PLB总线进行交互的接口模块IPIF,另一个是用户逻辑模块User_Logic。IPIF完成PLB总线信号的捕捉和协议转换,这部分内容不需要用户参与,用户只需根据自定义逻辑的输入/输出信号在IPIF中给出相应的声明即可;User_Logic模块则是需要用户进行手动添加自定义逻辑代码的地方,在这里用户只需关注自己需要实现的功能,不用担心它们与Microblaze之间的通信链接。

2.2 软件平台的开发

EDK的另一个组件SDK是对于XPS集成开发环境的补充,提供了一个软件工程项目的开发环境,具有以下功能和特点:

◆基于Eclipse开源代码标准;

◆项目管理;

◆功能完善的C/C++代码编辑和编译环境;

◆程序创建配置和自动化的Makefile生成;

◆完美集成的对嵌入式对象的无缝调试环境。

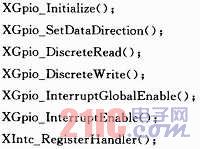

除了提供软件的开发环境外,Xilinx公司还提供了各种IP核的API控制函数,这些API被安放在..\EDK\SW\XilinxProcessorIPLib\drivers目录下,其中..\表示Xilinx软件的安装目录。通过阅读IP核的PDF说明文档和API函数的C代码,用户可以很容易地实现对IP核的控制。以通用输入/输出端口GPIO为例,在文件夹..\EDK\sw\XilinxProcessorIPLib\drivers\gpio_v2_13_a下存放着与GPIO软件编程有关的所有内容,其src子目录下包含各种API函数的C源码,doc目录下包含对各种API函数的使用说明,而examples目录下还有针对GPIO进行编程的实例源码。一般对GPIO的操作过程为:

即首先对GPIO口进行初始化,然后设置其方向为输入或是输出,接下来就可以对GPIO进行读写。如果该GPIO可以产生中断,则必须置位其中断使能位,然后将中断处理函数挂接到中断控制器或直接挂到Microblaze的中断位上。

2.3 Chipscope调试

Chipscope是Xilinx公司的片内调试工具,通过将逻辑分析器、总线分析器和虚拟I/O小型软核插入到用户的设计当中,可以查看和分析任何内部FPGA信号,包括嵌入式处理器总线。信号被实时采集,并从编程接口JTAG传输到主机,然后通过Chipscope Pro逻辑分析器进行分析。Chipscope的典型工作模式支持4种Chipscope Core,它们具有不同的功能和适应环境:

①Chipscope_icon,用于管理其他的Chipscope core,所有的Chipscope core都是通过这个核连接到FPGA的JTAG口;

②Chipscope_ila,用于监控FPGA内部的自定义信号,是使用范围最广的监控核;

③Chipscope_plb46_iba,用于监控PLB总线;

④Chipscope_vio,用于监控FPGA内部的实时自定义信号变化。

Chipscope使用的几个主要步骤包括:

①调用Chipscope Pro Core Generator,生成需要使用的Chipscope cote,并加入到工程中;

②调用Chipseope Pro Core Inserter,选择需要监控的信号,设置采样和匹配参数,并将配置后的Chipscopecore插入到设计中;

③调用Chipscope Pro Configuration,包括ChipscopePro On-Chip Debugging和Chipscope Pro On-Chip Verification,即通过Chips-cope的分析器工具Analyzer观察FPGA内部信号,并和设计者的需求进行比较,分析不一致的时序。

3 为系统添加嵌入式操作系统

如果系统所涉及的功能比较复杂,或者系统对实时性要求比较严格的话,在自己的设计中加载一个嵌入式操作系统是一个很好的选择。Xilinx FPGA目前支持绝大多数主流嵌入式操作系统,如VxWorks、Embedded Linux、μClinux、μC/OS-II和PetaLogix等,而μC/OS-II因其具有移植方便、执行效率高、占用空间小、实时性强和可靠性高等优点,成为Microblaze软核的首选嵌入式操作系统。μC/OS-II的大部分源代码是用ANSI C语言编写的,它的移植只需改写与处理器有关的3个文件即可。

如图5所示,修改与处理器相关的常数和宏定义头文件OS_CPU.H、任务切换过程中的堆栈处理汇编文件OS_CPU_A.ASM和钩函数定义文件OS_CPU_C.C。最简便的做法是在μC/OS-II官方网站www.micrium.com上下载an1013.zip压缩包,里面包含针对Microblaze修改好的3个移植文件、μC/OS-II软件代码和μC/OS-II应用指导文档,根据文档的描述将压缩包中的相关文件放到Xilinx的指定安装目录下,就可以在S-DK中直接选用μC/OS-II操作系统。此外,压缩包中还提供了一个示例程序,用于演示μC/OS-II操作系统是否在Microblaze系统上运行正常,极大减轻了用户在移植μC/OS-II过程中所面临的工作量。

4 FPGA的配置

基于SRAM结构的FPGA每次上电都需要外部的配置芯片对其进行加载,Xilinx的FPGA提供了多种配置方式,如简便的Platform Flash PROM主串配置、价格低廉的SPI配置、大容量的并行配置和JTAG配置等,用户可以根据自己的实际情况进行灵活选择。结合iMPACT图形化配置软件,向片外配置芯片烧写比特流的工作变得非常简单,极大缩短了系统的开发时间。除了常规的配置方式外,Xilinx FPGA还支持将多个配置文件放在一个配置芯片中实现系统的多配置启动,或者将用户数据存放在配置芯片中,在系统配置完成后根据需要随时从配置芯片中读出用户数据。在Xilinx的官方网站www.xinlinx.com上可以下载关于芯片配置的各种应用文档,使用户在嵌入式系统开发过程中最大限度地发挥FPGA的灵活性。

结语

基于FPGA软核的嵌入式系统开发分为硬件平台开发和软件平台开发两个部分,在硬件平台开发过程中可以根据需求选择外设,也可以定制自己的IP,实现更为灵活的接口和控制功能;在软件平台开发阶段则可以充分利用XPS提供的API制函数,方便快捷地编写控制程序。FP-GA进行嵌入式系统开发所具备的定制性正受到越来越多的青睐和关注,可以预见,未来使用FPGA进行嵌入式产品的开发必将成为潮流。