摘要:目前数字相机逐步取代模拟相机应用在光电测量设备中,因此图像处理器" title="图像处理器">图像处理器也逐渐转化为接收数字视频的接口,对数字图像处理器检测的信号发生器" title="信号发生器">信号发生器的研制也变得十分迫切。本文介绍了一种基于FPGA的两种数字视频格式输出的视频发生器,它可以产生LVDS制式的数字视频信号和CamerLink制式的数字视频信号,而且可以通过串口对产生的视频中的目标大小、运动速度、灰度及背景灰度进行实时更改。它满足了对数字视频输入的图像处理平台" title="图像处理平台">图像处理平台的检测,具有一定应用前景。

关键词:现场可编程门阵列;视频发生器;LVDS;图像处理平台

0 引言

在光电测量系统中,需要图像处理器进行图像采集、处理。而为了对图像处理器的图像采集能力及处理能力进行评估、检测,常常需要对图像处理器输入特定视频,进行各项功能测试。目前随着数字化相机的广泛应用,图像处理器多采用数字化接口。而且对图像处理器的检测要求信号发生器产生的视频内容越来越丰富,帧频越来越高,而目前检测图像处理器的信号发生器多是标准的模拟视频输出,如文献提出的模拟视频发生器,有的虽然能产生数字视频但内容是固定的,如果对内容进行更改则需要对数字视频信号发生器重新编程以达到要求,比较麻烦,不能满足日益复杂的要求。因此灵活改变视频内容的数字视频信号发生器的研制变得十分迫切。本文提出一种数字视频信号发生器的设计方法,此方法可以同时得到LVDS和CamerLink制式的视频,供数字化图像处理器检测使用。本文提出的设计方法除可以脱离计算机独立使用外,如果想实时更改信号发生器输出视频的各项参数,无需重新改写程序,只需把该信号发生器通过串口连接到计算机上,即可通过人机交互的方式对视频中的目标灰度、背景灰度,目标大小、目标运动速度进行更改。此外目标的背景还可以从板卡上的SDRAM中选取。与以往的视频信号发生器相比,本文提出的信号发生器除能产生多种数字化视频外,还能灵活更改所产生的视频各项参数,因此具有一定应用价值。

1 硬件组成

数字视频发生器主要卣FPGA模块、单片机模块、串行通信模块" title="通信模块">通信模块、TTL转L,VDS模块、FTL转CamerL,ink模块、SDRAM模块组成,整个系统框图如图1所示。

1.1 工作原理

数字式视频信号主要由行同步、帧同步、像素时钟、图像数据" title="图像数据">图像数据组成。其中行同步决定一行的起始位置,帧同步决定一帧图像的起始位置,像素时钟决定一行有多少列图像数据。根据数字图像的组成,可以看出如果想要生成一幅数字图像,必须包含上述要素。其行帧信号同图像的关系如图2所示,其中VSYN表示帧同步信号,HSYN表示行同步信号。

其中图像的采集是从行同步上升沿开始后,按像素时钟采集的。

本文根据数字视频产生所需的各要素进行信号发生器的设计。主要通过FPGA产生行同步信号、帧同步信号、像素时钟;通过单片机+串口通信模块实现目标参数的更改,并把更改后的参数传递给FPGA,供FPGA产生相应运动的视频信号;通过视频制式转换模块把FPGA生成的视频数据及视频控制信号转换成LVDS和CamerLink制式的数字视频信号。

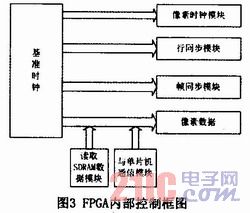

2 FPGA控制模块

FPGA具有高集成度、高可靠性以及开发工具智能化等特点,目前逐步成为复杂数字电路设计的理想首选。此外FPGA可以通过编程实现硬件的逻辑功能,大大减少了硬件设计的复杂程度。因此本文以FPGA为核心器件产生视频信号,这里选用ALTERA公司的SycloncII系列的EP2C8 F25618N,采用VHDL语言编程生成与数字视频有关的各个信号,与单片机通信接收视频修改参数的模块及得到SDRAM内部图像的模块。其结构框图如图3所示。

信号发生器上电后,FPGA通过与单片机通信的模块得到初始视频各项参数,根据参数进行目标大小、目标灰度、目标运动速度、背景灰度的设置,然后根据各项设置产生视频数据,FPGA帧同步模块、行同步模块、像素时钟模块分别产生帧同步、行同步、像素时钟,图像数据按以上控制信号从FPGA中发送出去。

在本文中FPGA各功能模块根据基准时钟生成帧同步、行同步、像素时钟。这里以50M时钟为基准时钟信号,根据图像处理平台对输入信号的要求,设计的帧同步高电平占33ms,低电平占1.2ms,行同步高电平占35 μm,低电平占8.4μm。这里把50M基准时钟输入像素时钟模块经过锁相后依然以50M的时钟频率输出,作为像素时钟。由于一行较多,可在程序中进行限位,控制每行像素数。像素的产生主要有两种方式,一种是通过与单片机通信得到目标像素灰度及背景像素灰度,根据这两种灰度产生像素数据。另一种方式是通过从连接在FPGA上的SDRAM内读出图像作为背景,从与单片机通信得到目标灰度,共同形成像素数据。

2.1 单片机控制模块及通信模块

在本设计中单片机作为通信管理芯片。它主要实现与计算机的通信,更改信号发生器所产生信号的各个参数,把各个参数经过整合送给FPGA,以便FPGA根据参数控制目标的运动速度、目标大小、目标灰度及背景灰度。为了保证信号发生器能够方便地和计算连接,实现人机交互,实时更改产生的视频信号,并且从通信稳定可靠出发,这里采用RS232通信接口。但是因为计算机每次发的数据较多,这里没有直接应用电平转换芯片把计算机和单片机的串口连在一起,而是通过一片16C650把电平转换芯片和单片机连在一起,这样的好处在于16C650内部具有32字节的FIFO,可起到数据缓存的作用,使单片机能够稳定可靠地接收数据。

2.2 视频制式转换模块

因为FPGA产生的视频信号为TTL电平,而目前数字视频信号以LVDS制式和CamerLink制式为主,因此需要进行电平转换。这里主要采用把FPGA产生的TTL电平的数字视频信号接入SN75LVDS387得到LVDS制式的视频信号,同时可把该TTL数字信号接入DS90CR285得到CamerLink制式信号。

3 软件设计

本文软件设计主要对单片机和FPGA进行编程。其中对单片机编程主要应用C语言进行编程,对FPGA主要应用VHDL语言编写。其中单片机程序框图如图4所示。FPGA程序流程框图如图5所示。

4 结论

本文介绍了一种基于FPGA的数字视频信号发生器,此发生器能够同时产生CamerLink和LVDS制式的视频信号,同时此视频信号发生器可通过人机对话的方式对所产生的视频信号中的目标、背景灰度、目标大小、运动速度等参数实时更改,从而达到检测图像处理平台目标分辨能力、目标捕获能力、目标捕获目标跟踪速度、目标跟踪精度等指标的目的。因此具有一定应用价值。