MF RC500-高集成ISO14443A 读卡器设计(第二部分并口数据)

RF社区

苏州中科集成

摘要: 4.并口4.1所支持的微处理器接口概述:MFRC500支持与不同的微处理器直接接口可与个人电脑的增...

Abstract:

Key words :

4 .并口

4.1 所支持的微处理器接口概述:

MF RC500 支持与不同的微处理器直接接口可与个人电脑的增强型并口EPP 直接相连。

下表所示为MF RC500 所支持的并口信号:

表1:并口描述

4.2 微处理器接口类型自动检测

在每次上电或硬复位后 MF RC500 也复位其并行微处理器接口模式并检测当前微处理器接口的类型MF RC500 在复位阶段后根据控制脚的逻辑电平识别微处理器接口这是由固定管脚连接的组合见表2和一个专门的初始化程序实现的见表3 。

表3:并口连接配置

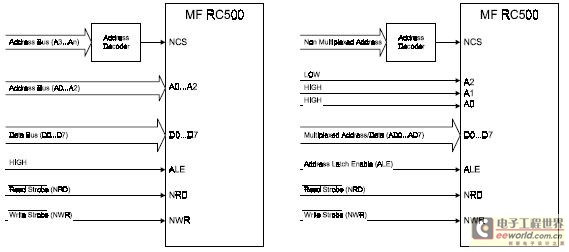

4.3 独立的读/写选通信号如下图所示:

图: 独立的读/写选通连接到微处理器

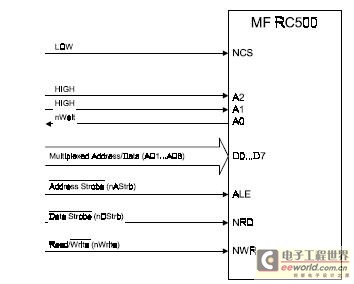

带握手机制的共用读/写选通信号EPP

尽管在EPP 的标准中无片选信号的定义,MF RC500 的N_CS 允许禁止nDStrb 信号如果不用应。

将其接到DVSS

在每次上电或硬复位后nWait 信号由A0 脚发出为高阻态,nWait 将在复位后nAStrb 上的第一个下降沿时定义。

MF RC500 不支持读地址周期。

此内容为AET网站原创,未经授权禁止转载。