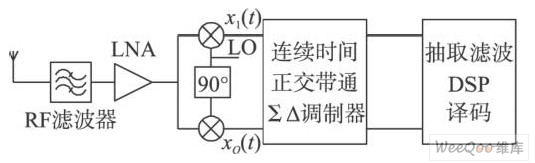

在低中频射频接收机中,如图1所示,射频信号经过下混频,产生I、Q两路正交低中频信号,之后直接通过带通ΣΔADC进行模数转换。由于中频不在直流处,可以避免直流失调和闪烁噪声。正交带通ΣΔADC比传统的带通ΣΔADC更适用于低中频架构,这是因为前者的噪声整形零点全部分布在单一频域,后者的噪声整形零点则对称的分布在正负频域,负频域的噪声整形零点是浪费,正交带通ΣΔADC在噪声整形性能上有优势。正交带通ΣΔADC由模拟和数字两部分组成,模拟部分是正交带通ΣΔ调制器,数字部分是抽取滤波器,本文主要研究正交带通ΣΔ调制器。

图1 低中频接收机架构

连续时间ΣΔ调制器与离散时间ΣΔ调制器相比,它具有一些显着的优势,特别是无需独立的抗混叠滤波器,同时降低对运放单位增益带宽和摆率的要求,从而有利于降低了调制器的功耗。文献首次提出并验证了连续时间正交带通ΣΔ调制器架构,近几年文献也提出了一些成功的设计。其根本设计方法都是将两个低通滤波器的输入输出进行交叉耦合来构成一个具有带通滤波特性的复数滤波器。

众所周知,连续时间ΣΔ调制器有一些固有的非理想特性,时钟抖动就是最主要的非理想特性之一。本文主要研究如何减少时钟抖动影响,设计了一个对其不敏感的四阶连续时间正交带通ΣΔ调制器。

1 复数滤波器

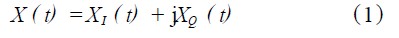

在低中频架构中,经过下混频产生的I、Q两路正交实信号可以表示成一个复数信号:

复数信号最重要的特性之一就是频谱关于直流不对称。处理复数信号就需要复数滤波器,如图2所示,它是由实数滤波器经过交叉耦合而形成,

图2 复数积分器

其传输函数为:

实数积分器具有低通特性,其传输函数的频谱关于直流对称,而复数积分器具有带通特性,其传输函数频谱的对称轴平移到了:

复数滤波器是构成正交带通ΣΔ调制器的基本模块,其传输函数的极点就是ΣΔ调制器的噪声整形零点。

2 正交带通调制器

目前连续时间正交带通ΣΔ调制器的设计方法主要有两种: (1)先设计一个优化好零点位置的连续时间低通ΣΔ调制器,然后用它构成I、Q两路,最后对两路调制器进行交叉耦合实现频谱搬移; (2)通过平移离散时间低通ΣΔ调制器的NTF,得到一个离散时间的复数NTF,然后对它进行DT2TO2CT变换,最终可以求得调制器的各支路系数。方法2设计过程繁琐,且整个调制器系数多,在电路实现时意味着更多的元件。

本文采用的方法与第一种类似,调制器的设计分为两步: 首先设计四阶连续前馈低通ΣΔ调制器,然后根据文献提供的四阶ΣΔ调制器的零点位置确定耦合电阻大小。

四阶前馈低通ΣΔ调制器整个环路滤波器是由有源RC积分器构成的,这是因为与开环结构的gm2C滤波器相比,反馈结构的有源RC积分器具有更好的线性度。之所以选择前馈结构,是因为前馈结构中只有误差信号通过整个环路滤波器,这降低了对各级积分器动态范围的要求,从而减少了功耗。然而前馈结构需要额外的求和模块,为了使求和网络在大的输入信号下仍具有良好线性,选择采用电阻比例积分器。

量化器选择本质上线性的1 bit比较器,反馈路径上采用对时钟抖动不敏感的开关电容DAC。

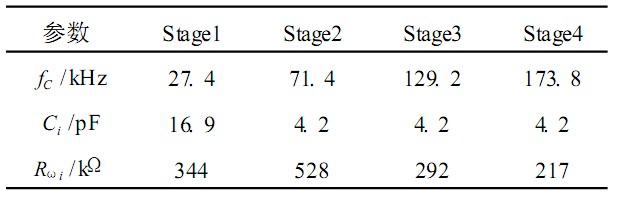

调制器零点频率即为复数积分器的中心频率fC ,根据式( 3)可以求出各级耦合电阻Rωi的值。表1反映了本文设计的正交带通ΣΔ调制器零点的分布情况, Ci 为各级积分器的积分电容。

表1 调制器零点配置

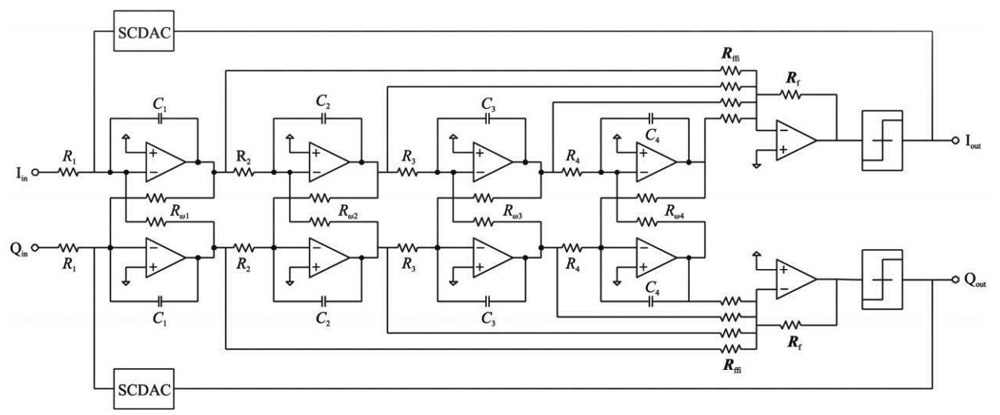

如图3所示,这是本文设计的四阶连续时间正交带通ΣΔ调制器,它由I、Q两路四阶前馈低通ΣΔ调制器经过电阻交叉耦合组成。

图3 四阶连续时间正交带通ΣΔ调制器

3 时钟抖动

时钟抖动是限制连续时间ΣΔ调制器性能的主要非理想因素之一。由于时序的不确定性,在量化器对求和电路输出进行采样和DAC产生反馈波形时都会引入误差。在采样过程中引入的误差和量化噪声一同被调制器的NTF整形。然而,DAC引入的误差直接反馈到输入,会限制整个调制器的性能。

采用开关电容反馈DAC能降低连续时间调制器的性能对时钟抖动的敏感度。

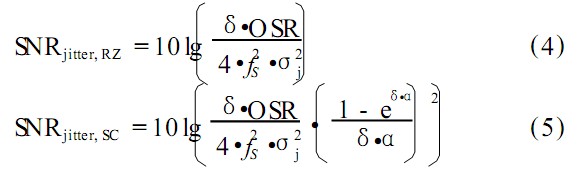

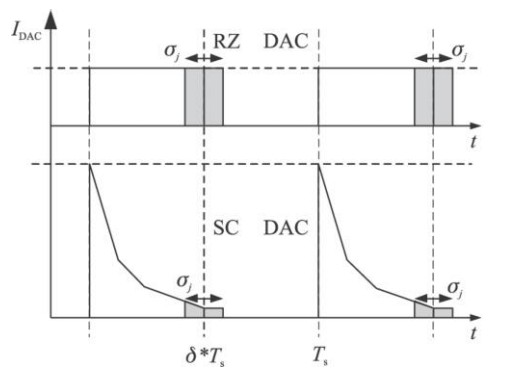

图4反映了时钟抖动对归零矩形波和指数波形的影响,在这两种反馈波形下,时钟抖动对SNR 的限制分别为:

其中,δ是DAC的占空比,σj 时钟抖动的均分根,α =TS / (RdacCdac )是采样周期与时间常数的比值,这里认为时钟抖动是方差为σj2 的随机白噪声。由(5)式,可以看出时钟抖动引入的误差与开关电容DAC的时间常数有关。比较以上两式,可以看出与归零矩形波相比,指数波形更能抑制时钟抖动效应对SNR的影响。

图4 时钟抖动的对反馈波形影响

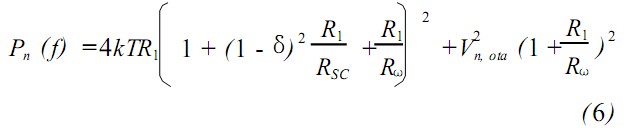

开关电容DAC的热噪声是调制器输入参考热噪声的重要组成部分,参考文献的结论,可以推出第一级复数积分器输入端的参考热噪声近似为:

其中RSC = TS /Cdac是开关电容电路的等效电阻。

4 电路模块

ΣΔ调制器中最重要的模块是构成有源RC积分器和比例加法器的运放, 1 bit量化器和开关电容反馈DAC。

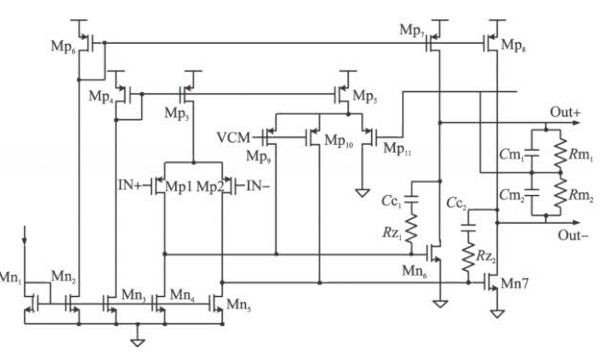

4. 1 运放

ΣΔ调制器中的运放都是两级米勒结构,如图5所示。运放第1 级满足增益和噪声要求, 采用PMOS作为输入管可以降低闪烁噪声;第2级满足摆幅要求。运放的输出被共模反馈电路检测,与参考电压比较,误差信号被反馈到运放内部,迫使运放的输出共模等于参考电平。与米勒电容串联的电阻用来抵消次极点。

ΣΔ调制器第1级运放直流增益为88 dB,单位增益带宽为250 MHz,调制器中其余运放的增益为85 dB,单位增益带宽为45MHz。

图5 两级Miller运放

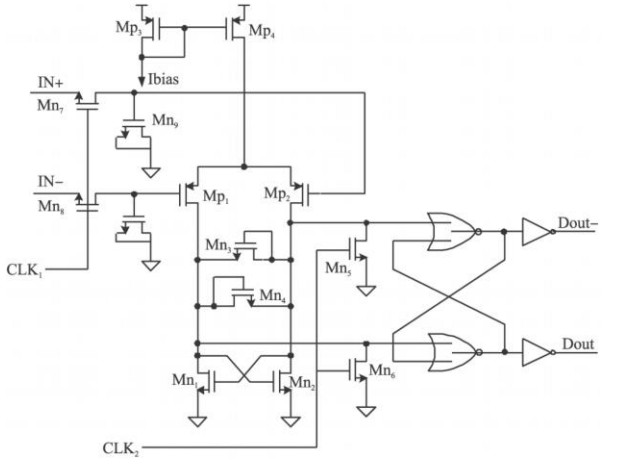

4. 2 量化器

量化器由比较器和SR锁存器组成,如图6 所示。比较器由Mp1 和Mp2 构成差分输入,Mn1 和Mn2 构成的负阻,正的增益起到了再生作用。为了获得更高的工作速度,在两个输出端之间还有两个二极管连接Mn3 和Mn2 ,对差分输出端的电压进行钳位。当CLK1 和CLK2 为1时,所有开关管闭合,信号被采样到MOS电容上,比较器的输出为0,交叉耦合的或非门保持原来逻辑电平不变; 当CLK1和CLK2 为0时,所有开关管截止,比较器的一端产生逻辑电平1,另一段产生逻辑电平0, SR锁存器更新逻辑值。

图6 1 bit量化器

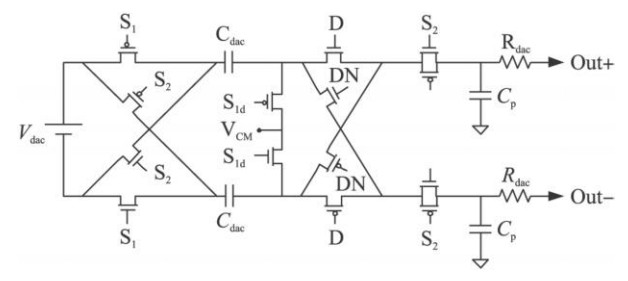

4. 3 开关电容DAC

开关电容DAC由MOS开关,电容和电阻组成,如图7所示。在第一个时钟相,开关S1 闭合, S2 断开,上下电容两端的电压为±0. 5Vref。在第二个时钟相,开关S2 闭合, S1 断开,电容放电,开关D 和DN决定放电通路。为了减小电荷注入效应,开关S1 比S1d提前闭合。输出端接第一级运放的输入,所以在第一个时钟相开关电容DAC的输出端电压等于运放的输入共模电压VCM 。

图7 开关电容DAC

5 仿真结果

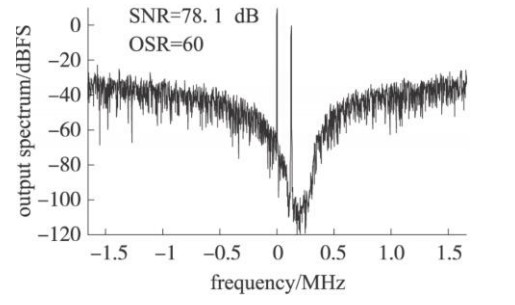

四阶连续时间正交带通ΣΔ调制器采用smic0. 13 mixed2signal CMOS工艺实现。采样频率为12MHz,过采样率为60,有效带宽为200 kHz,中心频率为200 kHz。用Spectre进行仿真验证,当I、Q两路的输入分别为125 kHz的正弦和余弦信号时,调制器的输出功率谱密度如图8所示,整个频谱近似关于f = 200 kHz对称,其SNDR为78 dB。

图8 输出频谱密度

6 结论

本文提出了一个基于复数滤波器的四阶连续时间带通ΣΔ调制器电路,非常适用于低中频架构。

调制器采用开关电容DAC,有效减少了时钟抖动效应的影响。