1引言

激光告警机" title="激光告警机">激光告警机是被动光电侦查设备,其功能是探测目标激光信号的性质,如波长、方位等,本系统能够完成探测并提取激光波长信息的功能。在激光波长测量系统中,激光信号从CCD相机输出到信号处理器的时间和处理器的处理时间是能否做到实时监测激光波长的两大关键,即使采用高速单片机也限于它的串行处理模式和较长的取指时间,无法满足实时测量的目的,因此为实现在几毫秒内就对目标激光信号的波长做出反应只能寄希望于高性能的DSP器件或FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA" title="FPGA">FPGA器件了。告警系统中,相机的接口为器件的选择则也提出要求:采集器件要支持LVDS 电平,否则要加入电平转换芯片,这势必会带来数据传输的延时;此外应用FFT进行数据处理时,由于FFT在算法上具有可重复性和可并行处理的特点,为实现实时性处理,要求选择具有并行处理功能的处理器。在设计中选用Xilinx公司的Sp3系列FPGA作为控制、处理器,将FPGA用在本系统中的好处有: (1)高密度FPGA可在一块片子上实现多个子模块,有效减小激光告警接收机的体积;(2)FPGA具有成熟的时钟管理体系,和精确的时钟控制体系,能够实现采集与处理的无缝连接,从而提高系统可靠性;(3)FPGA支持多种信号标准,尤其在告警系统中FPGA可将接口设置为LVDS型,使得FPGA与相机的通信更加直接,避免了以往采用电平转换芯片的相关工作;(4)FPGA具有并行处理功能,能够实现流水作业,可减少信号处理时进行FFT运算的时间。

2原理概述

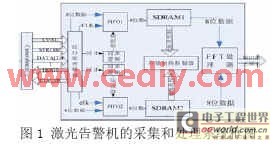

相机将探测到的激光信号通过Cameralink接口方式传递给FPGA,FPGA控制时序产生来完成以下工作:向CCD输入时钟信号;通过触发端设置 CCD积分时间;倍频相机的STROBE信号实现接收数据的串并转换;将并行数据在读使能的控制下从FIFO中转入块RAM。为提高激光告警机的响应时间该系统充分利用FPGA可流水作业这一功能,在数据接收端提供两个1024个单元的数据存储器交替工作,通过在软件上设立标志位来实现对存储区间进行切换。在数据存储和数据处理时,当FPGA用1 区进行采集数据的第i帧时,同时2 区进行第i-1帧数据的处理,当两者同时结束后,接着又用2 区进行第i+1帧数据的采集, 同时1 区进行第i 帧数据的处理, 这样交替工作,形成流水线作业。由于相机采集速率和块RAM写入时间的不同,在FPGA内部采用IP" title="IP">IP 核生成两个FIFO为两路数据的接收实现缓冲来取得同步。块RAM的写入、读出时序和地址发生器由VHDL语言编写完成。数据的处理通过在时钟的同步下逐一读取RAM中的数据,采用十级流水基-2算法实现1024点的快速傅里叶变换,得出输入激光信号的频谱特性。激光告警机的采集和处理系统框图如图1所示。

3系统设计

整个系统由两部分构成:数据采集模块,数据处理模块。

3.1 CCD相机数据采集模块

在设计中采用ATMEl公司的AViiVA M2 CL相机,该相机采用Cameralink接口,Cameralink技术的核心是美国NS(National Semiconductor)提出的一种高速数据传输方法—Channel Link技术,该技术主要用于数字图像数据的高速传输,采用LVDS信号模式,LVDS低电压摆幅差分模式具有高速传输数据时交叉干扰小、EMI 干扰小等优点,最高传输率可达2.38Gb/s。该相机的接口定义为:四对LVDS线,用来做FPGA对相机的控制;两对LVDS线,用于相机和FPGA 之间的通信,速度可达9600波特率;四对LVDS线,用于输出数据和数据的位同步、帧同步信号。选用XC3S400型的FPGA,它具有丰富的接口标准尤其是支持LVDS 信号标准,可与Cameralink接口的相机直接连接。相机工作方式的设置由FPGA基于RS-232协议串行通信来实现,采用全双工,没有握手信号的异步串行方式,波特率固定在9600Hz,每帧数据由一个起始位,8个数据位,一个停止位组成。相机的积分时间和输出增益都是可以根据需要设置为不同的值。对于相机工作的触发方式由FPGA外部触发,做到FPGA与相机共用同一个全局时钟。

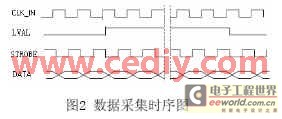

在数据的采集过程中,数据传送的同步信号由 STROBE引脚产生,当数据在一个数据区存满时,通过LVAL引脚通知FPGA 转到另一数据存储区。图2 给出了数据采集的时序图。其中CLK_IN是由FPGA的内核数字时钟管理模块DCM 来实现倍频得到。在时钟控制和管理方面DCM比DLL功能更强大,使用更灵活。DCM的主要功能包括消除时钟时延、频率综合和时钟相位的调整。在本设计中对输入时钟STROBE作8倍频处理,以实现数据一转八串并转换的锁存输出。

高速采集程序的设计主要有接口匹配、采集状态机和数据存储三部分。在接口匹配中由于LVDS 的输入与输出都是内匹配的,所以LVDS 间可直接连接。在FPGA 内,需对差分输入时钟缓冲器(IBUFDS)、差分输入的全局时钟缓冲器(IBUFGDS)和差分输出时钟缓冲器(OBUFDS) 例化。

FPGA 的部分代码如下:

component IBUFDS - - 差分输入时钟缓冲器( IBUFDS)

port (O : out STD_ULOGIC;

I : in STD_ULOGIC;

IB : in STD_ULOGIC) ;

end component ;

IBUFDS_INSTANCE_NAME: IBUFDS

port map (O=>user_O,I=> user_I,IB =>user_IB) ;

3.2数据处理模块

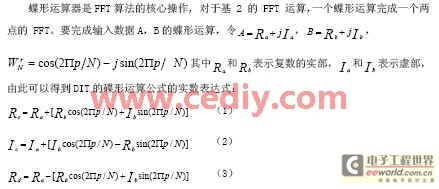

Spartan3系列FPGA有丰富的乘法器资源,在不使用任何优化算法的情况下每一个蝶形运算需要4个实数乘法器,因此在FPGA中每个蝶形运算可以用 4个乘法器在一个时钟周期内完成。丰富的RAM资源便于实现数据的流水操作,即对于输入、输出数据以及中间变量可以开辟不同的存储区,例如当计算第i组数据时,第i-1组计算结果正在输出,第i+1组数据正在输入。

由于在FFT运算中必然产生复数,因此为使计算方便,在设计之初就将FFT变换器的数据输入口分为实数和虚数。1024点复数FFT运算,按照基-2频率抽取运算分成10级,每级包括1个双端RAM,1个地址发生器,一个ROM用于存储旋转因子表,1个蝶形运算单元,2个选择缓冲单元。为了简化地址单元电路,将复数数据的实部虚部组合成一个数据存储在RAM中。由于使用双口RAM ,当一个存储单元中的数据读出做运算时,该存储单元就能够存储上一级来的数据,因此这种结构的FFT 可以进行流水线操作,能够对信号样本进行实时连续的运算。选择缓冲器的用途是拉齐数据,将RAM 输出的2个复数数据拆成4个实数数据输入到蝶形运算单元,完成蝶形运算后的数据进入选择缓冲器组合成2个复数数据输出。

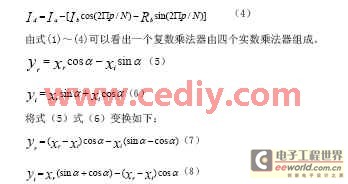

可见复数乘法需要的实数乘法由原来的4个变为3个,式中 因子可作为常数存入ROM,这样复数乘法只需3个实数乘法3个实数加法就可完成。由上述算法编程得到的蝶形变换器经综合后生成的原理图如图3所示。原理图中clk是时钟输入引脚;X_re,X_im,Y_re,Y_im分别是复数X,Y的实部和虚部;Cin代表 ;cms和cps分别表示 和 ;out1_re,out1_im,out2_re,out2_im代表蝶形变换后两个输出数据的实部和虚部。

地址产生及控制单元对整个参与FFT运算的数据的存储、读写时序进行控制,是 FFT 运算器的重要组成部分。地址产生及控制单元将要产生每一阶运算单元输入数据的读写地址、存储器的读写、使能等控制信号,同时还要产生旋转因子系数的读出地址,将配对的数据和旋转因子系数按序送入蝶形运算单元,从而实现每一阶的蝶形运算。地址产生及控制单元的设计方法主要是利用有限状态机进行设计。针对每一阶运算单元的运算过程划分成不同的状态,不同的状态下输出不同的数据地址和控制信号。

表1列出了计算一帧1024点FFT占用FPGA内部资源的情况。经后仿真时序分析,该激光告警系统在系统时钟为50MHz的情况下,完成一帧1024点 FFT只需110μs,加上数据载入时间和数据读取时间只需230μs,满足实时处理的要求。从表中可以看出, FFT子模块完成后, FPGA还有大量资源可以利用,因此剩余资源可用于采集模块,从而在一块芯片上完成多种功能,有效减少了激光告警机的体积。

在信号处理前直接对FPGA的输入信号用Matlab仿真的频谱如图4,可见激光信号的波长峰值在523nm附近,数据在FPGA中进行FFT之后输出的数据经过倒序后得到的频谱结果如图5,对比两图可知FPGA输出与Matlab仿真结果基本相同,从而验证了告警系统的正确性。

4 总结

本文介绍了为激光告警机探测目标激光的波长所开发的CCD相机信号采集与快速处理系统设备的设计。该系统利用FPGA实现对Atmel公司的AViiVA M2 CL型线阵CCD相机输出数据的采集与处理,电路简单,可靠性强,充分利用了FPGA支持多信号标准、支持流水作业工作模式、内设块存储器等特点。

本文作者创新点:在电路设计方面:摆脱了以往Cameralink接口型相机在与信号处理器进行通信时必须在相机和处理器之间加入电平转换芯片的做法,充分利用了FPGA支持LVDS电平的优势,从而减小了告警系统的电路体积和复杂度,在硬件方面提高了系统的可靠性。在程序设计方面:充分利用FPGA内部 RAM资源,多处用到FIFO存储器,以流水作业为手段,缩短了系统响应时间。