1 引言

PC/104嵌入式控制PC出现于80年代末,并于1992年形成IEEEP966.1标准,它既继承了所有的PC资源,又在结构、体积、功耗、可靠性等方面重新进行了设计,使之与IBM PC完全兼容,并具有了体积小、功耗低、工作温度范围宽、可靠性高等特点。PC/104嵌入式控制PC采用了独特的“自栈式”总线连接,模块化结构,使用起来灵活方便。它所采用的面向对象的硬件设计方法使得在PC/104标准上开发的扩展模块具有更强的通用性和更长的生命期。同台式PC机一样,PC/104嵌入式控制PC也提供两个RS-232串行口。串行通信端口在数据通信中一直扮演极重要的角色,它不仅没有因为时代的进步而被淘汰,反而在规格上愈来愈向其极限挑战。常用的串行通信接口有RS-232和RS-485两种,近年来盛行的USB和IEEE 1394也属于串行通信的延伸。RS-232主要用于点对点通信,特别是通过MODEM进行远距离的两点之间的通信;RS-485主要用于多机通信,采用平衡差分电路双线传输,总线连接,距离在1km以内时最大速率是100kbps,允许并联32台驱动器和32台接收器以半双工方式工作。

PC/104所提供的两个串行口资源在很多情况下会不够用,这是因为,不仅使用串行口的外设在增加,而且串行口的功能也在扩展。比如,有些PC/104可将接到串行口的设备作为系统控制台使用,占用了宝贵的串行口资源;串行口通信所具有的优点使其成为计算机之间通信的首选,随着计算机之间通信需求的增加,尤其在多机通信中,串行口资源就不够用;在一些PC/104中,两个串口的地址往往是不能改变的,给使用带来不便; PC/104不提供RS442或RS-485串行口,在需要利用RS485总线实现多机通信时就必须另外配备转换器。针对这些困难,解决的方法就是按照PC/104标准开发扩展通信板。

本设计是根据实际系统的需求开发的,设计中利用集成异步通信单元结合外围接口电路并按照PC/104标准设计开发了扩展串口通信板,板上提供了两个RS-232串行口和两个RS-485串行口,串行口地址和中断请求号可由用户选择。设计中也考虑了扩展通信板的通用性,所设计的通信板符合PC/104标准,支持即插即用,用户可根据需要和系统资源条件设置串行口地址和中断请求号,因此,本设计也可作为开发PC/104标准串口通信板的参考。另外,在本设计中RS-485串行口的硬件电路中有一个独特的结构,结合通信协议,可实现信号极性的自动识别和转换。

2 通信板的设计方法

2.1 总体结构

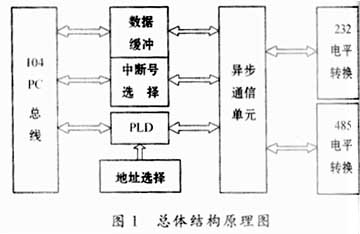

本设计的总体结构原理如图1所示。

图中PC/104总线是兼容于PC/AT的ISA总线,设计中使用了8位数据信号D0~D7,它们通过数据缓冲电路连接异步通信单元;10根地址线A0~A9,读写控制信号IOR,IOW,地址使能信号AEN和复位信号RESET,这些信号同地址选择电路以及PLD电路中设计的逻辑电路一起完成串行口的地址选择和各种逻辑控制,对每一个串口的内部寄存器的操作由地址的低3位A0,A1,A2选择确定;中断号选择电路结合PLD电路提供了IRQ3,4,5,7,9,10,11,15 这8个中断请求号供选择。

异步通信单元使用TI公司的TL16C554,它包含了4个异步收发单元,每一个都与16550兼容,加上电平转换电路就可构成一个串行口。

RS-232电平转换电路采用MAX213,它提供了5路232到TTL电平的转换和4路TTL到232电平的转换,一片MAX213就可实现完整的RS-232接口功能。

RS-485电平转换电路采用SN75176,它提供了485标准电平与TTL电平之间的转换,接收和发送部分可单独控制。

数据缓冲由74HC245承担,其传输方向由主机IOR信号控制,片选信号由PLD电路产生。

地址选择电路提供用户设置串行口地址,通过短路块的连接将地址的高4位A6~A9置0或置1。

2.2 异步通信单元

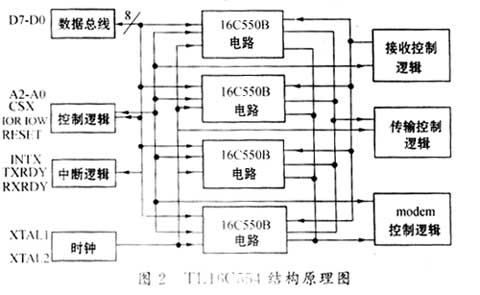

TL16C554是TI公司的产品,集成度高,性能稳定。其内部包含了4个可独立操作的可编程异步收发单元16C550,它们共用了数据线D7~D0、内部寄存器地址线A2~A0、读写信号线IOR和IOW、DMA读写控制TXRDY和RXRDY、复位RESET、时钟XTL1和XTL2。每个收发单元都有自己的片选信号CS、中断请求INT、数据输出TX、数据输入RX及MODEM逻辑控制信号CTS,DCD,DSR,DTR,RI,RTS。其内部功能模块如图2所示。

每一个内部的异步收发单元都等同于一个16550,它向下兼容16450,包含了16字节的先进先出寄存器,从而减少了对CPU的中断次数。可编程设定的波特率最大可达1Mbps,接口的字符结构可由用户选择,自动完成起始位、停止位、奇偶校验位的加入和删除,具有可程序化中断控制和完整的MODEM控制逻辑功能。

2.3 PLD电路

考虑到104标准的尺寸限制,设计中应尽量采用紧凑的结构,因此,用PLD电路来产生异步通信单元、数据缓冲电路的控制信号,还利用此电路实现485连接时信号极性的自动转换。

PLD电路采用了ALTERA公司的EPM7064,它包含了4个逻辑阵列块,64个宏单元,有1250个逻辑门可供使用。开发工具为MAX+PLUSⅡ。

PLD电路主要完成以下功能:

·每一个异步收发单元的选择。利用8根地址信号A9-A3和读写控制信号IOR,IOW之间的逻辑关系产生片选信号,其中,A9-A6位地址信号同地址选择电路的信号一起先送到一个四位比较器中进行地址比较,地址选择电路可由用户设定,这样就增加了用户对地址的选择范围和使用的灵活性。

·双向数据缓冲器的片选。利用A9-A6和读写控制信号产生。

·485信号极性选择。485采用总线方式连接,利用差分方式传输,两根连接线之间的信号正负极性不同,使用时必须使同极性端相连。当节点之间比较远,或者使用者并不清楚信号线的极性关系时,往往不能保证接线的正确,因此,我们设计了极性的自动转换电路。基本思路是这样的,设置一个电子开关,在通信初始化期间由主机发一个固定的测试信号,如果从机发现接收到的信号不对,就切换电子开关换向,如果接收到的测试信号正确,就保持原来的连接。电子开关由异或门充当,它可以反转或保持发送和接收的信号,即,当输入端中的一个信号置1时就可使另一个输入信号在输出端反相,而当将其置0时输出信号保持不变。电子开关的控制由D触发器实现,在初始化期间从机根据所接收信号的正误,选通D触发器,产生合适的电平,实现电子开关的控制。以上逻辑关系都由PLD电路完成。

3 结束语

本设计中,因高集成度串行口异步收发芯片和PLD电路的使用提升了电路的性能,所制作的印刷电路板结构紧凑,抗干扰性好,在几种不同型号104/PC机上使用时表现出了良好的兼容性和稳定性。