随着SoC技术应运而生的是SOPC技术。它结合了SoC和FPGA的优点,可裁减、可扩充、可升级,并具备软硬件在系统中可编程的功能。SOPC能够提供更好的性能以及更低的功耗,有效节省电路板空间并降低产品的总成本,电子工业正逐渐向SOPC设计转移,使SOPC成为现代电子系统的最佳选择之一。在充分研究EPA网络通信和SOPC技术的基础上,开发了一种基于SOPC技术的EPA控制器。

SOPC技术

SOPC技术是美国Altera公司于2000年最早提出的,并同时推出了相应的开发软件Quartus II。SOPC是基于FPGA解决方案的SoC,与ASIC的SoC解决方案相比,SOPC系统及其开发技术具有更多的特色,并具备以下的基本特征:至少包含一个以上的嵌入式处理器IP核;具有小容量片内高速RAM资源;丰富的IP核资源可供灵活选择;有足够的片上可编程逻辑资源;处理器调试接口和FPGA编程接口共用或并存;可包含部分可编程模拟电路;单芯片、低功耗。

SOPC是一种新的系统设计技术,也是一种新的软硬件综合设计技术。通过它,可以很快地将硬件系统(包括微处理器,存储器,外设以及用户逻辑电路等)和软件设计都放在一个可编程的FPGA芯片中,以达到系统的IC设计。这种设计方式,具有开发周期短以及系统可修改等优点。设计完成的SOPC可以通过HARDCOPY转为ASIC芯片,从而可以实现快速量产。

EPA现场控制器设计

针对控制系统中连接管理网、控制网和现场设备单元的要求,采用SOPC技术、现场总线技术和自动控制技术,设计一种适用于EPA工业以太网的控制器,并在其可编辑软核的CPU处理器上实现了实时操作系统及EPA通信协议栈。该EPA现场控制器可实现实时控制信息的输入输出,并对以太网上的其他的EPA设备进行监控、显示和故障报警。本文将针对该EPA控制器的基于SOPC技术的CPU核心处理模块和通信处理模块分别进行说明。

EPA现场控制器的硬件设计总体方案

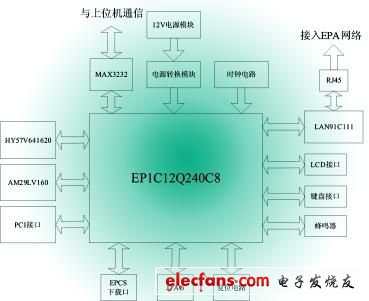

图1是EPA现场控制器的硬件系统结构框图。整个设计中,硬件上实现EP1C12Q240C8芯片、LAN91C111芯片的外围接口电路的设计;实现了串口通信和网络通信的设计;实现了复位电路、JTAG、时钟电路、电源电路的设计;实现了键盘电路、LCD显示电路、蜂鸣器报警电路的设计;实现了HY57V641620芯片、AM29LV160芯片外围电路的设计,拓展了丰富的存储器资源,可移植linux、windows CE操作系统等;拓展了总线接口,可以根据工业现场的实际需要接入相应的板卡(如DI/DO模块、AI/AO模块,实现与现场数据之间的数模、模数转换、拓展MMC存储卡,拓展其存储容量等)。

图1基于FPGA的EPA控制器的硬件结构框图

在设计时,考虑到由于该控制器的结构、功能较为复杂,涉及到的器件种类较多。所以在设计时,将硬件板卡分为两部分来做。第一部分:CPU核心处理模块,包含CPU处理器EP1C12Q240C8、存储器(FLASH、SDRAM)、电源部分、时钟源、JTAG、EPCS下载口和复位电路。第二部分:通信处理模块,包含网络通信(LAN91C111网卡芯片和RJ45)、串口通信(MAX3232)、LCD接口、键盘接口和蜂鸣器。基于SOPC技术的CPU核心处理模块

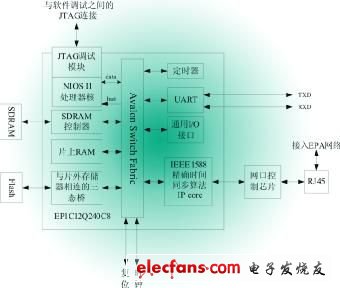

整个方案的实现是以接入实时工业以太网络为目的,在芯片内部实现部分EPA协议,同时控制器实现对工业以太网上的其他设备的监控、显示及数据分析。设计中采用Altera公司的新一代低成本的FPGA芯片EP1C12Q240C8芯片,该芯片包含有12060LE(逻辑单元),可根据实际需要,配置其NIOSⅡCPU软核、与CPU相连的片内外设和存储器以及与片外存储器和片外设备相连的接口等。其芯片系统结构框图如图2所示。

图2 芯片系统结构框图

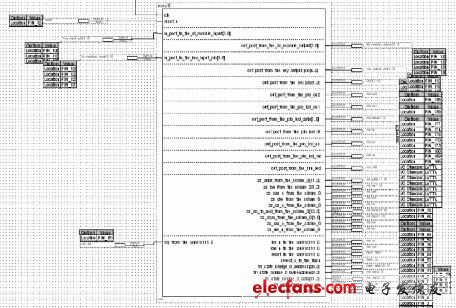

整个CPU处理器的硬软件设计均在Quartus II 5.1版本上实现。NIOSⅡ处理器核是Altera公司的第二代用户可配置的通用32位RISC软核微处理器,是Altera公司特有的基于FPGA架构的可配置的软CPU内核,其特性和外设可根据实际需要进行增加或剪裁。所有NIOSⅡ处理器系统使用统一的指令和编程模型,并有三种类型以满足不同设计的要求,分别是快速型、经济型和标准型。在本控制器中,所定制的NIOSⅡ软核选用快速型,该内核处理速度为49DMIPS,耗费的逻辑门数为1400~1800LE,同时带有硬件乘法器和硬件除法器。根据EPA网络对控制器的要求,添加与CPU相连的片内外设和片外设备接口:SDRAM控制器、片内RAM、三态桥、UART、定时器、通用I/O口、LCD显示驱动电路和以太网接口。按照设计要求,在Quartus II 5.1版本下的对CPU的配置情况如图3所示。FPGA芯片可根据实际需要灵活地增加功能,同样对不必要的功能也可进行删减,以满足快速、高效和低成本的设计。

图3 EP1C12Q240C8芯片配置情况

在配置完CPU处理器的内部结构以后,按照设计需要对CPU的外围进行配置。由于该控制器是接入EPA网络,需要实现EPA协议,而FPGA芯片EP1C12Q240C8的内部只有288K的RAM,所以在片外扩展了16M bits的FLASH-AM29LV160D和64M bits的SDRAM-HY57V641620的。从外部引入12V的直流电源,经过电平转换以后得到3.3V和1.5V的电源,为CPU、存储器及其他受电设备供电。CPU上的时钟源使用的是50MHz的钟振。JTAG和EPCS下载口用于硬软件的下载。将在Quartus Ⅱ上编辑的硬件程序和软件程序通过JTAG和EPCS下载口,下载到FLASH和RAM(片内或者片外)中,可进行在线调试。该复位电路是由10KW电阻、10mF电容和按键组成,可实现按键低电平复位和上电低电平复位。通信处理模块

整个设计以FPGA芯片EP1C12Q240C8为数据处理中心,通过网络通信,完成对工业以太网上的其他设备的数据通信,同时通过MAX3232实现和上位机的串口通信。在该模块中,加入了LCD接口、行列式键盘接口和蜂鸣器接口,对工业以太网上的其他EPA设备进行监控和显示,有较好的人机交互的功能。

在该设计中,网络通信分为有线和无线两种通信方式。其中,有线网络通信使用的是10M/100M的LAN91C111的自适应网卡芯片,并通过RJ45网口接入EPA网络。LAN91C111是SMSC公司为嵌入式应用系统推出的第三代快速以太网控制器。LAN91C111的芯片上集成了遵循SMSC/CD协议的MAC(媒体层)和PHY(物理层),符合IEEE802.3/802.U-100Base-Tx/10Base-T规范。在本控制器上预留了蓝牙模块和ZigBee模块的无线通信接口,作为辅助处理模块。可根据工业现场的实际情况,接入无线通信模块,实现与EPA网络的无线通信,通过该模块能够监测无线现场设备的运行情况及相关参数。

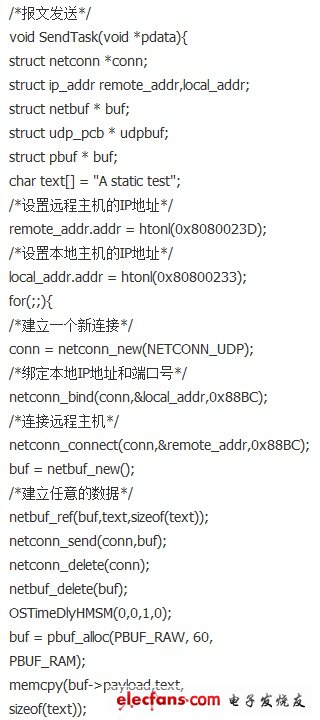

在整个EPA通信协议栈网络层和传输层接收报文处理流程中。NIOSⅡ处理器复位后初始化UC/OS Ⅱ操作系统、网络接口、堆栈以及定时器等外围设备接口。从外部存储器FLASH中获取IP地址和MAC地址等网络信息。当收到的报文IP地址和MAC地址都是本机地址时,把报文以LWIP所要求的特殊结构体形式存储在接收缓冲区中,然后发送到EPA协议栈中进行处理,当检查到UDP端口号是0x88BC时,将报文交由EPA应用层处理模块进行处理。

图4 EPA协议栈接收报文处理流程图

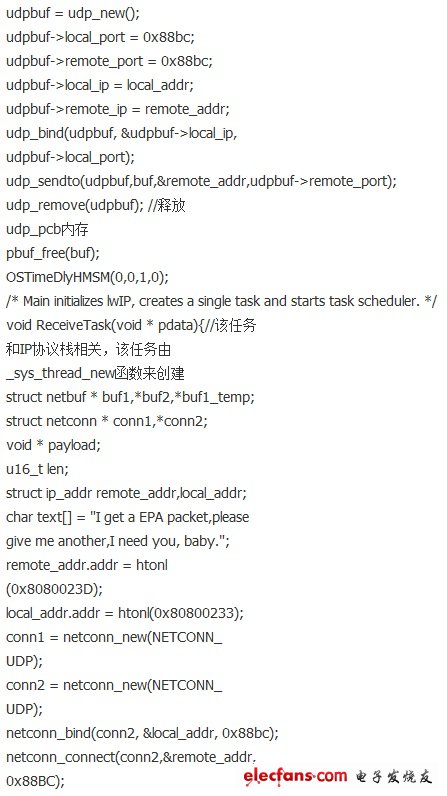

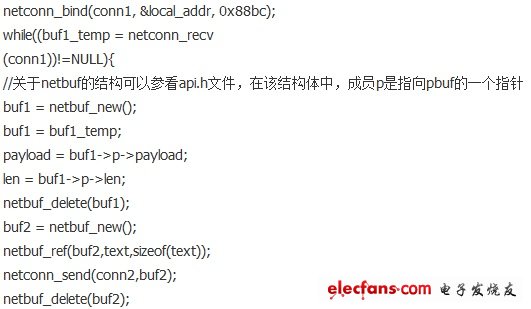

其部分报文处理程序如下:

结语

在完成整个设计,控制器接入EPA网络中能够正常运行。由于控制器中的处理器使用的是FPGA芯片,有较强的灵活性,能够进行编程、除错、再编程和重复操作,因而可以充分地进行设计开发和验证。当电路有少量改动时候,更凸现出其优势,其现场编程能力可以延长产品在市场上的寿命,可以用来系统升级,从而大大提高了控制器的性能。