0 引言

准确获取电网基波及谐波电压的相位角,在变频器、有源滤波器等电力电子装置中具有重要的意义,通常需要采用锁相环得以实现。传统锁相环电路一般由鉴相器、环路滤波器、压控振荡器及分频器组成,其工作原理是通过鉴相器将电网电压和控制系统内部同步信号的相位差转变成电压信号,经环路滤波器滤波后控制压控振荡器,从而改变系统内部同步信号的频率和相位,使之与电网电压一致。传统锁相环存在硬件电路复杂、易受环境干扰及锁相精度不高等问题,随着大规模集成电路及数字信号处理器的发展,通过采用高速DSP 等可编程器件,将锁相环的主要功能通过软件编程来实现。本文设计的锁相环控制系统采用数字处理器TMS320F2812 芯片实现对电网基波及特定次谐波电压相位的跟踪和锁定。

1 软件锁相环的设计方案

1.1 工作流程

基于DSP的软件锁相环设计此方案的基本思路是通过采样电压过零点获取同步信号,采用DSP 内部定时器的循环计数产生同步信号来实现压控振荡器和分频器的功能,即通过改变定时器的周期或最大循环计数值的方法来改变同步信号的频率和相位,同时对电压进行A/D 转换及数据处理,得出基波及谐波电压的相位与频率,调整SPWM 正弦表格指针地址完成对基波及谐波电压的锁相功能,其工作流程如图1 所示。

通常,过零信号可以通过检测电网三相电压中任一相的过零点获取。在图1 中,以检测A相电压过零点作为过零信号,将通过上升沿捕捉及软件滤波后产生的中断作为采样周期同步信号,当DSP内部时钟倍频后产生的中断在捕获到输入电压信号在过零点时,将发正弦信号的指针归零,以保证输入电压信号过零时DSP发出的基准正弦信号也同步过零,从而实现相位同步。本文采用SPWM 触发模式,基准正弦信号是一个正弦数据表格,控制逆变器输出的基准点;同时采样电压信号,经DSP进行FFT计算分析其相位和频率、基波及谐波与A相电压过零点相位差,通过修改定时器周期寄存器来改变SPWM 输出时正弦波的频率;以修改比较寄存器来改变SPWM 输出时正弦波的相位,这样完成了对基波及谐波电压的相位锁定。

1.2 过零检测电路的设计

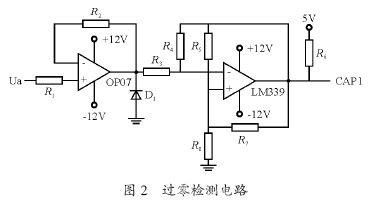

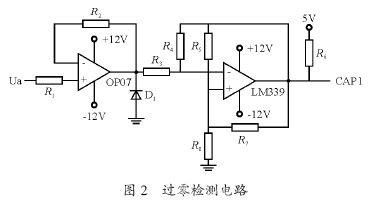

过零信号对系统相位捕捉的精准性影响较大,系统设计时采用软硬件结合的办法实现对过零信号的捕捉。获取过零信号实质上是为了给系统提供一个同步信号,即每次信号过零时启动A/D转换。在本设计中,过零检测电路采集A相电压每个周期的过零点作为系统产生的中断信号CAP1,使中断服务程序开始执行,图2 为电压信号过零检测电路。

图2 中,在比较器芯片LM339 的输出端选择加装了上拉电阻,主要是考虑到整个电路对驱动、功耗和速度的要求。电阻R7和R8构成一个滞回比较器,输出信号通过反馈电阻R7 改变同相端的参考电压,以消除输入信号正反过零产生的抖动。

1.3 过零捕捉的软件实现

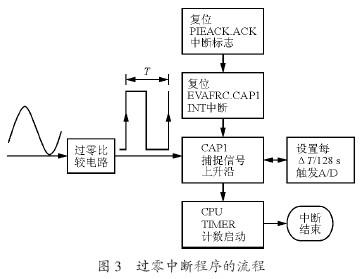

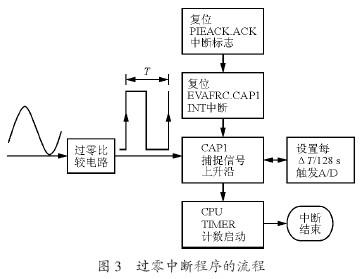

过零检测主要解决的是采样同步问题,当检测到的电压信号由负到正过零时,比较器芯片LM339 输出端产生上升沿,将此信号输入到DSP2812 事件管理器EVA 的引脚CAP1。引脚CAP1 在系统初始化程序中预设置为上升沿触发中断,因此当过零信号到来时,CAP1中断子程序开始执行,开启事件管理器EVA 的TIMER 周期中断,周期设置为驻T/128 s(每周期采样128 个点),触发A/D 模块采样。其中,驻T 为CAP1 捕捉到的两个过零检测信号上升沿的间隔时间,等于电网待测信号的周期T,图3 为过零中断程序的流程。

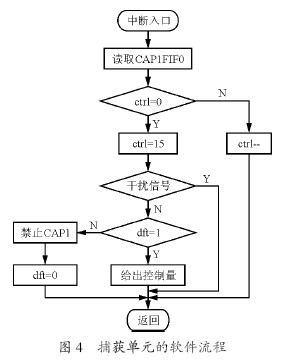

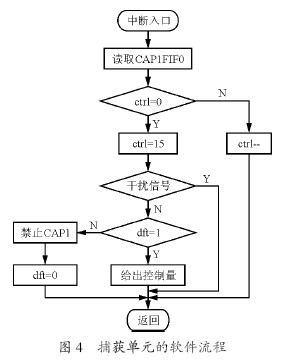

DSP 的捕获单元CAP隶属于事件管理器,它能够捕捉到CAP 外部引脚的跳变,当捕捉到对应引脚发生特定的跳变时,触发相应的中断,并将定时器的值存入一个两级深的FIFO堆栈中。本方案设计每16 点启动一次数据分析,同时投出一次控制量,这个过程为一个更新周期,判断标志ctrl 用来检测是否进入新的更新周期,以判断是否需要启动新一轮数据分析和投出控制量。标志位dft用来判断当前数据分析状态,为0 时表示重新初始化数据分析操作,为1 时表示数据分析操作完毕,为2 时表示允许启动新一轮数据分析,为3 时表示当前正在进行数据分析。图4 给出了捕获单元的软件流程。

1.4 过零信号的软件滤波

CAP1 捕捉到的两个过零信号上升沿的间隔时间,即两个CAP1中断事件的间隔时间,等于电网待测信号的周期T。TIMER 在系统初始化后不断计数,然后在CAP1 的中断服务程序中记录两个CAP1 中断事件之间的TIMER 计数值N,可计算出T。同时,采用软件滤波来判断CAP1信号是否为毛刺干扰,其过程如下:电网基波频率波动一般不超过依0.2 Hz,当产生CAP1中断时,可以计算本次与前次的计数差值,如果远小于工频周期计数差值,则认为捕获的中断为干扰产生,如该中断非连续两次以上出现,则中断返回。同时对产生的中断次数进行累加,达到设定范围时对电压过零时刻正弦表格的指针位置进行判断,调整正弦表格指针地址,实现过零指针的校准。

1.5 A/D转换及相频计算

过零信号经过软件滤波及校准后,在捕获到输入电压信号过零点时,直接将发正弦信号的指针归零,保证输入电压信号过零时DSP发出的基准同步过零,从而实现相位同步。A相电压过零信号送入管脚CAP1,作为一个采样周期的基准,该周期的128 倍频信号作为每次ADC 启动基准。在系统初始化后开启CAP1,并设置启动ADC、相应的模数转换、数据分析、控制量投出等操作,直到关机或者发生故障。由于F2812 的系统时钟频率非常高,为150 MHz,即中断服务程序的响应延迟时间非常小,可以忽略。在CAP1 的中断服务程序中,根据待测信号周期T来设置F2812 事件管理器的通用定时器TIMER,每隔驻T/128 s自动启动一次A/D转换进行数据采集。

0 引言

准确获取电网基波及谐波电压的相位角,在变频器、有源滤波器等电力电子装置中具有重要的意义,通常需要采用锁相环得以实现。传统锁相环电路一般由鉴相器、环路滤波器、压控振荡器及分频器组成,其工作原理是通过鉴相器将电网电压和控制系统内部同步信号的相位差转变成电压信号,经环路滤波器滤波后控制压控振荡器,从而改变系统内部同步信号的频率和相位,使之与电网电压一致。传统锁相环存在硬件电路复杂、易受环境干扰及锁相精度不高等问题,随着大规模集成电路及数字信号处理器的发展,通过采用高速DSP 等可编程器件,将锁相环的主要功能通过软件编程来实现。本文设计的锁相环控制系统采用数字处理器TMS320F2812 芯片实现对电网基波及特定次谐波电压相位的跟踪和锁定。

1 软件锁相环的设计方案

1.1 工作流程

基于DSP的软件锁相环设计此方案的基本思路是通过采样电压过零点获取同步信号,采用DSP 内部定时器的循环计数产生同步信号来实现压控振荡器和分频器的功能,即通过改变定时器的周期或最大循环计数值的方法来改变同步信号的频率和相位,同时对电压进行A/D 转换及数据处理,得出基波及谐波电压的相位与频率,调整SPWM 正弦表格指针地址完成对基波及谐波电压的锁相功能,其工作流程如图1 所示。

通常,过零信号可以通过检测电网三相电压中任一相的过零点获取。在图1 中,以检测A相电压过零点作为过零信号,将通过上升沿捕捉及软件滤波后产生的中断作为采样周期同步信号,当DSP内部时钟倍频后产生的中断在捕获到输入电压信号在过零点时,将发正弦信号的指针归零,以保证输入电压信号过零时DSP发出的基准正弦信号也同步过零,从而实现相位同步。本文采用SPWM 触发模式,基准正弦信号是一个正弦数据表格,控制逆变器输出的基准点;同时采样电压信号,经DSP进行FFT计算分析其相位和频率、基波及谐波与A相电压过零点相位差,通过修改定时器周期寄存器来改变SPWM 输出时正弦波的频率;以修改比较寄存器来改变SPWM 输出时正弦波的相位,这样完成了对基波及谐波电压的相位锁定。

1.2 过零检测电路的设计

过零信号对系统相位捕捉的精准性影响较大,系统设计时采用软硬件结合的办法实现对过零信号的捕捉。获取过零信号实质上是为了给系统提供一个同步信号,即每次信号过零时启动A/D转换。在本设计中,过零检测电路采集A相电压每个周期的过零点作为系统产生的中断信号CAP1,使中断服务程序开始执行,图2 为电压信号过零检测电路。

图2 中,在比较器芯片LM339 的输出端选择加装了上拉电阻,主要是考虑到整个电路对驱动、功耗和速度的要求。电阻R7和R8构成一个滞回比较器,输出信号通过反馈电阻R7 改变同相端的参考电压,以消除输入信号正反过零产生的抖动。

1.3 过零捕捉的软件实现

过零检测主要解决的是采样同步问题,当检测到的电压信号由负到正过零时,比较器芯片LM339 输出端产生上升沿,将此信号输入到DSP2812 事件管理器EVA 的引脚CAP1。引脚CAP1 在系统初始化程序中预设置为上升沿触发中断,因此当过零信号到来时,CAP1中断子程序开始执行,开启事件管理器EVA 的TIMER 周期中断,周期设置为驻T/128 s(每周期采样128 个点),触发A/D 模块采样。其中,驻T 为CAP1 捕捉到的两个过零检测信号上升沿的间隔时间,等于电网待测信号的周期T,图3 为过零中断程序的流程。

DSP 的捕获单元CAP隶属于事件管理器,它能够捕捉到CAP 外部引脚的跳变,当捕捉到对应引脚发生特定的跳变时,触发相应的中断,并将定时器的值存入一个两级深的FIFO堆栈中。本方案设计每16 点启动一次数据分析,同时投出一次控制量,这个过程为一个更新周期,判断标志ctrl 用来检测是否进入新的更新周期,以判断是否需要启动新一轮数据分析和投出控制量。标志位dft用来判断当前数据分析状态,为0 时表示重新初始化数据分析操作,为1 时表示数据分析操作完毕,为2 时表示允许启动新一轮数据分析,为3 时表示当前正在进行数据分析。图4 给出了捕获单元的软件流程。

1.4 过零信号的软件滤波

CAP1 捕捉到的两个过零信号上升沿的间隔时间,即两个CAP1中断事件的间隔时间,等于电网待测信号的周期T。TIMER 在系统初始化后不断计数,然后在CAP1 的中断服务程序中记录两个CAP1 中断事件之间的TIMER 计数值N,可计算出T。同时,采用软件滤波来判断CAP1信号是否为毛刺干扰,其过程如下:电网基波频率波动一般不超过依0.2 Hz,当产生CAP1中断时,可以计算本次与前次的计数差值,如果远小于工频周期计数差值,则认为捕获的中断为干扰产生,如该中断非连续两次以上出现,则中断返回。同时对产生的中断次数进行累加,达到设定范围时对电压过零时刻正弦表格的指针位置进行判断,调整正弦表格指针地址,实现过零指针的校准。

1.5 A/D转换及相频计算

过零信号经过软件滤波及校准后,在捕获到输入电压信号过零点时,直接将发正弦信号的指针归零,保证输入电压信号过零时DSP发出的基准同步过零,从而实现相位同步。A相电压过零信号送入管脚CAP1,作为一个采样周期的基准,该周期的128 倍频信号作为每次ADC 启动基准。在系统初始化后开启CAP1,并设置启动ADC、相应的模数转换、数据分析、控制量投出等操作,直到关机或者发生故障。由于F2812 的系统时钟频率非常高,为150 MHz,即中断服务程序的响应延迟时间非常小,可以忽略。在CAP1 的中断服务程序中,根据待测信号周期T来设置F2812 事件管理器的通用定时器TIMER,每隔驻T/128 s自动启动一次A/D转换进行数据采集。

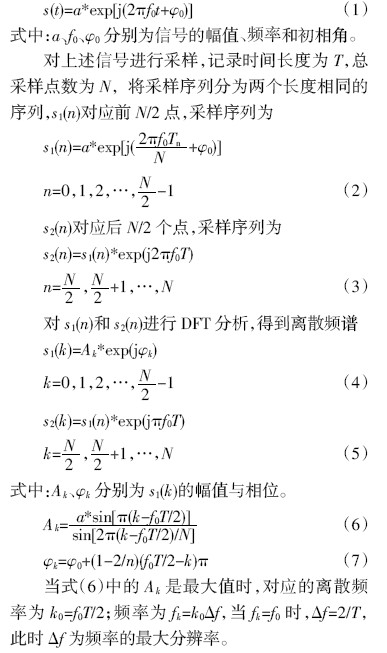

A/D 转换后的信号使用滑动窗口的FFT 算法,以滑动窗口的DFT和Pruning-FFT为基础,利用DFT对特定次谐波进行选择计算,根据滑动窗口快速响应以及Pruning-FFT 快速计算的特点,使DSP的处理速度达到理想值。使用FFT进行相位和频率分析的原理如下。

对某一单一频率信号

通过上述分析得出初相角、频率,将数据存入对应寄存器中,完成基波及谐波的相频计算功能。

1.6 SPWM输出的相频调整

软件锁相输出是由捕获中断和定时器中断共同完成,捕捉中断可以完成电压周期和相位的计算,定时器中断用来输出SPWM波形。在本方案中,三角载波是利用通用定时器的连续增减计数模式产生的,当通用定时器有效后,开始递增计数,直到等于周期寄存器的值,定时器开始递减计数,递减到零时,重新开始递增计数,并重复以上过程,从而形成三角载波信号。得到三角波后,通过比较单元来控制输出波的极性,产生PWM 波。

TMS320F2812 系列DSP 片内带有比较单元,可提供6对可编程的PWM信号,这为实现上述算法提供了极大的便利。当定时器发生周期中断时,就需要重新装载比较器的值,即此刻的正弦值。设定载波比为21(载波比应为奇数且能被3 整除),即1个正弦波的周期等于21 个载波的周期,则相邻的两个三角波峰值对应的正弦波相位差为360毅/21= 17.143毅,假定上一周期中断装载的正弦值为sin兹,则本周期中断所需装载的正弦值为sin(兹+17.143毅)。

例如:输出正弦信号的频率为250 Hz(5 次谐波)时,其三角波的频率则为5.25 kHz。三角波信号由定时器模拟产生,则定时器的定时周期为

5 次谐波的初相角兹是电压经FFT 计算得到与A相电压过零点的相位差值。根据x和兹值,产生相应的PWM 波。因正弦值实时计算时用得较多,在确定相位分辨率后,例如1毅,会导致大量重复计算。因此,采用查表法,按顺序预存一个周期为420 点的正弦值,相位的分辨率为360毅/420=0.857毅,因每次比较器的装载值是上一次移相17.143毅后的正弦值,所以只需将上一次装载值的地址加上一定的偏移量,即为本次所需的装载值地址,该偏移量为420/21=20。可见,将正弦计算简化为读相应地址的存储器值,会大大提高程序的效率。

通过读取寄存器中基波及谐波电压的初相角频率以及与过零点相位差的值,调整对应的正弦表格初相角指针地址,通过修改定时器周期寄存器来改变正弦波的频率,修改比较寄存器来改变正弦波的幅值和相位,在下一个过零信号过零点投出相位和频率控制量,即可完成对基波及谐波电压及SPWM 输出时的相位锁定。

2 实验结果与分析

在一台低压有源电力滤波装置中,采用基于TMS320F2812芯片为核心控制器的软件锁相环的设计方案。实验结果验证,该方案能够很好地实现对基波及特定次谐波电压相位的跟踪和锁定。

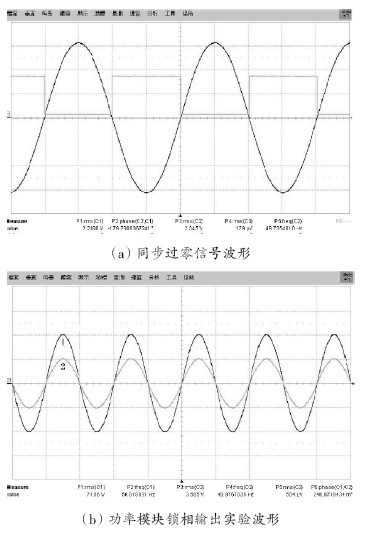

图5(a)给出同步过零信号波形,电压信号(正弦波)为A相电压,过零信号为方波。电路设计时将电压采样信号幅值转化为3.3 V,满足过零信号能被管脚CAP1 识别的条件。如图5(a)所示,过零信号与电压采样信号同步。

图5(b)给出功率模块锁相输出实验波形,图中波形1 为A相电压采样信号,波形2 为功率模块输出电流波形,控制器设定跟随电压采样信号的过零点触发功率模块同步输出。从实验结果可以看出,功率模块逆变输出电流相位能够与采样信号过零点保持同步,相位偏移极小,达到对电网基波电压锁相及跟踪输出的目的。

图5(c)给出功率模块锁相倍频输出实验波形。为方便观察谐波锁相输出的效果,设定5 次谐波初相角与基波过零点同相,控制器设定跟随电压采样信号过零点,反相输出5 次谐波电流,电流幅值不变。图中波形3 为采样点电压信号,波形4为控制器触发功率模块输出电流波形。如图所示,功率模块输出的5 次谐波电流初相角与采样信号保持过零同步。

实验结果表明:通过软件锁相环可以实现功率模块逆变输出电流与电压采样信号的同步,调整控制器程序,可以实现对谐波相位及频率跟踪,达到对电网电压及特定次谐波电压锁相及跟踪输出的目的。

3 结语

本文提出了一种基于DSP2812实现对电网电压软件锁相的技术方案。实验结果表明,该方案能很好地实现对电压信号周期及频率的实时跟踪。

采用软件锁相环技术,只需设计过零检测及信号调整电路,其它功能均由DSP芯片完成,减少了外界环境干扰的问题,提高了锁相精度。同时,DSP可以实时进行软件修改,能实现复杂控制,提高了其可操作和可扩展性。随着DSP性能的不断改进,其运算速度越来越快,将为软件锁相技术提供更多的发展空间。