PCI Express是由Intel,Dell,Compaq,IBM,Microsoft等PCI SIG联合成立的Arapahoe Work Group共同草拟并推举成取代PCI总线标准的下一代标准。PCI Express利用串行的连接特点能轻松将数据传输速度提到一个很高的频率,达到远远超出PCI总线的传输速率。一个PCI Express连接可以被配置成x1,x2,x4,x8,x12,x16和x32的数据带宽。x1的通道能实现单向312.5 MB/s(2.5 Gb/s)的传输速率。Xilinx公司的Virtex5" title="Virtex5">Virtex5系列FPGA芯片内嵌PCI-Express" title="PCI-Express">PCI-ExpressEndpoint Block硬核,为实现单片可配置PCI-Express总线解决方案提供了可能。

本文在研究PCI-Express接口协议和PCI-Express Endpoint Block硬核的基础上,使用Virtex5LXT50 FPGA芯片设计PCI Express接口硬件电路,实现PCI-Express数据传输。

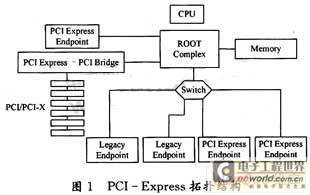

1 PCI Express的拓扑结构

PCI Express是一种能够应用于点设备、台式电脑、工作站、服务器、嵌入式计算机和通信平台等所有周边I/O设备互连的总线。其拓扑结构如图1所示,其中包含ROOT COMPLEX(RC)、多个终端(I/O器件)、开关和PCI Express/PCI桥路,它们通过PCI Express进行互联。

RC是I/O层次的根部,将CPU/存储器子系统与I/O相连。RC可以支持一个或多个PCI Express端口,例如英特尔芯片组。

开关定义为多个虚拟PCI之间的桥路器件的逻辑组,它们使用一种基于地址路由的PCI桥路机制来传递执行信息,例如IDT PCI Express开关。

端点是指能作为PCI Express执行的请求者或完成者的那一类器件,可以是PCI Express自身,也可以是一个非PCI Express器件,例如连接在PCI Express上的图形控制器。

PCIE总线保留了对于PCI局部总线协议全部软件的向下兼容性,即只要是PCIE的卡都可以插到支持PCI的操作系统上使用;在硬件上,两者不兼容,PCIE取代PCI,PCI-X的并行多路总线结构,采用一种串行、点到点的总线连接结构,需要的接口更少。

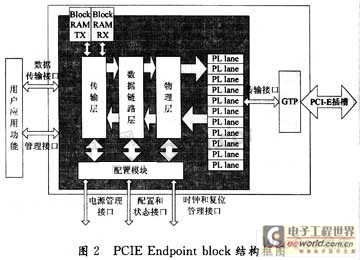

2 Virtex 5 Lxt PCIE Endpoint block

Virtex 5 Lxt PCIE Endpoint block集成了PCIE协议中的物理层(PHY)、数据链接层(DLL)和传输层(TL),同时它还实现了PCI-Express设备的功能配置寄存器,其结构框图如图2所示,包含有以下几个接口:时钟和复位接口、配置和状态接口、电源管理接口、用户接口和传输层接口。

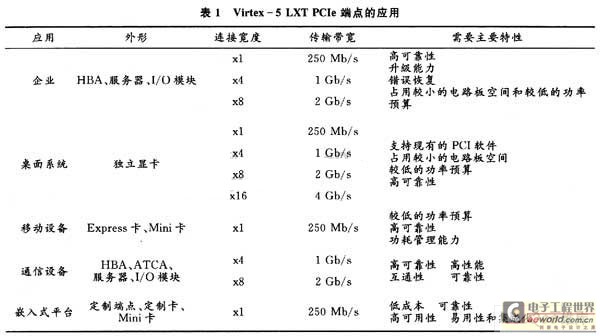

Virtex 5 Lxt PCIE Endpoint block具有PCI-Express的完整功能,完全符合PCIe基本规格v1.1版要求,作为FPGA内部的硬核,它是可配置的PCIe端点解决方案,大大增加设计的灵活性,降低设计的RNE费用,并且支持1x,2x,4x或8x通道的实现,为系统的功能扩张提供了有效途径;带有内置PCIe端点模块的Virtex-5 LXT FPGA芯片,能够被用于任何一种外形的产品设计,如表1所示。

3 总线接口" title="总线接口">总线接口设计实现

3.1 接口硬件设计

接口硬件主要由主控FPGA模块,电源管理模块,DDR高速缓存模块、和时钟管理模块组成。硬件结构框图如图3所示。

FPGA是整个设计的最关键部分,主要实现:PCI-Express硬核;在硬核的用户接口和传输接口实现PCI-Express传输本地总线的时序逻辑;并且在其内部完成DDR控制时序逻辑。FPGA是PCI-Express接口和DDR内存单元数据传输的通道。这里选择XilinxVirtex5系列FPGA中的V5LX50T芯片,封装形式为FFGll36。

在整个电路中,FPGA的功耗最大,因此在电源模块设计中,重点考虑FPGA因素。FPGA的功耗与设计有关,主要取决于器件的型号、设计的时钟频率、内部设计触发器翻转率和整个FPGA的资源利用率。这里使用Xilinx功耗分析工具XPower进行功耗分析,根据XPower提供的动态功耗和静态功耗分析结果,选择TI公司的相关电源模块。

DDR是比较常用的高速缓存单元,这里选择使用现代公司的HY5DU56822DT-D4,在PCI-Express传输过程中,对时钟的稳定性要求很高;Virtex5 FPGA内部的CMT模块的时钟综合处理能力可能达不到预想的效果,这里使用专门的时钟管理单元提供时钟,选择的是ICS874003芯片,通过FPGA管脚控制其时钟综合的效果。

3.2 软件设计

在实现PCI-Express数据传输过程中,构建数据传输流程如图4所示。

数据从PC内存通过PCI-Express接口向下传输到FPGA内部,FPGA内部DDR控制逻辑再将数据传输到的DDR内存芯片中存储,向下传输完毕后,FPGA内部逻辑从DDR芯片中将存储的数据读出,并且给每个数据按字节加‘1’,然后通过PCI-Express接口,再将数据传输回PC内存,PC内存程序对数据进行校验。

4 结 语

Virtex5系列FPGA芯片内嵌PCI-Express End-point Block硬核,为实现单片可配置PCI-Express总线解决方案提供了可能。基于Virtex5 FPGA的PCIExpress设计实现方式简单、配置灵活,适合于各种应用领域,降低了设计成本,缩短了产品上市时间,保证了产品的功能性和易用性,开创了高效率PCI Express开发的新时代。