移动产品应用领域,NANDFlash设备已成为人们解决高密度固态存储的专用方法。信息技术的飞速发展,人们对信息的需求量也越来越大。因此,大量数据在系统内部以及网络之间存储和传递时,对数据进行检测并更正可能出现的错误尤为重要。纠错码ECC(ErrorCorrect-ionCode)满足这一需求,其被称为ECC校验,是一种常用于NANDFlash读写控制器的校验编码。

ECC校验负责检测错误、维护ECC信息、更正由原数值改变了的单比特错误。所有ECC的操作处理都可由一个ECC模块来控制,其作为一种简单地存储一映射接口,放置在NAND器件和处理器接口之间。该模块一般包含Hamming编码产生模块和出错位置模块,分别用于产生ECC校验码和计算出错位置。

1Haremina编码

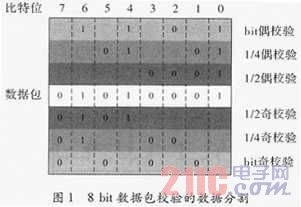

Hamming编码计算简单。广泛用于NANDFlash的Hamming算法,通过计算块上数据包得到2个ECC值。为计算ECC值,数据包中的比特数据要先进行分割,如1/2组、1/4组、1/8组等,直到其精度达到单个比特为止,以8bit即1Byte的数据包为例进行说明,如图1所示。

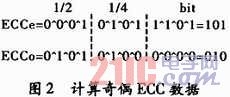

该数据按图1所示方式进行比特分割,分别得到上方的偶校验值ECCe和下方的奇校验值ECCo。其中,1/2校验值经“异或”操作构成ECC校验的最高有效位,同理1/4校验值构成ECC校验的次高有效位,最低有效位由具体到比特的校验值填补。图2展示了两个ECC校验值的计算过程。

即偶校验值ECCe为“101”,奇校验值ECCo为“010”。图1所示为只有1Byte数据的数据包,更大的数据包需要更多的ECC值。事实上,每nbit的ECC数值可满足2nbit数据包的校验要求。又由于这种Hamming码算法要求一对ECC数据(奇偶),所以总共要求2nbit的ECC校验数据来处理2nbit的数据包。

计算之后,原数据包和ECC数值都要写入NAND器件。稍后,原数据包将从NAND器件中读取,此时ECC值将重新计算。如果新计算的ECC不同于先前编入NAND器件的ECC,那么表明数据在读写过程中出错。

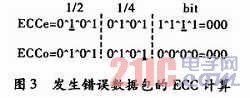

例如,原始数据01010001中有1个单一的比特出现错误,出错后的数据是01010101。经前面所示方法计算,从图3中可以清楚地看到由于数据发生了变化,2个新的ECC数值已不同与原来的ECC值。

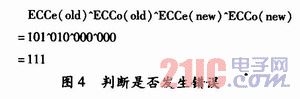

此时把所有4个ECC数值进行按位“异或”,就可以判断是否出现了1个单一比特的错误或者是多比特的错误。如果计算结果为全“0”,说明数据在读写过程中未发生变化。如果计算的结果为全“1”,表明发生了1bit错误,如图4所示。如果计算结果是除了全“0”和全“1”的任何一种情况,那么就是2bit出错的情况。2bit错误总可以检测到,然而,Hamming码算法仅能够保证更正单一比特的错误。如果两个或是更多的比特出错,那么就不能修改该出错的数据包,在这种情况下,Hamming算法就可能不能够指示出已经出现的错误。不过,考虑到SLCNAND器件的比特错误的情况,出现2、3bit错误的可能性非常低。

对于1bit错误的情况,出错地址可通过将原有ECCo值和新ECCo值进行按位“异或”来识别获取。通过图5中的计算,结果为2,表明原数据第2bit位出现了问题。该计算采用奇校验数据ECCo,这是因为它们可以直接地反映出出错比特的位置。

![]()

找到出错比特后,只要通过翻转它的状态就可修复数据包,具体操作也就是将该位与“1”进行异或操作,如图6所示。

![]()

2扩展数据包

在上述举例中,校验1个8bit数据包需要6bit的ECC数据。在这种情况下,校验数据量达到原始数据包的数据量的75%,看上去并不令人满意。然而,随着数据包大小的增加,Hamming算法将表现得越来越有效率。由前面2nbit数据需要2nbitECC校验的关系推知,每增加一倍的数据要求两个额外的ECC信息比特。这样,当数据增加到,比如512Byte时,仅产生24bit的ECC,此时用于校验的数据占原数据的比例降为0.06%,效率较高。下面,以1个8Byte的数据包为例说明扩展数据包的校验情况。

在这里,由于异或操作满足交换律,用一种更为有效的方法进行校验。如图7所示,首先将该8Byte数据排为1个矩阵的形式,每行为1B-yte。分别计算每行各bit的异或结果记为字节校验码(Byte-Wise),计算每列各bit的异或结果记为比特校验码(Bit-Wise)。接下来,将两个校验码分别按上述方法分割计算得到ECC校验码,并将字节校验码的ECC结果作为ECCe和ECCo的高有效位(MSB)、比特校验码的ECC结果做为低有效位(LSB)进行组合,最终得到8Byte数据包的ECC校验码。

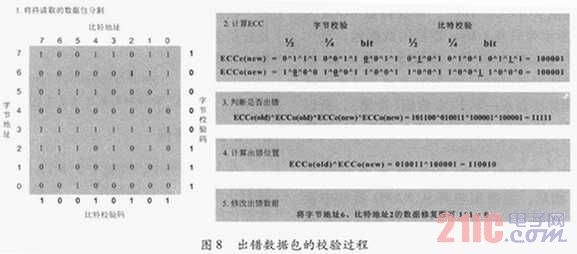

当数据包发生错误时,错误检测和更正所使用的方法与先前所描述的方法相似,这里仍以1bit错误来说明校验过程,具体如图8所示。

经步骤1~步骤4的计算,新的数据包存在错误且出错位置为“110010”,由于前面将字节校验码设为ECC值的高位,比特校验码设为低位,因此,“110010”的高有效位表示出错的字节地址,低有效位代表出错的比特地址,即字节地址为6、比特地址为2的数据发生了错误,与设定的错误情况相符。此时,只需将该位的数据比特与“1”异或即可完成数据包的修正。

将8Byte数据包扩展到512Byte数据包,虽然数据量大大增加,但仅添加了数据分割的情况,算法仍然一样。计算所得奇偶ECC数据均为12bit长,其中,3个低有效位代表bit地址(7~0),9个高有效位代表512Byte的地址(255~0)。

3实验分析

本实验处理对像为256Byte的数据包,对其进行ECC校验共生成22bit校验数据。为方便读取,可以在末尾添加两位,形成完整的3Byte校验数据。这3Byte共24bit,分成两部分:6bit的比特校验和16bit的字节校验,多余的两个比特置1并置于校验码的最低位,在进行异或操作时此两比特忽略。

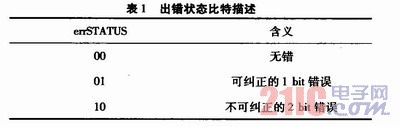

当往NANDFlash页中写人数据时,每256bit生成一个ECC校验,称之为原ECC校验和,并保存到页的OOB数据区中;当从NANDFlash中读取数据的时,每256bit又生成一个新ECC校验,称之为新的ECC校验和。校验时,将从OOB区中读出的原ECC校验和与新ECC校验和并执行按位异或操作,若计算结果为全“0”,则表示不存在出错,并将出错状态变量errSTATUS赋值为“00”;若结果为全“1”,表示出现1个比特错误,将errSTATUS赋值为"01”并进行纠正;除全“0”和全“1”外的其他情况将errSTATUS赋值为“10”表示出现了无法纠正的2bit错误,如表1所示。

实验仿真环境为AlteraQuartusII7.0,编程语言为VHDL。VHDL语言为硬件编程语言,具有并行处理的特点,而原程序中有大量的需要并行处理的异或操作,因此程序执行效率高,非常有利于硬件实现。

图9给出了数据包发生1bit错误的校验情况。其中,DATAin表示待读取的数据,HammingCALC表示在写入NANDFlash页时计算好的原始ECC,HAMMINGout表示后面在读取DATAin数据时计算的新的ECC,errSTATUS为出错状态,ERRIoc为计算所得出错的位置。为满足1bit错误的条件且易于观察,将256Byte数据(0~255)的最后一个Byte由“11110110”变为“11111110”,如图9中阴影部分所示。此时,errSTATUS结果为"01”,表明程序检测出了该1bit错误,且ERRloc输出为“111111111O11”,即出错位置为第255Byte的比特3发生了错误。为纠正该错误,此时,只要将该位置的比特取反输出即可。

在原来1bit错误的情况下,将其相邻的第254bit的数据由“11110101”变为“01110101”,如图10阴影部分所示,整个数据包有2bit发生了变化。此时,errSTATUS结果显示为“10”,即检测出了有2bit错误。但此时的ERRloe无效,不能表征出两个出错的位置,也就是为什么ECC校验只能检测出2bit错误而不能对其进行更正的原因。

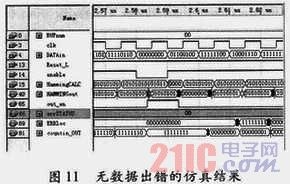

当然,如果数据包没有发生任何错误,也就是若读出的数据与先前写入的数据完全一致,ECC校验也是能够保证检测出来的。如图11所示,当未发生任何错误时,errSTATUS为“00”,验证了数据的一致性。此时,ERPloe无意义。

值得说明的是,如果数据包发生的错误多于2bit,该算法并不适宜。测定了更多比特(≥3)出错的情况,结果证明,errSTATUS的结果可能为“00”、“01”、“10”中的任何一个,也就是说在这种情况下,该算法很可能出现误检。因此,在这里,可以得出与ECC校验原理相符的结论:ECC能够保证纠正1bit错误和检测2bit错误,但对于1bit以上的错误无法纠正,对2bit以上的错误不保证能检测。

4结束语

本文将ECC校验算法通过硬件编程语言VHDL在AheraQuanusⅡ7.0开发环境下进行了后仿真测试,实现了NANDFlash的ECC校验功能。本程序可实现每256Byte数据生成3ByteECC校验数据,且通过与原始ECC数据对比,能够保证检测出1bit的错误及其出错位置,进一步结合对此错误的纠正,可应用于NANDFlash读写控制器的FPGA设计,实现对数据的ECC校验,确保数据准备有效地传输。经硬件实验结果反馈,该算法硬件适应性良好。

ECC是一种在NANDFlash处理中比较专用的校验,其原理简便、易于执行、计算速度快并且数据量越大,其算法越有效。但这样一个高效的算法仍存在缺陷,那就是其有限的纠错能力。本文也验证了其对于2bit以上错误是无效的,尽管这种情况在Flash中发生的几率很低,但就校验原理来说,是否存在一种改进的算法可用于多比特错误的纠正还有待进一步研究和验证。