PC104是一种专门为嵌入式控制而定义的工业控制总线,PC104与普通PC总线控制系统的主要区别是:

(1)小尺寸结构。

(2)堆栈式连接。

(3)轻松总线驱动。

PC104有2个版本,8位和16位,分别与PC和PC/AT相对应。PC104 PLUS则与PCI总线相对应。本文主要涉及的是PC104与DSP的16位数据通信接口设计,采用了CYPRESS公司的双端口静态读写存储器CY7C028V15AC作为共享存储器,双端口RAM右侧接ADI公司的DSP芯片T S101,左侧接PC104总线,控制逻辑用ALTERA公司ACEX系列CPLD中的EP1K100TC208来实现。

2双端口RAM访问模式

CY7C028V15AC是16 b×64 k的双端口RAM,支持高速的访问,访问速度为20 ns,支持左右2个端口完全异步访问。2个端口的选通信号有效,则双端口RAM两侧可以同时对双端口RAM进行读写操作。需要解决的是当同时访问到一个存贮块时的冲突问题。有2种方法可以解决访问冲突:一种是信号令牌传递方式,双端口RAM内部提供了8个Semaphore锁存单元,可以在逻辑上把双端口RAM划分为8个区段;当某个端口要访问某个区块时,首先向相应的锁存单元请求令牌,以确定访问是否会产生冲突,即向某一个锁存单元写“0”,然后读回所写数据,如果成功,则对应于该锁存单元的块是空闲的,可以访问,否则就不能访问。当一侧正在访问双端口RAM的某一块,则相应的锁存单元对另一侧是不能访问的。申请令牌通过读写I/O的方式实现,实际用到的是双端口RAM左右两侧数据总线的D0位,地址总线的A2~A0位(其译码对应于8个锁存单元),以及左右两侧对锁存单元访问的使能控制端SEML和SEMR。另一种方式是中断方式。在中断方式下,RAM最高的两个地址作为通讯邮箱,FFFEH分配给右端口,FFFFH分配给左端口。两个邮箱的使用方法一致。以右端口为例,当DSP向FFFEH地址写任意一个值时,左端口的中断请求信号INTL有效,当响应完中断请求后,PC104总线读一次FFFEH地址就可以INTL清除中断。

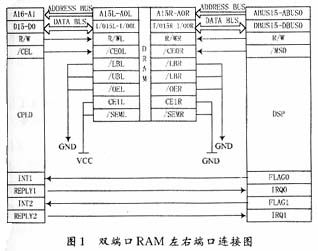

本文中采用中断方式设计PC104与DSP的握手信号。考虑到用CPLD来设计数字逻辑的灵活性和可重复编程,用CPLD来控制中断请求与响应信号,所以RAM最高端的两个地址仍作为普通的R AM单元使用。双端口RAM左右端口的连接如图1所示。

当DSP向PC104请求数据,TS101的标志位FLAG0通过CPLD的缓冲连接到PC104的其中一条中断信号引脚,当PC104收到中断请求向RAM写完数据,通过写I/O口的方式,由CPLD产生回复信号到TS101的IRQ0,TS101在适当的时间读取数据并进行算法处理。当TS101向PC104发送数据,则先向RAM中写数据,写完后由标志位FLAG1产生读数据请求信号,通过CPLD缓冲连接到PC10 4的另一条中断信号引脚,PC104响应中断读完数据,通过写I/O口的方式由CPLD产生回复信号到TS101的IRQ1。当PC104访问双端口RAM时。数据总线的16位通过CPLD缓冲连接到RAM左端口的I/O15L~I/O0L,因为16位的数据访问占用的是偶地址,所以地址总线的A16~A1在CPLD缓冲后连接到RAM的左端口的A15L~A0L地址线。PC104其余的地址线通过在CPLD里的译码产生RAM左端口的选通信号。当TS101访问RAM,TS101的前16根地址线连接到RAM的A15R~A0R,前16根数据线连接到RAM右端口的I/O15R~I/O0R,用产生选通信号,通过TS 101的编程实现,访问RAM的有效地址由用户定义。?

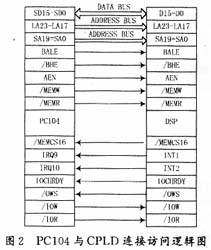

3PC104与CPLD的连接关系

通过CPLD,PC104要实现对双端口RAM的访问,首先要考虑的是分配给RAM的存储地址,因为64 k×16 b的RAM需要64 k的偶地址空间,或者说128 k的连续地址空间,工控机1 M以内可由用户使用的自由地址空间往往达不到128 k。所以应将RAM安排在1 M地址空间以外访问。此时除了用到用于1 M寻址的地址线SA19~SA0,还要采用1 M外寻址的地址线LA23~LA17。需要注意的是,PC104的总线上的SA19~SA17与LA19~LA17是重复的。区别在于SA10~SA0是通过总线地址锁存使能信号BALE锁存输出,而LA19~LA17未经锁存,为保证在对RAM访问期内地址信号一直有效,至少应在CPLD内将LA23~LA20进行BALE锁存。本文中将RAM的地址安排在1 M地址空间外从100000 H开始的64 K偶地址。所有需要用到的PC104信号线都连接到CPLD,CPLD将SA16~SA1缓冲连接到RAM,其余地址线译码产生RAM左端口选通信号。PC104与CPLD连接的访问逻辑如图2所示。

其中有效表示数据总线的高8位有效,SA0有效表示数据总线的低8位有效,作为译码信号的一部分,对于单片16位数据线的集成电路,实际上也可以不连接,用SA0和高端地址线译码产生选片信号。AEN信号有效表示计算机在和某个设备进行DMA传送,其他的设备发现AEN信号有效,就不要响应寻址信号。因此在CPLD内部逻辑里设置当AEN信号有效时,将进入CPLD的地址信号线置为高阻态。

![]()

是存储器读写信号,是用于1 M以外地址空间的读写信号,当这两个信号之一有效且寻址到1 M内的地址,将分别使1 M以内地址的读写

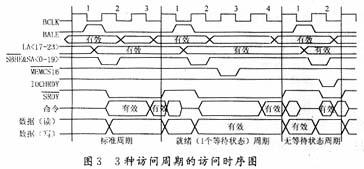

一起控制总线周期的长短。有3种存储器访问周期:标准周期,就绪周期,无等待状态周期。访问时序如图3所示。

在设计的时候考虑到信号在CPLD里的延时,如果标准周期对于访问的时间长度不够,可以采 用有1个等待状态的就绪周期,而这只需要修改CPLD的设计并重新下载到CPLD即可,由此可 见用CPLD作为控制芯片的优点。

4结语

本文说明的这种PC104总线与DSP的数据通讯接口设计,也可以作为采用其他计算机总线与DS P进行16位数据通讯接口设计的参考。