引言

随机数发生器是信息安全领域不可或缺的重要组成部分,广泛应用于金融、军事等信息安全保密通信的电子设备中。目前,随着对RNG体积、功耗、接口方式等要求的提高,设计集成化芯片或IP核形式的随机数发生器成为一种必然。为此,基于纯数字电路实现的随机数发生器已成为研究的热点,而FPGA可编程逻辑芯片为此类随机数发生器的研究提供了良好的开发环境。

为方便随机数发生器IP核的下载、运行及测试,同时保证产生的随机数能够快速地传送给主机进行随机性检测,本文以FPGA芯片为核心,以USB接口为通信接口,设计实现了一个随机数发生器的验证平台。该平台结构简单,功能完善,对于其他特殊应用的验证平台搭建也具有指导意义。

1 系统硬件结构及工作原理

随机数发生器验证平台主要由CycloneII FPGA芯片EP2C20Q240C8N、与主机进行通信的USB收发器电路、下载配置芯片EPCS4、频率为48 MHz的时钟源芯片、外部存储器(Flash)、两个电压转换电路、复位电路和其他电路组成,如图1所示。

在每次实验演示时,将该芯片通过USB口与PC机相连,由主机为平台提供5 V电源,当与主机连通后系统上电,复位电路进行工作,对整个系统进行复位。以QuartusII 7.2为开发环境,采用ByterBlsterII下载电缆,通过JTAG下载口或以AS下载方式,通过配置芯片EPCS4将随机数发生器系统下载到实验平台中,最终通过USB口连接主机与平台进行信息交互。由主机向系统发送命令,在系统控制下,产生的随机数通过USB收发器传送给主机,主机接收数据后进行随机性的各项检测。

2 核心器件和关键技术

2.1 FPGA芯片EP2C20Q240C8N

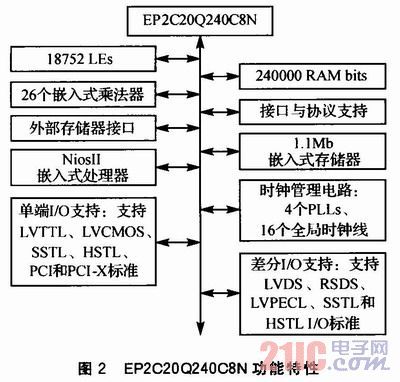

EP2C20Q240C8N芯片是A1tera CyeloneII系列产品中的一员,它采用TSMC1.2 V、90 nm和低电介绝缘工艺技术,由12英寸(300 mm)晶圆制成,具有潜在速度方面的极大优势。

该芯片提供了许多功能特性,如图2所示。该芯片资源丰富,可为随机数生成系统提供良好的实验环境。随机数生成系统主要由OC8051IP核、随机数发生器IP核及USB控制器组成,实现了USB接口与随机数生成系统的连接,保证了主机与平台的信息交互。

2.2 PDIUSBP11A收发器芯片

PDIUSBP11A USB收发器是Philips公司推出的,设计用来与USB物理层进行交互,来自串行接口引擎(SIE)的VPO和VMO作为主驱动器的输出。串行接口引擎和USB收发器的共同作用允许USB专用集成电路设计者设计灵活的USB设备,与更多可用逻辑元件相兼容。其主要特性包括:

①符合USB1.1协议规范;

②利用数字信号的输入与输出来传送和接收USB串行数据;

③支持全速(12 Mb/s)和低速(1.5 Mb/s)的串行数据传输;

④支持单端口数据界面;

⑤单一的3.3 V电源;

⑥允许USB专用集成电路与USB的物理层进行交互;

⑦有SO-114、SSOP-14和TSSOP-14封装。

3 设计方案实现

3.1 系统供电电路

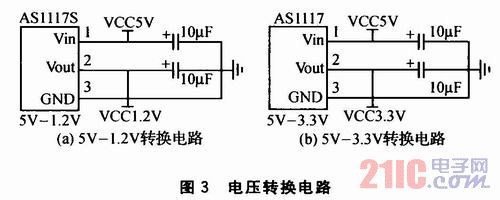

本系统没有设置专门的电源电路,而是通过USB接口由主机提供5 V电源。由于系统内部工作电压为3.3 V和1.2 V,为此,专门设计了两个电压转换电路,将USB接口的5 V电压转换成3.3 V和1.2 V后再提供给系统,保证系统正常工作。电压转换电路采用封装为SOT-223的AS1117和AS1117S芯片,主要电路原理图如图3所示。

为保证输出电压的稳定性,在电压输入端和输出端都接有10μF的输出电容。

3.2 USB收发器电路

PDIUSBP11A芯片拥有14个可用引脚,其电路原理图如图4所示。

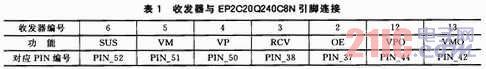

在本设计电路中,将PDIUSBP11A芯片的引脚1和引脚8悬空;引脚7和引脚14分别接地和3.3 V电压;差分数据信号D+和D-引脚分别经一个阻值为24 Ω的电阻与USB接口的D+和D-相连,同时D+经上拉电阻与3.3 V电压相连;引脚9经上拉电阻与3.3 V电压相连,使USB保持在全速工作模式下;其他引脚与FPGA芯片相应的引脚相连接,具体连接方式如表1所列。

3.3 配置芯片及下载电路

Altera编程硬件主要包括MasterBlaster、ByteBlasterMV、ByterBlsterII、USB-Blaster和Ethernet Blaster下载电缆或Altera编程单元(APU)。

本文采用ByterBlsterII下载电缆,选用EPCS4配置芯片,设计实现了AS主动串行配置模式与JTAG下载模式相混合的下载配置电路。

本设计采用AS和JTAG两种下载方式,可以通过JTAG方式对程序进行调试,同时通过QuartuslI软件提供的一个可在线操作FPGA片上RAM内容的工具InSystem Memory Content Editor,用户可以查看和修改RAM的内容。用户可以预期对RAM中的内容进行修改,并通过该工具查看修改后的结果,两者进行对比就可验证程序运行是否正确。此外,在JTAG模式下可以利用jic文件验证配置芯片是否已经损坏。

3.4 复位电路

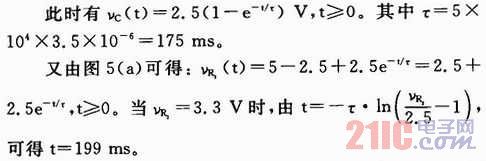

为使验证系统初始化正确,当整个系统在电源上电时,必须处于复位状态。一般应保持复位脉冲为高保持两个机器周期以上,而系统晶体振荡器达到稳定一般需要150 ms左右。为此,本文设计了基于RC器件的复位电路,如图5所示。

其中,R1=R2=100 kΩ,C1=3.5μF,对于虚线中的电路,运用戴维南定理把系统上电后电路中除电容支路以外的部分进行化简,得到的电路如图5(b)所示。

由此可得,该复位电路能够正常复位,保证系统正常工作。

3.5 时钟电路

时钟由晶振芯片提供,晶振芯片有无源晶振和有源晶振两种。无源晶振为无极性元件,共有2个引脚,只有在时钟电路工作控制下才能产生振荡信号;有源晶振由石英晶体组成,此外还有晶体管和阻容元件,信号稳定,它共有4个引脚,常用的连接方式为:1脚悬空,2脚接地,3脚输出,4脚接电压。本设计采用ELV型号为SMD5*7的48MHz晶振。

3.6 存储器模块

为满足特殊功能需求,扩展了1 Mb的Flash。Flash选用Spansion公司的CMOS多功能器件,型号为AM29LV010B,采用32引脚的标准TSOP封装,工作电压为3 V,8位数据宽度。数据总线使用D0~D7,地址总线使用A0~A16,其他还有芯片使能信号CE,输出使能信号0E和写使能信号WE。它与FPGA芯片引脚的具体连接方式如表2所列。

3.7 其他电路

为保证系统中各个芯片能够正常工作,本设计在各电压源都并联有0.1μF的退耦电容,并将这些电容摆放在芯片的周围,滤除高频杂波。

4 测试与验证

各模块电路设计完成后,经Altium Designer09仿真验证,完成了相应的PCB版图设计,并最终进行电路版图的印刷和元器件焊接,实现了整个验证平台。

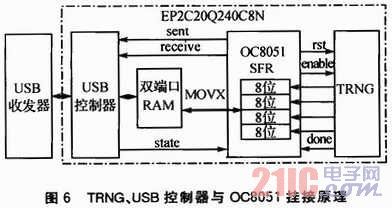

为检验平台工作的正确性,本文对参考文献中的随机数发生器利用VHDL语言进行了实现,并在输出模块中增加了一个32位的移位寄存器,每产生32位随机数进行一次输出。最后,将该随机数发生器及参考文献中所设计的USB控制器与参考文献中所提供的OC8051 IP核进行挂载连接,其挂接原理图如图6所示。

挂接完成后,利用QuartusII软件,将整个系统以AS下载方式,通过配置芯片EPCS4下载到FPGA板中。由OC8051 IP核控制随机数发生器模块进行工作,每产生32位随机数时,TRNG向OC8051发送一个done信号,OC8051接收32位数据,并将其分为4个8位存于4个特殊功能寄存器(Sp-ecial Function Register,SFR)中,并通过指令MOVX借助累加器将32位数据转移至双端口RAM中。之后进行下一32位随机数的产生及传送,直到运行16次后,RAM中所存储的随机数为512位时,OC8051置sent信号有效,USB控制器将512位随机数封装成数据包,通过USB收发器传送给主机,传送完成后向OC8051返回一个state信号,表明传送结束。重复上述过程即可源源不断地将产生的随机数传送给主机,由主机最终完成随机数检测,检测结果表明所接收到的数据满足随机数特性。

在随机数生成系统下载、随机数生成及随机数传送过程中,整个平台工作正常,表明各模块电路原理及连接的正确性:

①电压转换电路连接正确,能为系统提供稳定电压,同时表明,退耦电容起到了很好的去噪作用;

②下载电路连接正确,能够将程序正确下载到FPGA中;

③复位电路工作正常,时钟电路能给系统提供稳定的时钟;

④USB收发器电路连接正确,能正常收发数据。

由此表明,该验证平台具有一定的可靠性和稳定性,能为随机数发生器提供一个良好的验证环境。

结语

本文结合实际需求,在充分理解FPGA结构原理和元件特性的基础上,设计实现了一个小型的FPGA开发板。它不仅可以作为随机数发生器的验证平台,同时也可为其他基于数字电路实现的系统提供服务。本文所设计的开发板结构比较简单,故难以满足大型数字电路开发系统的要求,为此,下一步的工作是扩展功能模块,设计更多的外围扩展电路,满足更高的实验需求。