通用工业视频图像叠加的设计与实现

2009-04-16

作者:茹海燕 顾子天

摘 要: 介绍了在工业现场控制中,一种视频图像叠加系统的设计与实现,详细介绍其硬件原理和软件组成,并对该系统的进一步扩充提出了一些措施和方案。

关键词: 图像处理技术 视频信号 同步信号 像素

图像处理技术广泛应用于科学研究、工农业生产、军事技术、医疗卫生等领域。在工业上的应用主要有:机器人视觉的研制、生产过程自动化、产品质量检测、机器零件的无损探伤、人工地震信号处理及地层内部结构的重建等等。本文介绍的项目是为实现生产过程自动化,叠加工业现场视频图像中多种起标识作用的图形,简化以后的数字化处理过程;并且可以通过人机交互,由用户通过按键选择所要叠加的图形。目前市场上有能完成其中部分功能的芯片,但是它们价格太高;而且,这些芯片应用面窄,可扩充性差,不能满足客户的特殊要求。本文作者设计并实现了一种成本低、应用灵活可靠,易于扩充、实用性强的图像叠加方案。

1 图像叠加的原理及总体设计

为实现图像叠加,必须先了解图像传送的原理。图像是由明暗不同的部分构成的,一幅图像可以分解成许多个基本单元,叫“像素”。显然,像素的数目越多,就越能呈现出图像的细节,因而画面就越清晰。要想成功地传送一幅图像,必须把它所有的像素分别转换成相应的电信号,再一一加以传送。现代电视技术中,采用顺序(轮流)传送像素的方法,在发送端按照各个像素的行列位置逐个变成电信号,发送到接收端;在接收端屏幕上,各个像素当然也是一个一个地轮流出现的。因此,要想在接收端的屏幕上得出正确的影象,应该符合两个条件:首先是发送与接收两个端的扫描时间应该相等,即扫描频率一致;另外,每一行和每一场开始扫描的时刻也要一样,即扫描的相位一致。所以,严格地保证接收端和发送端的扫描运动互相同步是非常重要的。目前在传送视频信号时,把影象信号、消隐信号和复合同步信号三者按一定比例混合在一起,发送到接收端去控制显象管中电子束的扫描运动,以保证影象中各像素的位置在荧光屏上正确重显。我国采用的电视信号是PAL制,场扫描频率为50Hz,行扫描频率为15625Hz,它的行同步信号和场同步信号的基本波形如图1所示。实际传送的视频信号波形如图2所示,在接收端可以利用这三种信号的幅值不同,用幅度分离将它们彼此分开。“消隐信号”是为了在行扫描逆程或帧扫描逆程期间,摄象管和显象管的电子束被截止而设的信号。“复合同步信号”可控制扫描振荡器的工作频率和相位,它由“水平同步信号”和“垂直同步信号”组合而成,二者的频率不同,在接收端用频率分离电路(或称波形分离电路)将它们彼此分开。

本项目中,要求对摄象头获得的图像,叠加上几种不同形状的光标,如十字形、圆形、方形、六边形等;用户可以通过键盘对这些光标的形状和大小进行选择。按此要求,我们在图像传送过程中,截取从摄象头传出的视频信号,叠加一些图形信号,再传送到接收端(本项目中为监视器)。所谓叠加,实质上是在像素级,为每个像素点选择电信号。这其中有两个问题,一是精确定位像素点,即确定它的行、列位置;二是定位之后,控制电信号的输出,即选择在监视器上的某一像素点,是显示现场图像像素的电信号,还是叠加图形的像素电信号。解决第一个问题的难点在于信号同步,即从视频信号中提取行同步信号及场同步信号,来控制行/场计数器准确计数,以定位像素点。解决第二个问题在于设置“二选一开关”控制电信号输出。另外,为实现人机交互,实时动态地控制所叠加图形的变换,如改变光标的形状、大小,需要对屏幕编辑缓冲区RAM进行刷新。为避免输出不完整或不稳定的图像,在刷新过程中,维持原屏幕上的图像不变,直至刷新结束。那么如何设置RAM的读写控制信号来实现这一要求,是第三个难点。

经过上述分析和市场调查,选用Intel的单片机90C32(它与8032的引脚和功能完全一致)作为CPU,可以充分发挥它的灵活性,并且利用其成熟的典型扩展电路来减少开发的难度和成本。在设计中,同步信号的提取、叠加选择的控制、屏幕编辑缓冲区的读写控制,以及键盘译码均用硬件实现,使系统快速、稳定、可靠运行。为减少时延,扩展电路全部采用高速CMOS芯片实现。在此功能较完善的硬件基础上,软件设计简单多了,主要完成系统初始化的按键响应。

2 硬件设计

硬件设计的总体框图如图3所示。

下面分别详细介绍各个主要部分的电路。

2.1 同步信号的提取及行/场计数器电路

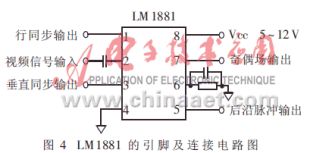

准确提取视频信号中的同步信号对于本项目的成攻至关重要,幸运的是市场上提供了LM1881芯片,它仅需几个外接元件,就可以可靠地提取出视频信号中的同步信号。LM1881的引脚及连接电路如图4所示,图中的电容值均为0.1μF,电阻阻值为680kΩ。

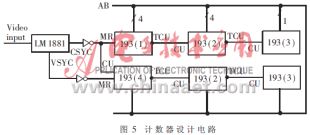

行/场计数器由193芯片级联而成。按PAL制式规定,场扫描频率为50Hz,帧频25Hz,总扫描线数625,由于分为奇偶场扫描,每场有312行,需用二进制地址9位。选择4MHz的晶振行为行计数器的计数脉冲输入,那么每行有256个像素点,计算公式为:![]() 。每片193有四位输入、输出端,输入端均接“0”,输出端组成地址总线。为保持行、场计数器电路的整齐,并保留一定的扩充性,行、场计数器各设3片193芯片实现。计数器电路如图5所示。

。每片193有四位输入、输出端,输入端均接“0”,输出端组成地址总线。为保持行、场计数器电路的整齐,并保留一定的扩充性,行、场计数器各设3片193芯片实现。计数器电路如图5所示。

行同步信号经过一级非门,送往行计数器三片193的清零端MR;同时作为场计数器的计数脉冲,送往场计数器最低级193的计数脉冲输入端CU;而行计数器各级之间的级联由低级193芯片的TCU端送往更高一级193芯片的CU端;图中未画出的行计数器的计数脉冲输入端CU由晶振信号送入。场同步信号经过一级非门,送往场计数器三片193的清零端MR;场计数器各芯片之间的级联方式同行计数器相同。计数器产生的18位地址,经过总线锁存器,高15位送往屏幕编程缓冲区RAM,最低3位送往叠加控制的并串转换电路。

2.2 图像叠加及控制电路

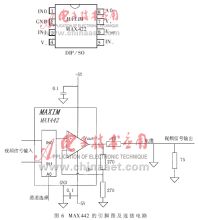

参与叠加的信号有两路:现场视频信号、叠加图形信号。由于只要求完成对摄象头获取的图像的叠加,并在监视器上重显图像,叠加信号可以为黑电平和白电平。而视觉效果上黑电平更明显,所以我们选择叠加黑电平。这个“二选一”开关可用美国MAXIM公司生产的MAX442来实现。MAX442芯片是内含放大器的视频两路开关,它具有140MHz的单位增益带宽,250V/μs的转换速率;相位误差小于0.09°,增益误差小于0.07%;通道切换速率为36ns,可以直接驱动50Ω或75Ω的同轴电缆。虽然它价格相对较贵,但考虑到选用它之后,系统的性能可以得到较大幅度的改善,而且本项目的总体成本仍然很低,即性能价格比合理,所以选择这种芯片。

MAX442的引脚图与连接电路如图6所示,图中的电容容值单位为μF,电阻单位为Ω。IN0,IN1为两路视频信号的输入端,分别外接现场视频信号和黑电平;地址线A0控制“二选一”开关,选择输出哪个通道的信号。A0在屏幕编辑缓冲区中仅占一位空间,所以叠加控制字可以按位读写修改,这大大减少了所需的屏幕编辑缓冲区RAM的存储空间。在RAM中数据是按照字节存取的,因此在输出时,需要把从RAM中读出的数据进行并串转换,送到MAX442的A0端。这种“八选一”的数字逻辑电路用可编程芯片GAL可以很方便地实现,成本也不高,因此我们选择用GAL实现,逻辑表达式从略。

2.3 屏幕编辑缓冲区的控制设计

屏幕编辑缓冲区选择用RAM,是因为用户要求叠加的均是规则的几何图形,由CPU 90C32动态计算图形各点的位置算法非常简单;用户完全可以接受。

CPU和视频输出端都要对屏幕编辑缓冲区进行访问,其中CPU要完成对RAM的刷新,即“写”RAM;输出端仅需读RAM。也就是说,对RAM的访问可以定为“写时禁止读”,“读时禁止写”。让它们共用数据总线DB和地址总线AB,而通过控制CPU和行场计数器的地址锁存器的使能端E,来分时使用。可见,这两组地址锁存缓冲器的使能端E是互斥的,可以仅用90C32的一根PI端口I/O线来作一个“单刀双掷开关”,由CPU通过控制这根I/O线来实现总线的分时使用。所以在电路设计中,RAM的片选端CS直接接地,写使能端WR与CPU的WR相连,而读使能端OE与行/场计数器的地址锁存器的使能端E相连。当CPU要对屏幕编辑缓冲区写时,选通它的地址锁存器的使能端E,同时行场计数器的地址锁存器被禁止,RAM的读使能端也被禁止,即RAM处于“只写”状态。反之,当CPU不需要对RAM刷新时,选通行/场计数器的地址锁存器的使能端E,同时RAM的读使能也被选通,RAM处于“读”状态,并且禁止写操作。用这种“存储器双总线技术”,避免了对屏幕编辑缓冲区的冲突访问,从而保证数据的完整性,得到稳定、正确的叠加视频图像。

CPU 90C32的典型扩展电路包括程序存储区的扩展、数据存储区的扩展、时钟电路和晶振电路的扩展。考虑到项目需求并保留一定的扩充余地,存储器ROM选用27256芯片,RAM选用61256芯片。其中除RAM(屏幕编辑缓冲区)为临界区,需要特殊设计以外,其它电路与通用的单片机扩展电路完全相同,在此不另做介绍。

2.4 按键译码电路

本项目中,用户在人机交互选择叠加光标的形状与大小时,仅需要四个按键,因此不必使用功能强大的8279芯片,直接扩展90C32即可。四个按键经过译码,送到90C32的P1端口,这个译码逻辑非常简单,同样用GAL实现,逻辑表达式从略。在实际使用中,用户选择一次光标的大小与形状之后,总会稳定一段时间去进行其主要工作,所以操作按键的时间对于整个系统的工作时间而言是很短的。CPU对按键的响应采用中断方式,这可以比轮询方式大大减少对CPU处理器资源的占用。在按键电路中,一共占用P1端口2根I/O线,A0、A1是译码后的按键地址(或代码);另有INT是检测是否有按键被按下的中断信号线,它与90C32的外接中断输入端P3.2 相连接。通常INT为高电平,若有按键被按下,INT为低电平,CPU可响应中断。

相连接。通常INT为高电平,若有按键被按下,INT为低电平,CPU可响应中断。

按键电路的设计,也选择简单、典型而可靠的通用电路实现。目前,按键是利用机械触点的合与断来作用的,当电信号通过按键时,在闭合及断开的瞬间均有抖动过程,会出现一系列的负脉冲,持续时间一般为5~10ms。按键的稳定闭合期,由操作人员的按键动作所决定,一般为十分之几秒至几秒时间。为了保证CPU对按键的一次闭合,仅做一次键输入处理,必须去除抖动影响。通常去抖影响的措施有硬、软件两种,本项目用两重 去抖来提高可靠性:硬件设计中,为每个按键在输入端加一个一端接地的电容,滤去毛刺脉冲;软件设计中,有按键去抖过程,具体思想在软件设计中详细讲述。

3 软件实现

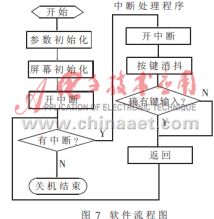

由于本项目中的难点工作均用硬件实现,所以大大减少了软件设计工作量。软件主要实现系统初始化和中断处理过程,其流程图如图7所示。

主要过程的设计思想如下所述。

3.1 系统初始化

初始化参数,如代表光标大小的RDS、代表光标形状的SHAPE等等;

初始化监视器的屏幕:清零屏幕编辑缓冲区、叠加十字光标和圆形光标;

开中断,使CPU处于可接收外部中断信号的状态。

3.2 中断处理过程

首先打开在CPU响应中断时关闭的中断,然后调用按键去抖过程,确认有合法按键输入后取出按键代码,刷新屏幕编辑缓冲区,并调用按键响应过程。

3.3 按键响应过程

四个子程序分别对应于四个按键的功能:

KEY0:将现在屏幕上的光标尺寸放大一个单位;

KEY1:将现在屏幕上的光标尺寸缩小一个单位;

KEY2:改变现在屏幕上的光标形状,依次重复按此键,光标的形状依次变为圆形、方形、六边形;

KEY3:同时叠加所有不同大小的圆形光标,这是考虑到在实际应用中,圆形光标的使用频率较其它形状更高而特设的。

3.4 按键去抖过程

在检测到有且仅有一个键被按下时,记录此时闭合的按键的代码,然后执行一个延时过程,如延时10ms;之后,再判断是否仍有按键闭合。若有,检测它的代码与方才记录的代码是否一致,只有二者一致时,才认为确实有按键闭合,进行按键响应处理。

此项目已投入实际生产,运行结果令研制人员和客户满意,认为它:a)原理简单,功能齐全,性能可靠,成本低廉;b)可扩充性强,只需作少许改动,即可适应用户的更高要求:

(1)若要求进一步提高图像叠加的精确度,可选择更高频的晶振作为行计数器的输入脉冲,必要时对行计数器电路加以扩展;同时在软件的地址处理上略加改动即可。这相当于将像素点细化,因而叠加后的图像清晰度更高。

(2)若要求对叠加的图形加以扩充或改动,可对相应的软件“按键处理过程”做调整。若需要增加按键的数目,还要对硬件中的按键译码电路进行扩展。由于在硬件设计中已考虑到未来的扩展,目前的设计仅需作很少改动,并且可最大限度地减少占用CPU90C32的端口线。如4个按键需要3根I/O线,即2线地址线,1根中断检测线;若扩展为8个按键,只需增加1根地址线,并重写译码GAL的逻辑即可。以此类推,若扩展N个按键,需要n根I/O线,其中,

n=[logN]+1

但是,由于GAL芯片本身结构的限制,建议在按键超过8个时,选用8279扩展键盘,以更好地满足用户要求。

(3)若要求能叠加更多类的信号,如增加要求“可选择叠加黑电平或白电平”,可对硬件设计的叠加电路及其控制部分加以修改。MAXIM公司提供的芯片MAX441是4信道视频多路开关,MAX440是8信道视频多路开关,它们的单位增益带宽更高,其他主要参数与MAX442基本一致。详细介绍请查阅《MAXIM DATABOOK1998》。

(4)若要对视频信号进行其它加工、处理,也可由本文所述的原理与实现得到参考和启发。

参考文献

1 何立民编著.MCS-51系列单片机应用系统设计——系统配置与接口技术.北京:北京航空航天大学出版社,1998

2 薛钧义编.MCS-51/98系列单片机微型计算机及其应用.西安交通大学出版社,1996

3 赵荣椿编.数字图像处理导论.西安:西北工业大学出版社,1995

4 MAXIM.DATABOOK 1998.MAXIM,1998

5 政武编著.家庭影院系统的原理与配置.北京:电子工业出版社,1997

6 中央广播事业局电视服务部编.电视机的原理与维修.北京:科学出版社,1980