引言

模拟示波器由于无法高效地观察实验结果、数据处理功能弱等缺点,已逐渐被数字示波器所取代,但数字示波器价格昂贵。虚拟仪器是在通用计算机平台上,用户利用软件根据自已的需求定义设计仪器的测量功能,其可以大大拓展传统仪器的功能,降低仪器成本,并可通过软件实现数据的复杂分析、运算和海量存储等功能。LabWindows/CVI是1种常用的虚拟仪器设计软件,为用户提供了功能强大的虚拟仪器系统开发平台。为此,本文以LabWindows/CVI为开发平台,利用FPGA中嵌入的NiosⅡ软核构成的SOPC系统,设计一种双通道虚拟示波器,以达到一般传统示波器的性能指标。

1 虚拟示波器硬件电路设计

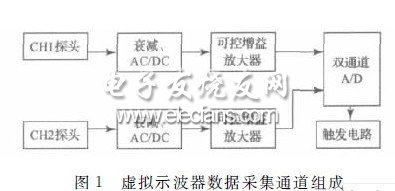

1.1 虚拟示波器数据采集通道电路设计

为减少虚拟示波器对被测电路的影响,要求虚拟示波器数据采集通道的输入阻抗在1MΩ以上,因此必须设计合适的衰减器和可控增益的放大器。虚拟示波器数据采集通道的原理方框图如图1所示。图1中,虚拟示波器的2个通道完全对称,且相互独立。从探头进来的信号经过衰减网络,获得合适的信号强度,进行AD/DC切换开关后,送到可控增益放大器,将不同幅度的信号放大为幅度大致相同的信号,经高速A/D转换获得两路独立的数字信号,同时触发电路完成触发功能,使波形能够平稳地显示。

1.1.1 衰减与AD/DC转换电路

图2为虚拟示波器的衰减与AD/DC转换电路图。

图2中,R1、R2、R3、C1 和R4、C2组成1:10的分压网络,通过CPU控制三极管Q1、Q2 和继电器K1、K2 分别控制进行1/10的衰减与AD/DC切换控制。

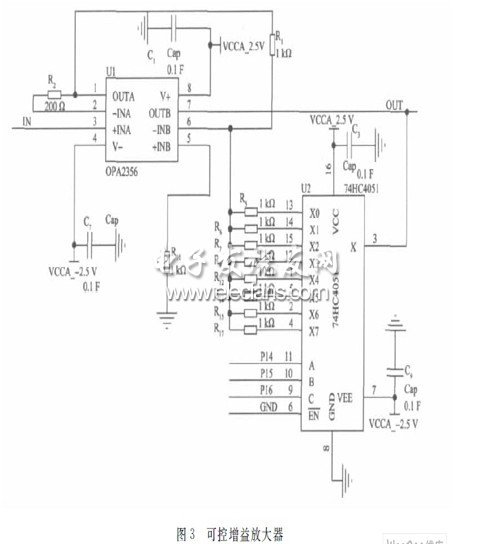

1.1.2 可控增益放大器

虚拟示波器需设计宽范围可调节的增益放大电路器,以实现10mV~±200V范围内的输入电压采样。本系统采用模拟多路器切换运放的反馈电阻,以达到改变增益的目的,其电路图如图3所示。

图3中,U1内部包含两通道JFET高输入阻抗的运放,前级为跟随器,以满足示波器的高输入阻抗要求,第2级为可控增益放大器,由模拟多路器和运放共同构成。

1.1.3 A/D转换电路

虚拟示波器的A/D 转换器采用Linear 公司的LTC2289,它的采样频率可达80MHz,有2个独立通道,可选内部参考或外部参考。本文选用内部参考。

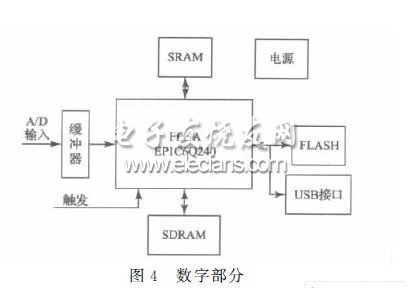

1.2 虚拟示波器信息处理部分硬件设计

虚拟示波器信息处理部分主要包括FPGA 系统和USB通信部分,其组成方框图如图4所示。

图4中,虚拟示波器模拟输入通道的模拟信号经A/D转换后获得数字信号,经过1个数据缓冲器输入到FPGA,FPGA通过逻辑电路和NiosⅡ管理将数据进行存储、上传等。SRAM用于缓存采样数据;FLASH用于存储NiosⅡ应用程序,并实现系统上电时将程序加载至SDRAM中。

系统选择的USB接口芯片CY7C68001为USB2.0标准控制器,其可工作在高速或全速状态,支持4个可配置共享4KB FIFO空间的端点,并具有一个标准8位或16位主机接口,非常适合做高速USB接口。虚拟示波器SOPC系统构建及NiosⅡ软件开发#e#

2 虚拟示波器SOPC系统构建及NiosⅡ软件开发

2.1 虚拟示波器SOPC系统构建

本文采用ALTERA公司的NiosⅡ软核处理器,并利用FPGA设计虚拟示波器系统。ALTERA 公司的NiosⅡ软核处理器是一个32位RISC嵌入式处理器,具有5级流水线、采用数据和指令分离的Harvard结构、提供众多标准外设和软件集成开发环境。

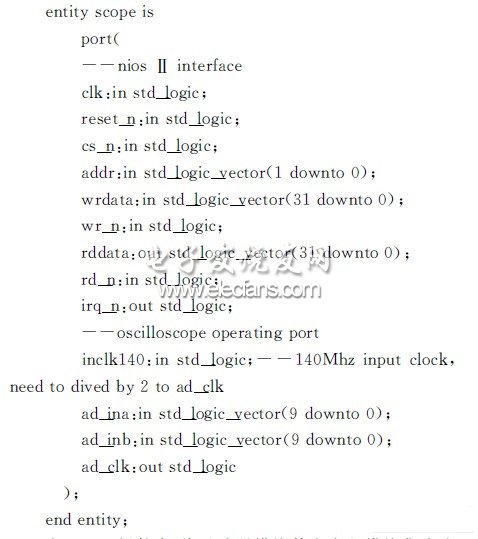

进行基于Nios Ⅱ 的SOPC 系统开发时,可利用ALTERA提供的SOPC插件,进行外设和CPU的配置,并提供自定义IP的构建方法。在虚拟示波器系统中,需要开发符合AVALON总线的示波器模块,并加入到自定义IP中。示波器模块实体程序如下:

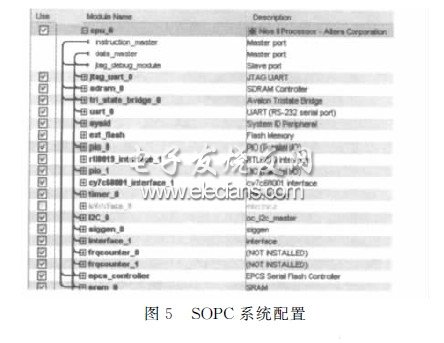

在SOPC插件中,将示波器模块等自定义模块集成为IP核,分别将NiosⅡJTAG_UART、FLASH以及SRAM等IP核加入虚拟示波器系统中,SOPC系统配置图如图5所示。

配置完成后,生成系统,并在QuartusⅡ中进行引脚配置,然后综合、布线,生成配置文件,通过JTAG 对FPGA进行配置,即可获得虚拟示波器系统的信息处理部分硬件电路。

2.2 NiosⅡ软件开发

实践证明,当系统的复杂程度达到一定时,采用嵌入式操作系统不仅会简化程序员工作、提高CPU利用率,而且会提高系统可靠性。因此本系统的下位机软件采用嵌入式操作系统。microc/os-Ⅱ是1个性能优良的嵌入式多任务实时操作系统,稳定度高、安全性好;同时NiosⅡ开发环境中集成了性能良好的、免费的microc/os-Ⅱ估算版,因此虚拟示波器系统采用该操作系统。

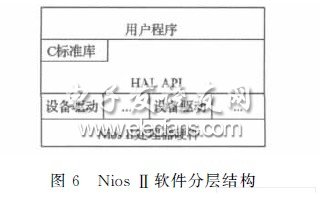

NiosⅡ的软件开发一般采用分层的方式进行,它采用类似Linux的设备文件系统来管理设备,采用HAL(硬件抽象层)完成硬件相关设备的封装操作,因此每个CPU外设都需要有相应的驱动程序。虚拟示波器系统中,NiosⅡ的驱动分层结构如图6所示。

虚拟示波器系统需要为定义的IP设计相应的驱动程序,对于最底层与硬件相关的操作,NiosⅡ提供了IOWR(base,offerset,data)和IORD(base,offerset)2个宏,分别用于对寄存器的读、写操作。这里,base为虚拟示波器驱动程序的基地址,其自动生成;offerset为指被操作的寄存器在该设备中的偏移地址。

2.3 嵌入式USB协议栈开发

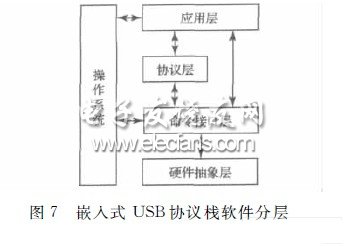

USB协议复杂,虚拟示波器系统开发的USB协议栈基于microc/os-Ⅱ,并采用了如图7的分层结构,以减少开发调试的难度。

硬件抽象层和命令接口层都与硬件相关,硬件抽象层负责对SX2的寄存器进行读写操作,而命令接口则实现与SX2的工作方式有关的操作;协议层与平台无关,其主要完成USB的枚举及各端口数据处理;应用层完成对提供调用的函数进行封装,应用层提供了简单的API接口,其利用senddata函数发送数据到主机,同时利用recdata函数从主机接收数据以及厂商请求的函数,上层程序只要简单地调试这3个函数而无需关注USB协议,即可完成虚拟示波器的USB通信。3 虚拟示波器上位机软件设计

3.1 虚拟示波器USB通信的封装

虚拟示波器上位机程序采用LabWindows/CVI开发,其本身并不支持USB通信,因此采用了调用外部模块的方法。采用VC++编写程序,将USB通信底层函数进行封装,编译成DLL,再供LabWindows/CVI进行调用。为此,将动态链接库的头文件和DLL文件导入进工程,生成1个FP的驱动器,这时虚拟示波器系统就可以直接调用DLL里面提供的函数。

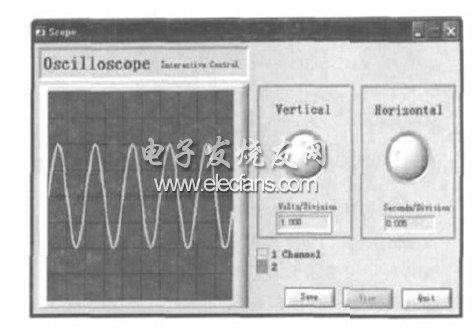

3.3 虚拟示波器面板程序的开发

图8中,用户对虚拟示波器面板上的垂直幅度调节、水平宽度调节等按钮操作时,系统会将相应的操作命令传送给下位机,并由下位机调节垂直幅度和水平时基等,从而实现用户对虚拟示波器系统的操作。

4 测试结果

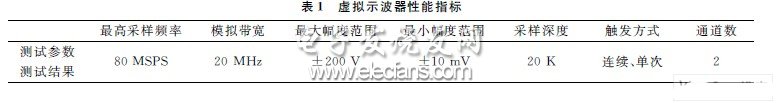

采用FPGA处理器和ALTERA公司的NiosⅡ软核完成虚拟示波器系统设计后,进行了多次测试,其性能指标如表1所示。

由表1可知,该虚拟示波器达到了一般模拟示波器的指标。然而由于本系统采用虚拟仪器技术,在功能上增加单次采样、波形保存等功能,因此与普通示波器相比,其成本低廉,操作界面更友好、简便。

5 结论

本文以LabWindows/CVI为开发平台,设计了1种双通道虚拟示波器,该示波器利用FPGA 中嵌入的NiosⅡ软核构成的SOPC系统,完成虚拟示波器各模块的管理;利用嵌入式USB协议,配合片外的模拟信号处理模块,通过USB总线,完成各种波形数据的采集,经上位机软件完成了波形显示和数据分析,并实现了仪器的各种操作功能。实际测试结果表明,该虚拟示波器达到了或优于一般模拟示波器的性能指标。