直接数字频率合成技术(Direct Digital Synthesize,DDS)是继直接频率合成技术和锁相式频率合成技术之后的第三代频率合成技术。它采用全数字技术,并从相位角度出发进行频率合成。随着微电子技术和数字集成电路的飞速发展,以及电子工程领域的实际需要,DDS日益显露出优于传统频率合成技术的一些性能,高分辨率、极短的频率切换时间、相位噪声低、便于集成等,逐步成为现代频率合成技术中的佼佼者。

目前,DDS的设计大多是应用HDL(Hardware Description Language)对其进行逻辑描述。整个设计可以很容易地实现参数改变和设计移植,给设计者带来很大的方便。Verilog HDL就是其中一种标准化的硬件描述语言,它不仅可以进行功能描述,还可以对仿真测试矢量进行设计。Altera公司开发的QuartusⅡ设计软件,提供了Verilog HDL的设计界面以及编译平台,并且该公司还集成了可供程序下载的FPGA器件CYCLONEⅡ系列芯片,这样大大缩短了DDS的设计周期。

1 DDS的设计原理

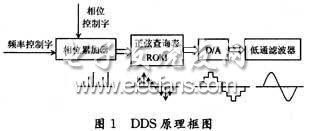

DDS的原理图如图1所示。DDS实现频率合成主要是通过查表的方式进行的。

正弦查询表是一个只读存储器(ROM),以相位为地址,存有1个或多个按0°~360°相位划分幅值的正弦波幅度信息。相位累加器对频率控制字进行累加运算,若需要还可以加入相位控制字,得到的结果作为正弦波查询表的地址。正弦查询表的输出为数字化正弦幅度值,通过D/A转换器转化为近似正弦波的阶梯波,再通过低通滤波器滤除高频成分和噪声最终得到一个纯正度很高的正弦波。

1.1 建模

如图2所示正弦波y=sin(2πx),若以f量化的量化频率对其幅度值进行量化,一个周期可以得到M=f量化个幅度值。将这些幅度值按顺序存入到ROM。相位累加器在参考时钟的驱动下,每来1个脉冲,输出就会增加1个步长相位增量X,输出数据作为地址送入ROM中,读出对应的幅度值形成相应的波形。

1.2 参数设定

DDS输出信号频率:

其中,X为频率累加器设定值;N为相位累加器位数;fc为参考时钟频率。

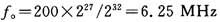

例如,假定基准时钟为200 MHz,累加器的位数为32,频率控制字X为:

0x08000000H,即为227,则:

再设定频率控制字X为0x80000000H,即为231,则:

可见,理论上通过设定DDS相位累加器位数N、频率控制字X和基准时钟fc的值,就可以得到任一频率的输出。

频率分辨率为:fres=fc/2N,由参考时钟和累加器的位数决定,当参考时钟的频率越高,相位累加器的位数越高,所得到的频率分辨率就越高。

1.3 方案的选择

在利用FPGA制作DDS时,相位累加器是决定DDS性能的一个关键部分。一方面可以利用进位链来实现快速、高效的电路结构,同时长的进位链会减少其他逻辑的布线资源,限制整个系统速度的提高;另一方面可以利用流水线技术提高工作频率,但系统频率转换速度会相对降低。在选择累加器实现方案时需要综合考虑。

正弦波查询表ROM也是制作的重点。在FPGA中ROM表的尺寸随着地址位数或数据位数的增加呈指数递增,如何在满足性能的前提下节省资源开销。一方面通过相位累加器的输出截断方式,例如从32位的相位累加器结果中提取高16位作为ROM的查询地址,由此而产生的误差会对频谱纯度有影响,但是对波形的精度的影响是可以忽略的;另一方面可以根据信号周期对称性来压缩ROM的尺寸,这时系统硬件设计复杂度会有所增加。因此,需要选取合适的参数和ROM压缩技术,在满足系统性能的前提下使得系统尽量优化。

2 Verilog HDL实现DDS模块

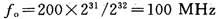

2.1 相位累加器

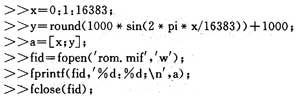

上述为相位累加器的Verilog HDL功能实现,其中数据宽度为32位。同时利用QuartusⅡ进行波形仿真见图3。对应的模块符号见图4。

2.2 ROM正弦查询表

根据DDS的原理,将正弦波形的量化数据存储于波形查询表ROM中,即可完成正弦波发生的功能。Altera公司提供了LPM ROM(ROM兆函数),这里只需借助Matlab生成.mif文件,并加载到LPM ROM中即可得到所需的正弦查询表ROM。

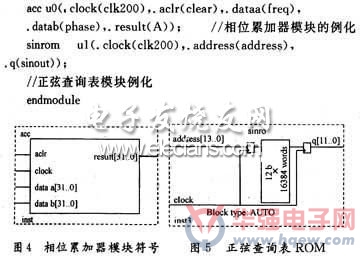

在Matlab中,运行下面的语句可以得到储存正弦波数字幅度值的.mif文件。例如产生214×12 b的正弦波0~27π幅度值,语句如下:

由此而生成的rom.mif文件内容是正弦波0~2π数字幅度值,但是格式不符合.mif。文件的格式,需要对其进行修改。.mif文件的格式如下:

这样通过例化LPM ROM得到了正弦波查询表ROM的模块,地址宽度为14位,输出数据为12位。模块符号见图5。

2.3 DDS顶层模块的实现

上述代码为DDS模块的Verilog HDL顶层文件。对应的模块图见图6。

若需要利用NIOSⅡ对其进行控制,需要并将DDS模块加载到NIOSⅡ的系统中。例如,通过NIOSⅡ为DDS模块的频率控制字freq和相位控制字phase置数。此时DDS的代码应改为:

模块的输入端口添加了写信号iwr、地址信号addr和与NIOSⅡ同步的时钟信号iclk,这样是为了将DDS模块连接到Avalon总线上,利用总线和NIOSⅡ进行通信。加载到NIOSⅡ系统之前,需要将该模块进行仿真和调试。仿真结果如图7所示。

结论:

对于整个模块的驱动时钟,若时钟源器件的频率不符合实际需要,需要再设计一个倍(分)频器将其倍频或是分频。例如现有时钟源为50 MHz,可以使用FPGA中的PLL(锁相环)实现4倍频得到200 MHz。