引言

浮点运算" title="浮点运算">浮点运算作为数字信号处理中最常见的运算之一,各大EDA软件都带有免费的浮点运算IP核。通过对IP核的生成和例化来实现浮点运算,把FPGA" title="FPGA">FPGA设计者从繁重的代码编写中解脱了出来,同时可以对IP核进行功能剪裁以避免对FPGA逻辑资源的浪费,实现最优设计。但对浮点数的获取却关注很少。在浮点运算中,单精度" title="单精度">单精度浮点以其极强的通用性得到了最广泛的应用。本文将目光集中在单精度浮点数的获取上,为浮点IP核提供数据源。在数据的传输上,ASCII码是经常采用的一种形式,本文以串口接收到的ASCII码所表示的实数为例,采用流水处理方式高速地将实数转换为单精度浮点数。

1 实数转换为单精度浮点数的原理

1.1 单精度浮点数格式

浮点数的表示遵循IEEE 754标准,它由3部分组成:符号位(sign)、阶码(exponent)和尾数(fraction)。IEEE 754标准规定的单精度浮点数格式占用32位,包含:1位符号位s、8位带偏移量的指数e[30:23]和23位尾数f[22:0],如图1。单精度的指数使用正偏值形式表示,指数值的大小从1~254(0和255是特殊值)。采用该种形式表示是为了有利于比较大小,浮点小数在计算时,指数值减去偏正值即是实际的指数大小。其中偏移值(bias)为127,尾数有1位隐藏位。

单精度浮点数包含以下几种情况:

(1)规格化数:0

(2)(+0,-0):如果e=0且f=0,则V=(-1)s×0;

(3)非规格化数:e=0但f≠0则V为非规格化数;

(4)(+∞,-∞):e=255,且f=0,则V=(-1)s×∞;

(5)NaN(不是一个数):e=255,且f≠0,则V=NaN。

1.2 转换原理

例如有一个实数为6.91,首先将其转换为二进制形式表示:110.1110100011110101110000101000。再将其规范化为如下:

6.91=1.101110100011110101110000101000×22则可以得到基本原型:

s:0;

e:2+127(十进制)=129(十进制)=10000001(二进制);

f:101110100011110101110000101000(注:小数部分取28位,且小数点前面的1不要)。

小数部分取28位的目的在于更为准确地表示实数,后五位用于舍入处理。在IEEE 754标准中,舍入处理提供了4种可选方法:就近舍入、朝0舍入、朝+∞舍入和朝-∞舍入,本文采用就近舍入原则。就近舍入的实质就是通常所说的“四舍五入”。例如:尾数超过规定的23位的多余数字是10010,多余位的值超过规定的最低有效值的一半。故最低有效位应增1,若多余的5位是01111则简单地截尾即可,对多余的5位100 00这种特殊情况:若最低有效位现为0,则截尾;若最低有效位现1,则向上进一位使其变为0。所以,此例中要将最后5位作舍弃处理。得到的结果为:0 100000011011101000111101011100001。组合后等于0100 0000 1101 1101 0001 1110 1011 1000等于40DDIEB8。至此在原理上完成一个实数到单精度浮点数的转换。

2 在FPGA中实现实数到单精度浮点数转换的流程

2.1 转换流程

在实际工程应用中,所处理的数据都有一个或大或小的范围,在这个范围内将实数转换为单精度浮点数会节约芯片资源和降低功耗。故选择在-9 999.999 9~9 999.999 9的范围内完成实数到单精度浮点数的转换,如图2所示。考虑到实际,数值在很多情况下是通过串口获取的,并表现为ASCII形式。故本文中所提到的实数皆为ASCII表示。

转换过程采用流水线操作,用计数器控制转换进程。ASCII码转换为单精度浮点的方法如下:

(1)将8位ASCII码所代表的数字字符转为十进制数字(由于硬件电路对数字的表示只有0和1的组合,所以将实数的整数和小数分开表示);

(2)利用程序包里的数据类型转换函数将十进制数转换为二进制数,但小数部分的转换需要单独实现;

(3)对二进制表示的实数进行规格化;

(4)根据符号位ASCII码值确定符号位s,根据规格化移动的位数确定阶码e,将规格化中的小数部分f保留28位;

(5)根据就近舍入原则对保留的28位小数部分的后5位进行判断和舍入。2.2 关键代码解析

在FPGA的硬件描述语言中将整数的十进制转换为二进制比较简单,可以调用ISE软件自带的程序包中的转换函数来实现,但如何将小数部分转换为二进制是能否顺利完成从实数到单精度浮点数转换的关键。考虑到要对小数部分进行舍入运算,所以将小数部分转换28位的二进制。要用28位二进制表示小数部分,需利用VHDL语言中变量(variable)被赋值时立即生效的特性,结合FOR循环来实现。部分关键代码如下:

代码中frac_part是小数部分的十进制表示(因为integer类型只能表示整数,所以将小数部分扩大了10 000倍,但不影响结果的正确性),frac_28是小数部分的二进制表示。信号frac_28(27)的权值是2-1,依次以1/2倍率递减,frac_28(0)的权值是2-28。此进程由frac_part发生变化来启动,完成转换的时间是瞬时,也可以认为是一个时钟周期。

3 仿真结果及分析

首先用ModelSim进行功能仿真,其结果如图3所示。输入的实数为125.763,输出结果经Matlab逆向求值同输入值进行比较,验证了转换结果的正确性。一个数的正确转换并不能说明问题,下面将验证此转换方法的可行性。

选取具有代表性的实数对转换方法的性能进行验证。主要验证两个方面:

(1)是否在预定域内具有全覆盖性;

(2)是否能对此域中的最小值进行有效表示。

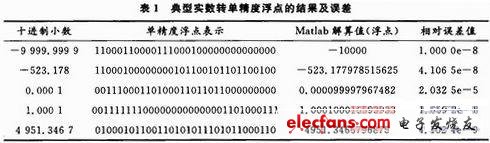

结果如表1所示。

根据转换原理,最小值所转换的误差最大,但最大值的转换误差不一定最小(因为存在舍入)。这个最大的转换误差在10-5量级,当待转换实数的绝对值大于整数1时,转换的误差将小于10-5量级,可达10-9量级。这样的转换误差可以满足大多数浮点运算环境下的精度需要。实验验证了此转换方法的有效性和“全覆盖性”。

在完成仿真测试后,将程序进行综合,布局布线,最后生成位流文件下载到FPGA芯片中进行验证。在实际的芯片中将转换结果和已仿真得到的结果进行比较,并输出指示信号。从实际的电路输出结果看,和仿真结果完全一致,证明了此方法在实际芯片中可行性。因为采用的是流水线操作,所以仿真所用的周期数和实际周期数是一致的。该实验在50 MHz的时钟下用时6个周期(即0.12μs)完成转换操作。而在最常用的串口传输波特率9 600 b/s下,传送1个码元的时间为10-1ms量级。从而可以得出:完成从ASCII码所表示的实数(-9 999.999 9~+9 999.999 9)到单精度浮点的转换所用的时间将在10-1μs量级以下,具有较高的实时性。

4 结语

本文的实现向单精度浮点的转换占用1 161个slice资源,在FPGA发展到今天,FPGA的容量和资源都有了很大提高的情况下,这样的资源占用量在大多数应用中是可以承受的。本文的设计可以很容易地根据实际实数的范围进行调整,并且可以推广到其他浮点格式,可有效地为浮点IP核提供快速且具有高精度的数据源。