视频字符叠加技术的发展及四种实现方案

2009-07-22

作者:孙泓波 顾 红 苏为民

摘 要: 分析了视频字符叠加的作用和发展现状,介绍基于中小规模集成电路、FPGA、单片机和专用芯片的四种实现方案,并对它们各自的特点简要地作了分析和比较。

关键词: 视频字符叠加 单片机 现场可编程门阵列(FPGA)

视频字符及时间叠加器是在视频信号中混入字符或时间信号,从而在屏幕的特定位置上与图像信号同时进行显示的设备。这项技术是应用电视技术中的一个重要领域,在应用电视系统中发挥着重要的作用。从视频字符及时间叠加器的工作方式及本身电路的构成来看,已经历了三个不同的发展阶段[1][2]。

第一阶段是“图解显示控制”即GDC阶段。它是利用中小规模数字集成电路来实现各部分所要求的严格的时序关系,并将形成的字符信号与视频信号在预定的时间关系上混合并显示在屏幕上。在这种方式中,字符的产生有两种办法:

·专用字符发生器:它是一种专用的ROM,常用的有MK36000、MCM6670P、8678、MN1217A等。它们将字符或数字以点阵的方式存入存储器中,在外加恰当地址后便能输出相应的数据信号。这种方式中一旦选定了某种器件,所显示的字符也就确定了,缺乏灵活性,且不能显示图形,通常称此为“文本方式”。

·“图形方式”:在这种方式中,是用EPROM来存储字符或图形的点阵数据,其点阵形式由设计者自己决定,具有更大的灵活性。

第二阶段是用CRT控制器这类专用集成电路的阶段。常用的有8350、8275、MC6845等。它将“图解显示控制方式”中的中小规模集成器件构成的电路集成化。字符(或图形)等以点阵方式存储在外围的ROM或RAM中。它使电路大为简化,因而使用较为方便。

第三阶段是单片“屏幕显示”器件阶段:因为在与电视有关的产品上,并不需要显示很多的字符或图形,因此将以上CRT控制器中的外部存储器与其集成在一起而形成所谓单片屏幕显示器件。这类器件主要是为家用电视这类产品而设计的,并得到了广泛的应用。

考虑到实际使用中用户所需的功能和指标的多样性,我们先后开发了四种典型的实现方案,每种方案各有特点。本文将其分别作简要介绍,以供大家参考。

1 通用中小规模集成电路实现方案

本方案属上面的“图解显示控制”型,全部采用逻辑门、计数器、移位寄存器等通用中小规模集成电路实现单路视频字符及时间叠加。其基本工作原理如下:CPU从ROM字库中取出要显示字符的点阵数据,根据所设定的在屏幕上的显示位置,送到显示RAM的对应位置中去;然后由计数电路对显示RAM进行扫描,将字符点阵信号并行读出;最后经过并串变换电路转化为串行码输出;再与视频图象信号叠加后送监视器屏幕显示。限于篇幅,这里对整体电路结构不作过多描述,只对其中我们设计中的几点考虑作一介绍。

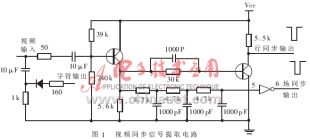

一是视频同步信号提取电路。现在市场上已有不少可实现行、场同步信号分离的专用集成电路,如LM1881等,但成本较高。我们使用分立模拟元件设计了该电路,性能十分稳定可靠,同时大大降低了成本。原理图如图1所示。

关于字符点阵数据在显示RAM中的存放,一般的作法是一种称之为“屏幕存储映像”的方式,其特点是屏幕上每一个象素点都与一位RAM存储单元对应,要对屏幕上字符的显示进行编辑十分简单。但这种方式占用RAM单元较多,需要大容量RAM。我们考虑到一般情况下要在屏幕上显示的字符较少(大多为一行标题、一行时间),屏幕上的大部分地方都是空白的。所以我们只在显示RAM中生成屏幕上两行字符的映像,字符在屏幕上显示的行位置取决于其在RAM区的存储位置,而列位置则由单片机单独发出控制脉冲来控制,这样就大大节省了显示RAM的存储单元。我们称之为“行存储映像”。以上两点可供大家借鉴。

2 基于FPGA的多路实现方案

上面介绍的方案要实现单路字符叠加需用中小规模集成电路十余片,显然要实现多路显示过于复杂,可靠性差。现在随着大规模可编程逻辑器件的普及,其价格也在不断降低。我们就有可能在共用一片CPU、字库ROM和实时时钟的前提下,利用FPGA集成若干路独立的显示RAM计数扫描电路,实现多路时间字符叠加。

多路显示中要求每一路有独立的显示RAM区,最简单的办法是设置多片RAM,但是这样大大增加了电路的复杂性,成本也比较高。我们也可以采用一片大容量的RAM,在其中分别划出四个区域作为四个屏幕的显示RAM。但一片RAM不可能同时输出四路的字符点阵数据,也就是说必须解决RAM的时分复用问题,才能做到多路的同时显示。这里简要介绍一下我们的实现方案(以四路为例)。设字符数据串行输出移位时钟为5MHz,则移位寄存器的置数时钟应为5MHz的8分频,即625kHz。要实现四路连续显示,就应以625kHz的4倍频——2.5MHz的频率分别从显示RAM中的各个存储区域中取出字符点阵数据,经过锁存置入四个输出移位寄存器。这种方法必须使RAM的地址具有各路计数扫描控制下的快速跳转能力,这就要求采用一个大规模的多路开关(如果RAM用62256的话就需15路四选一开关)来实现RAM地址线的切换。以上方案的原理框图如图2。我们采用ALTERA公司的FLEX10K10(1万门FPGA)实现了四路时间字符叠加,性能十分稳定。

3 基于AT90S1200单片机的实现方案

以上两种方案都是用硬件电路实现对显示RAM的计数扫描和点阵数据的移位输出,实际上,我们完全可以利用软件实现这样的功能。如果要用软件实现字符点阵数据的输出,其速度必须满足以下两个条件:一是能够以5MHz的频率将数据串行输出;二是在视频信号行场消隐期内要完成字符数据的读取和与主控CPU的通讯等操作。常用的51系列单片机外接12MHz时钟时一条单周期指令的执行时间为1μs,显然无法满足上面的要求。因此我们选用ATMEL公司新推出的AT90S1200型单片机。其内部有1K的FLASH程序存储器和64字节E2PROM数据存储器,内置有模拟比较器和看门狗,通过SPI口可以串行下载程序而不必通过专用的编程器。更重要的是,它是一种RISC精简指令集单片机,其大部分指令为单周期指令。外接16MHz时钟时每条指令仅需0.06~0.12μs,完全可以满足视频字符叠加数据串行输出的要求。

当然,采用单片机软件实现字符叠加时也有许多具体的问题要考虑。AT90S1200单片机的指令执行速度完全能够满足要求,但是它内部没有大容量的RAM存储器,无法实现前面提到的“屏幕存储映像”或“行存储映像”的内置化,也不易外接存储器,只能以串行通讯的方式由外部主控机发给。为了保证显示的连续性,通讯只能在视频信号消隐期内完成(当然还要完成其他必要的操作)。要在消隐期内完成大量字符点阵数据的传输显然是不可能的。幸运的是,实际使用中监视器上显示的汉字标题信息一般是不变的,只有以数字表示的时间信息是每秒钟变化。针对这种情况,我们利用AT90S1200单片机内部的可以按字节寻址的64字节E2PROM来存储0~9十个数字以及“:”、“—”等用于时间显示的字符点阵,还有其它的诸如显示位置等不经常修改的变量。片内1K字节FLASH不能按字节寻址,用作程序存储器,要显示的汉字点阵数据包含在程序中。这样在使用时主控CPU只需将当前时间值传给AT90S1200,大大减少了通讯的数据量,使之可以在场消隐期内完成,保证时间的连续显示。当显示的汉字标题要更改时,由主控CPU从外部字库ROM中取出新的点阵数据,将其拼接在AT90S1200程序代码的对应位置,再通过SPI口对AT90S1200进行串行编程,编程完毕后恢复正常显示。我们采用ATMEL 89C51单片机作主控机,6片AT90S1200单片机作显示执行机,行场同步信号分别利用AT90S1200模拟比较器和I/O口输入。由于AT90S1200没有标准的UART串口,我们利用其I/O管脚自定义了一种串行通讯协议,从而实现了六路时间字符叠加。这种方案电路非常简单,并且多路实现时成本很低,是一种值得推广的方法。

4 基于μPD6453字符叠加专用芯片的实现方案

μPD6453是NEC公司推出的专用视频字符叠加芯片,它最多可以同时显示12行24列12×18点阵的字符。芯片内部固化了240个日文、英文字母和数字等字符的字模,还有16个字符的空RAM区供用户添入自定义字符。μPD6453的显示编辑功能非常强大,它的控制方式也非常灵活简单。它共有5条单字节指令、6条双字节指令和1条三字节指令,所有的指令均串行输入μPD6453,使用非常方便。限于篇幅,有关μPD6453的性能不再赘述,这里只简要介绍一些我们设计过程中的经验。

首先,对于我国的用户来说,大量的汉字都没有固化在μPD6453芯片内部,需要将其先写入片内16个字符的空RAM区,再发出指令让其显示出来。μPD6453内部的字模(包括16个字符的空RAM区)均为12×18点阵,而12×18点阵的汉字字库很难找到。我们考虑了两种方案:一是利用12×12点阵字库数据直接写入片内RAM区,这样两行汉字之间会有一些间隔,但多数情况下只需显示一行汉字,在显示精度要求不高的情况下可以采用这种方法。二是利用16×16点阵或更高的点阵字库写入,使几个字符拼成一个汉字,这样显示精度很高,但软件处理较为复杂。在实际使用中我们提取出UCDOS中的12×12点阵一级字库,将其固化在128K ROM 27010中,利用键盘控制可以将任意字符送到屏幕上显示。第二,μPD6453显示字符的大小有单倍、双倍、三倍和四倍模式,但有时单倍显示的字符仍然嫌大。我们注意到μPD6453外接的电感电容振荡电路对显示字符的横向长度影响很大,但芯片手册上并未给出具体的参数值。经过反复试验,我们认为电感取15μH,电容取56pF比较合适。若稍微调整电感值,则可改变显示字符横向尺寸,使用时可根据自己的需要选用。

以上介绍了四种视频时间字符叠加的方案和我们在设计中的一些经验。相比较而言,第一种中小规模集成电路的方案电路较为复杂,只适用于单路设计。随着专用芯片和单片机技术的发展,这种实现方案应逐渐被淘汰。第二种基于FPGA的实现方案在原理上与第一种类似,只是利用可编程逻辑器件集成了大量中小规模集成电路,电路规模简化了不少,实现也较为方便,但还受到价格的制约。第三种基于单片机的实现方案利用软件实现了硬件扫描电路的功能,并且十分灵活,成本也很低。它的缺点是只适用于显示字符相对较少的场合,若显示字符很多软件就过于复杂,很难保证连续显示。第四种基于专用字符叠加芯片的方案功能很强,适用于显示字符较多的场合,并且价格适中。我们认为在要求显示字符较少的情况下(例如仅显示一行标题、一行时间),可以选用第三种基于单片机的实现方案;若显示的字符较多且位置复杂,第四种方案较为合适。这四种方案我们都实现了产品化的批量生产,技术上是成熟的,性能也都十分稳定可靠,读者可以根据具体情况选用。

参考文献

1 傅万钧,张维力.应用电视技术.北京:国防工业出版社,1996

2 中国广播电视设备工业协会应用电视专业协会.应用电视——设备原理与工程实践.北京:电子工业出版社,1992